低开销、高带宽的可重配置互连装置和方法

1.优先权要求

2.本技术要求于2019年9月19日递交的、并且题为“低开销、高带宽的可重配置互连装置和方法(low overhead,high bandwidth re-configurable interconnect apparatus and method)”的美国专利申请no.16/576,687的优先权,该美国专利申请通过引用以其整体并入本文,用于所有目的。

背景技术:

3.当今,要求单个产品设计在不同的供应电压下操作。例如,同一处理器被设计为在高电压供应(例如,1.2v)和低电压供应(例如,0.5v)下操作。可以根据细分市场(例如,平板设备、膝上型电脑、桌面型电脑,等等)的性能和功率要求来选择和固定供应电压(或电压范围)。例如,桌面型电脑细分市场中的处理器可以在更高的电压下操作,提供更高的频率和处理速度(例如,更高的性能),而平板设备或膝上型电脑细分市场中的同一处理器可以在更低的电压下并以更低的频率和处理速度操作。在大多数情况下,可能要求处理器支持从最低操作电压(vmin)到最高操作电压(vmax)的范围。而且,在操作期间,电压可能会被动态调整(例如,低功率模式、正常模式、极速模式,等等)。

4.对于大型异构平台,低时延、低能量和高带宽的片上网络(network-on-chip,noc)对于在功率包络内维持性能cagr(compound annual growth rate,复合年增长率)是至关重要的。虽然经过精心设计,但noc架构(环线(ring)或网格(mesh)或其他拓扑结构)仍要努力满足对时延、带宽和能量的竞争性需求,往往是牺牲一个来换取另一个。具体而言,noc架构的时延、带宽和能量往往受到长的中继/缓冲线/互连的限制。例如,noc架构的时延、带宽和能量进而又受到连接两个网格站点或环线站点的缓冲互连的限制。例如,缓冲互连构成了由几千条线组成的总线,并且通常在芯片上跨越几毫米,并且经历dvfs(动态电压和频率缩放)以实现功率包络下的高性能。通过精心选择中继器间的距离、缓冲器大小、导线层、导线宽度、导线间距等等来优化缓冲互连。技术缩放和宽操作范围进一步加剧了这一挑战。

附图说明

5.通过以下给出的详细描述并且通过本公开的各种实施例的附图,将更充分理解本公开的实施例,然而,详细描述和附图不应当被理解为将本公开限制到特定实施例,而只是用于说明和理解的目的。

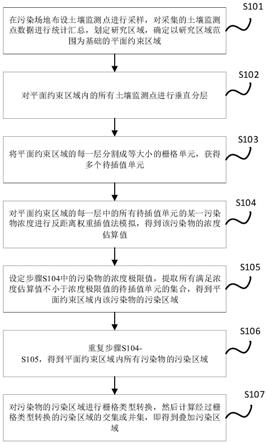

6.图1a图示了高速模式中的可重配置互连。

7.图1b图示了低能量模式中的可重配置互连。

8.图2图示了根据一些实施例的包括具有可重配置互连的3x 3网格的片上网络(noc)。

9.图3图示了基线中继总线互连设计。

10.图4图示了根据一些实施例的三模态可重配置互连。

11.图5图示了根据一些实施例的带宽模式中的三模态可重配置互连。

12.图6图示了根据一些实施例的时延模式中的三模态可重配置互连。

13.图7图示了根据一些实施例的能量模式中的三模态可重配置互连。

14.图8a-图8b图示了根据一些实施例的分别示出带宽模式和时延模式的图线。

15.图9a-图9b图示了根据一些实施例的分别示出带宽模式和时延模式的图线。

16.图10图示了根据一些实施例的具有3x中继线的三模态可重配置互连。

17.图11图示了根据一些实施例的具有三模态可重配置互连的soc或noc。

具体实施方式

18.电阻性互连的功率和性能影响在很大程度上取决于供应电压。因此,在低电压下操作得最好的设计,在高电压下操作效率较低,反之亦然。将一种设计应用于不同的细分市场和功率模式,会提供设计和制造效率,但会损害性能和能量。随着互连电阻随着缩放而增大,这种损害可能会变得更加严重。

19.设计具有电阻性互连的逻辑或处理器的当前解决方案限于两种非最优的方法。在第一种方法中,在给定的性能点(例如,高性能或低功率)下对集成电路(ic)的设计进行优化。在这种情况下,其他性能目标产品在不佳的功率性能下操作将受到很大影响。例如,为在高性能(例如,高频率)下操作而优化的ic设计可能会导致在低电压和频率下操作的产品的不佳的功率效率,因为所消耗的功率将超过以较低性能操作所实际需要的最低值。

20.一些实施例提供了一种低开销的方法和装置,用于将一对缓冲互连链路重配置为在这三种模式之一中操作——第一模式(例如,带宽模式)、第二模式(例如,时延模式)和第三模式(例如,能量模式)。在带宽模式中,该对缓冲互连链路中的每个链路将独特的信号从源携带到目的地。在时延模式中,该对中的两条链路都将同一信号从源携带到目的地,其中该对中的一条链路是“主”链路,另一条被称为“辅助”链路。这一对缓冲互连中的转变的时间对齐减小了主链路的有效电容,从而减小了延迟或时延。在能量模式中,该对中的一条链路,即主链路,单独携带信号,而该对中的另一条链路是空闲的。一侧的空闲邻居减小了主链路的能量消耗。这些互连是网格或环线网络的一部分(例如,在片上网络(noc)中)。在一些实施例中,仲裁器电路(例如,网格站点和环线站点)与主架构控制器(例如,在功率管理单元中)协调工作,以使得缓冲互连链路动态地适应工作负载需要。

21.各种实施例有许多技术效果。例如,可重配置互连允许了对架构时延、带宽和能量进行即时重配置。虽然可以通过动态电压频率缩放来调节延迟和能量,但这种可重配置互连提供了一种强大而可靠的旋钮来调节延迟(例如,时延)、能量和带宽。这种可重配置互连实现了这些优点,而不需要额外的布线或任何新的工艺增强或复杂的定制电路。可重配置互连为潜在芯片设计者提供了统一物理缓冲互连链路设计/优化,因为同一对底层物理链路可以在不同的模式中被控制和操作,以完成一系列的时延、带宽和能量目标。例如,noc/架构互连配置维持了核心间通信(这包括处理器核心到更低级别缓存(lower-level-cache,llc)的通信)、核心与主存储器的通信、核心与i/o的通信,这意味着可重配置互连的更低时延和更高带宽架构为各种工作负载实现了功率性能的明显改善。其他技术效果将从各种实施例和附图中清楚显现。

22.在接下来的描述中,论述了许多细节以提供对本公开的实施例的更透彻说明。然而,本领域技术人员将会清楚,没有这些具体细节也可以实践本公开的实施例。在其他情况

下,以框图形式而不是详细示出公知的结构和设备,以避免模糊本公开的实施例。

23.注意,在实施例的相应附图中,以线条来表示信号。一些线条可能更粗,以指示更多的构成信号路径,和/或在一端或多端具有箭头,以指示主信息流方向。这种指示并不旨在进行限制。更确切地说,这些线条与一个或多个示例性实施例被联合使用以帮助更容易理解电路或逻辑单元。由设计需要或偏好决定的任何所表示的信号可实际上包括可在任一方向上行进并且可利用任何适当类型的信号方案来实现的一个或多个信号。

24.在整个说明书中,以及在权利要求中,术语“连接”的意思是直接连接,例如连接的事物之间的电连接、机械连接或磁连接,没有任何中间设备。术语“耦合”的意思是直接或间接连接,例如连接的事物之间的直接电连接、机械连接或磁连接,或者通过一个或多个无源或有源中间设备的间接连接。

25.术语“电路”或“模块”可以指被布置为与彼此合作来提供期望的功能的一个或多个无源和/或有源组件。术语“信号”可以指至少一个电流信号、电压信号、磁信号、或者数据/时钟信号。“一”、“一个”和“该”的含义包括复数引用。“在

…

中”的含义包括“在

…

中”和“在

…

上”。

26.术语“缩放”一般是指将某个设计(图解和布局)从一种工艺技术转换到另一种工艺技术并随后减小布局面积。术语“缩放”一般也指在同一技术节点内减小布局和器件的大小。术语“缩放”还可以指相对于另一参数(例如,电力供应水平)对信号频率进行的调整(例如,减慢或加速——即分别是缩小或放大)。术语“缩放”也可以指调整到(一个或多个)电路的电力供应电压的幅值(例如,电压缩放)。

27.术语“基本上”、“接近”、“大致”、“近似”和“大约”一般是指在目标值的 /-10%内。除非另有说明,否则,使用序数形容词“第一”、“第二”和“第三”等等来描述共同对象只是表明相似对象的不同实例被引用,而并不旨在暗示这样描述的对象必须在时间上、空间上、排名上或者以任何其他方式处于给定的序列中。

28.要理解,这样使用的术语在适当的情况下是可互换的,从而使得本文描述的发明的实施例例如能够按与本文图示或以其他方式描述的那些不同的其他朝向来操作。

29.对于本公开而言,短语“a和/或b”和“a或b”的意思是(a)、(b)或者(a和b)。对于本公开而言,短语“a、b和/或c”的意思是(a)、(b)、(c)、(a和b)、(a和c)、(b和c)或者(a、b和c)。说明书中和权利要求中的术语“左”、“右”、“前”、“后”、“顶部”、“底部”、“之上”、“下方”等等(如果存在的话)是用于描述性目的的,而并不一定用于描述永久的相对位置。

30.就本发明实施例而言,各种电路、模块和逻辑块中的晶体管可以是隧穿场效应晶体管(tunneling fet,tfet),或者各种实施例的一些晶体管可包括金属氧化物半导体(metal oxide semiconductor,mos)晶体管,其包括漏极、源极、栅极和体端子。晶体管也可包括三栅极和finfet晶体管、栅极全环绕圆柱体晶体管、方形线晶体管、或者矩形带状晶体管、或者像碳纳米管或自旋器件之类的实现晶体管功能的其他器件。mosfet对称源极和漏极端子是相同的端子,并且在这里可被互换使用。另一方面,tfet器件具有非对称源极和漏极端子。本领域技术人员将会明白,在不脱离本公开的范围的情况下,其他晶体管,例如双极结型晶体管—bjt pnp/npn、bicmos、cmos等等,可被用于一些晶体管。

31.随着用于处理器或逻辑的电力供应电压(vdd)增大,缓冲互连更多地受到导线的限制,而不是设备的限制(因为设备延迟随着vdd而减小,而导线延迟却不会)。为了在高vdd

下实现更低的延迟,同时在低vdd下实现更低的功率,可以使用可重配置互连。在典型的可重配置互连中,每个缓冲互连会得到另一个相同的缓冲互连(驱动器和导线)作为“辅助”。可重配置互连在两种模式中操作:高速模式和低能量模式,如图1a-图1b中所示。

32.图1a图示了高速模式中的可重配置互连体系结构100。图1b图示了低能量模式中的可重配置互连体系结构120。体系结构100图示了导线101a、101b、101c和101d;驱动器(反相器)102a、102b、102c和102d;以及接收器(反相器)103a、103b、103c和103d。互联的可重配置部分接收输入“in”,并且提供输出“out”。互连的可重配置部分由驱动器102a和102b、导线101b和101c以及接收器103a和103b组成,其中驱动器102b是三态驱动器(由使能信号控制),并且其中,接收器103b是可由使能信号控制的三态接收器。

33.这里,电容c

ab

是导线101a和101b之间的耦合电容,电容c

bc

是导线101b和101c之间的耦合电容,而电容c

cd

是导线101c和101d之间的耦合电容。在高速模式中,如图1a所示,主互连101b和辅助互连101c中的转变的时间对齐减小了主互连101b和辅助互连101c之间的有效交叉耦合电容,从而减小了从输入in到输出out的延迟和能量。在低能量模式中,如图1b所示,辅助缓冲互连是三态和空闲的,这导致了能量的节省。

34.图1a-图1b的可重配置互连只在布线资源不受约束的场景中有效。另外,辅助路径中的三态反相器102b和103b会消耗硅面积。例如,图1a的高速模式配置通过减小主互连101b的有效导线电容而减小了延迟,因为主互连101b和辅助互连101c中的转变在时间上对齐,因此它们之间的交叉耦合电容c

bc

被减小或消除了。在图1b的低能量模式配置中,辅助互连101c被禁用,从而减小了动态功率。然而,可重配置互连体系结构100/120需要针对辅助导线101c的额外布线轨道。

35.图2图示了根据一些实施例的包括具有可重配置互连的3x3网格的片上网络(noc)体系结构。noc体系结构200包括功率管理单元(power management unit,pmu)201,并且网格网络包括路由器、节点和/或仲裁器202。在这个示例中,示出了3x3网格网络,包括路由器、节点和/或仲裁器202

1,1

至202

3,3

。每个路由器、节点和/或仲裁器具有用于接收模式控制203的接口和与业务互连204耦合的接口(例如,驱动器和接收器)。在一些实施例中,缓冲互连204通常是常规反相器路径,在辅助路径中不需要三态反相器,并且引申开来,也不需要用于三态反相器的控制信号。因此,各种实施例的技术与静态定时分析兼容,并且是随时可使用的。

36.在一些实施例中,缓冲互连的操作模式由主架构控制器(或功率管理单元201)确定,它可以是也控制dvfs的同一单元。在一些实施例中,控制器201将操作模式发送给每一个网格站点或环线站点。这里,网格站点或环线站点是路由器、节点和/或仲裁器202。因此,网格站点和环线站点确定并且驱动信号到一对缓冲互连的输入(取决于操作模式)。例如,基于操作模式,一对缓冲互连被用独特信号(带宽模式)或相同信号(时延模式)适当地驱动,或者辅助不被驱动(能量模式)。在一些实施例中,pmu 201使用操作系统(operating system,os)提示和/或片上功率性能计数器来动态地确定互连架构的操作模式。

37.例如,对于时延很关键的时延关键工作负载,os向pmu 201发出时延模式,pmu 201将仲裁器配置在时延模式中,以减小noc中的延迟,从而满足频率要求。对于时延非关键的工作负载,os使得pmu 201能够执行dvfs,该dvfs减小了供应电压和频率两者以节省能量,并且pmu将仲裁器配置在能量模式中,该模式减小了noc的能量消耗。对于通过dvfs提升操

作频率而无法支持的要求高带宽的工作负载(例如,数据移动、存储器访问,等等),pmu 201可以将仲裁器配置在带宽模式中,该模式利用可用的互连来进行通信。

38.在传统的可重配置互连中,例如图1a-图1b中的那种,缓冲互连的性能-功率调节通常仅限于缓冲器和导线优化。在一些实施例中,网格站点还可以通过控制操作模式来影响缓冲互连的延迟和能量。这为微体系结构师和体系结构师提供了一个调节基本架构参数的旋钮。

39.与其他逻辑控制器相比,主架构控制器(例如,pmu 201)可以通过控制网格站点,并进而控制缓冲互连链路的操作模式,来更好地对带宽或时延需求做出反应。这提供了超出操作vdd和频率(利用dvfs)的一个额外的自由度。

40.图3图示了基线中继总线互连设计300。基线设计300图示了两个可能的网格或环线站点之间的互连的示例。在这个示例中,网格或环线站点是路由器(节点或仲裁器)302

1,1

和302

1,2

。示出了两条信号路径(或业务互连)304。第一信号路径从输入in1开始,在输出out1结束。第二信号路径从输入in2开始,在输出out2结束。每条信号路径是中继总线互连,具有优化的中继器间距离、中继器尺寸、导线层、宽度和导线间空间。在这个示例中,中继器304a被示为反相器(其也可被实现为非反相缓冲器)和导线304b。被动屏蔽被用来减小相邻导线之间的米勒耦合电容。在这个示例中,被动屏蔽是电力供应(vcc)或地(vss)互连。在相反的方向上运行信号也可以减小米勒耦合电容。在这个示例中,信号in1从右向左传播,而信号in2从左向右传播。

41.图4图示了根据一些实施例的三模态可重配置互连400。在这个示例中,示出了2x中继线,它们形成了一组信号路径,这些路径被vcc或vss互连所屏蔽。第一信号路径从输入in1开始,在输出out1结束。第二信号路径从输入in2开始,在输出out2结束。第三信号路径从输入in3开始,在输出out3结束。第四信号路径从输入in4开始,在输出out4结束。第二和第四信号路径将(一个或多个)信号从仲裁器301

1,1

传播到仲裁器302

1,2

,而第一和第三信号路径将(一个或多个)信号从仲裁器301

1,2

传播到仲裁器302

1,1

。虽然本发明实施例图示了仲裁器301

1,1

和仲裁器302

1,2

之间的信号路径,但本发明实施例适用于任何网格或环线站点之间的信号传输。在各种实施例中,仲裁器301

1,1

确定驱动in3和in4的输入信号,从而,设置操作模式——带宽模式、时延模式和能量模式。表格1总结了这些模式。

42.表格1

[0043][0044][0045]

在一些实施例中,控制器(例如,pmu 201或任何其他网络控制器)生成模式信号203。此模式信号203是多比特信号,它指示出两个或更多个互连中的第一互连和第二互连的操作模式。例如,模式信号203设置信号路径in1到out1、in3到out3、in2到out2和in4到

out4的操作模式,其中信号路径in1到out1和in3到out3是第一组两个或更多个互连的一部分,并且其中,信号路径in2到out2和in4到out4是第二组两个或更多个互连的一部分。在各种实施例中,信号路径在特定方向上的传播延迟是相同的(或者基本相同)。例如,信号路径in2到out2和in4到out4具有相同(或者基本相同)的传播延迟,而信号路径in1到out1和in3到out3具有相同(或者基本相同)的传播延迟。

[0046]

操作模式可以是第一模式、第二模式或者第三模式。各种实施例是参考模式信号是2比特信号来描述的,其中第一模式是带宽模式,第二模式是时延模式,并且第三模式是能量模式。然而,实施例并不限于这些模式。仲裁器402(例如,402

1,1

和402

1,2

)可被配置为实现比三种模式更多的模式。在一个这样的实施例中,在仲裁器之间提供更多的信号路径,并且模式控制信号203的比特大小可以大于两个比特。

[0047]

第一仲裁器402

1,2

与控制器201通信地耦合。例如,模式控制203被提供给第一仲裁器402

1,2

,因此实现了通信耦合。在一些实施例中,第一仲裁器402

1,2

将两个或更多个互连中的第一互连(例如,in1到out1和in3到out3)配置为处于第一、第二或第三模式之一中。例如,取决于模式控制信号203的比特值,第一仲裁器402

1,2

将输入in1和in3节点设置为独立的以通过它们各自的信号路径来携带独特的信号,设置为短接以通过它们各自的信号路径来携带相同的信号,或者其中之一被电气开路以使得只有一个信号路径是活跃的。

[0048]

在一些实施例中,第二仲裁器402

1,1

与控制器201通信耦合,就像第一仲裁器402

1,2

与控制器201通信耦合一样。在一些实施例中,第二仲裁器402

1,1

将两个或更多个互连中的第二互连(例如,in2到out2和in4到out4)配置为处于第一、第二或第三模式之一中。例如,取决于模式控制信号203的比特值,第二仲裁器402

1,1

将输入in2和in4节点设置为独立的以通过它们各自的信号路径来携带独特的信号,设置为短接以通过它们各自的信号路径来携带相同的信号,或者其中之一被电气开路以使得只有一个信号路径是活跃的。

[0049]

在各种实施例中,由第一和第二仲裁器设置的操作模式是相同的操作模式。例如,第一仲裁器402

1,2

和第二仲裁器402

1,1

使得信号路径(例如,两个或更多个互连中的第一互连,以及两个或更多个互连中的第二互连)处于带宽模式、时延模式或能量模式中。在一些实施例中,由第一和第二仲裁器设置的操作模式是不同的操作模式。

[0050]

在各种实施例中,两个或更多个互连中的第一互连中的至少一者和两个或更多个互连中的第二互连中的至少一者被电力供应线(vcc)或地线(vss)所屏蔽。在这个示例中,信号路径in1到out1被vcc或vss之一屏蔽,同时信号路径in2到out2被vcc或vss之一屏蔽。

[0051]

在一些实施例中,在第一模式(例如,带宽模式)中,第一仲裁器402

1,2

和第二仲裁器402

1,1

使得在两个或更多个互连中的第一互连和第二互连上传播单独的信号。例如,每个信号路径携带独特的信号。在这个示例中,可以在带宽模式中在两个仲裁器之间传播四个不同的信号。

[0052]

在一些实施例中,在第二模式(例如,时延模式)中,第一仲裁器402

1,2

和第二仲裁器402

1,1

使得在两个或更多个互连中的第一互连上传播第一相同信号,并且在两个或更多个互连中的第二互连上传播第二相同信号。例如,in1和in3是从仲裁器402

1,2

传播到仲裁器402

1,1

的相同信号,in2和in4是从仲裁器402

1,1

传播到仲裁器402

1,2

的相同信号。

[0053]

在一些实施例中,在第三模式(例如,能量模式)中,第一仲裁器402

1,2

和第二仲裁器402

1,1

使得交替地在两个或更多个互连中的第一互连上并交替地在两个或更多个互连中

的第二互连上传播信号。例如,信号路径in1到out1被使能,但信号路径in3到out3被禁用。同样地,信号路径in2到out2被使能,而信号路径in4到out4被禁用。

[0054]

在各种实施例中,仲裁器可以使用任何适当的逻辑来实现,例如多路复用器、传输门、三态缓冲器或反相器、与非门、或非门等等,它们可由模式控制203来控制,该模式控制203根据模式控制203的比特值在互连304上路由业务。

[0055]

图5图示了根据一些实施例的带宽模式中的三模态可重配置互连500。在这种配置中,相对于单个信号路径,实现了高带宽。每条物理链路携带独特的逻辑信号。在这个示例中,4条物理导线被打包在同一布线资源内。这里,仲裁器301

1,1

和仲裁器302

1,2

被配置(如信号路由器502

1,1

和502

1,2

所示)为使得输入in1、in2、in3和in4携带独特的信号。

[0056]

图6图示了根据一些实施例的时延模式中的三模态可重配置互连600。邻居(例如,信号路径in3)被重利用为信号路径in1的辅助路径。这里,仲裁器301

1,1

和仲裁器302

1,2

被配置(如信号路由器602

1,1

和602

1,2

所示)为使得in2和in4携带相同的信号,并且in1和in3携带相同的信号。通过使用并行的信号路径,减小了信号路径之间的交叉耦合电容。辅助路径(in3)和主路径(in1)中的信号转变在时间上对齐,从而有效地减小(并且在最佳情况下消除)了in1和in3之间的耦合电容。驱动器大小和导线布局是相同的(或基本相同的)(对于in1和in3),以使得能够实现紧密匹配。虽然如此,如果在in1和in3之间的信号转变中存在时间上的不匹配,则延迟效益会完整下降。

[0057]

图7图示了根据一些实施例的能量模式中的三模态可重配置互连700。这里,仲裁器301

1,1

和仲裁器302

1,2

被配置(如信号路由器702

1,1

和702

1,2

所示)为使能交替的信号路径。因此,携带信号的信号路径被非切换信号路径所屏蔽。因为切换的信号路径更少了,所以这种配置不仅可以使能低能量模式,而且它还允许屏蔽重要的信号(例如,硬复位信号),使其免受噪音影响。在这种情况下,邻居信号路径(in3)不切换,而仅仅是信号路径in1切换,从而在工作负载不要求低时延或高带宽时节省能量。

[0058]

图8a-图8b图示了根据一些实施例的分别示出带宽模式和时延模式的图线800和820。图线800比较了典型互连801、时延模式中的可重配置互连802以及带宽模式中的可重配置互连803的峰值带宽与时延。这些图线示出了时延关键服务器网格链路的三模态可重配置互连的性能。这里,每条曲线中的四个点是不同的vdd点:0.65v、0.75v、0.9v和1.1v。图线800示出,在带宽模式中,我们可以将峰值带宽增大多达33%,代价是比801多46%的能量。图线820比较了典型互连821、时延模式中的可重配置互连822以及带宽模式中的可重配置互连823的能量与时延。图线820示出,在时延模式中,链路时延可被减小14%,代价是能量增大68%。注意,在这个示例中,如果两者都不是想要的,那么可重配置互连可以在能量模式中,时延增加不到5%。

[0059]

图9a-图9b图示了根据一些实施例的分别示出带宽模式和时延模式的图线900和920。图线900比较了典型互连901、时延模式中的可重配置互连902以及带宽模式中的可重配置互连903的峰值带宽与时延。这些图线示出了时延关键服务器网格链路的三模态可重配置互连的性能。例如,图线900和920示出,即使在固定的能量预算下也能获得效益,如曲线中的不同点所示,它们是不同的vdd点:0.65v、0.75v、0.9v和1.1v。峰值带宽与时延图线900示出,在带宽模式中,即使在能量约束下(例如,链路901消耗最大能量),带宽也会增大27%。图线920比较了典型互连921、时延模式中的可重配置互连922以及带宽模式中的可重

配置互连923的能量与时延。图线920示出,在时延模式中,链路时延可被减小5%,并且能量没有增大。注意,更复杂的(全对全(all-to-all))仲裁器也可以动态地支持2x和3x三模态可重配置互连。这里,全对全仲裁器指的是可以与所有其他仲裁器直接通信的仲裁器。

[0060]

图10图示了根据一些实施例的具有3x中继线的三模态可重配置互连1000。在本发明的替换实施例中,可以将三个缓冲互连配置成三种操作模式——带宽、时延和能量,而不是动态地重配置一对缓冲互连。类似的方案可用于配置“n”个缓冲互连,其中“n”大于3。在一些实施例中,仲裁器1002

1,1

和1002

1,2

确定驱动in3、in4、in5和in4的输入信号,从而,设置操作模式——带宽模式、时延模式和能量模式。表格2总结了这些模式。对于某些缓冲互连配置,3x三模态可重配置互连可能实现的时延减小、能量减小和带宽增大可能高于基线。

[0061]

表格2

[0062][0063]

图11图示了根据一些实施例的具有三模态可重配置互连的soc或noc 2400。在一些实施例中,设备2400表示适当的计算设备,例如计算平板、移动电话或智能电话、膝上型电脑、桌面型电脑、物联网(internet-of-things,iot)设备、服务器、可穿戴设备、机顶盒、具备无线能力的电子阅读器,等等。将会理解,某些组件被概括地示出,并且在设备2400中没有示出这种设备的所有组件。图11的任何块可具有各种实施例的三模态可重配置互连。

[0064]

在一示例中,设备2400包括soc(片上系统)2401。soc 2401的示例边界在图15中利用虚线图示,其中一些示例组件被图示为包括在soc2401内——然而,soc 2401可包括设备2400的任何适当组件。

[0065]

在一些实施例中,设备2400包括处理器2404。处理器2404可包括一个或多个物理设备,例如微处理器、应用处理器、微控制器、可编程逻辑器件、处理核心、或者其他处理装置。处理器2404执行的处理操作包括对其上执行应用和/或设备功能的操作平台或操作系统的执行。处理操作包括关于与人类用户或与其他设备的i/o(输入/输出)的操作、关于功率管理的操作、关于将计算设备2400连接到另一设备的操作,等等。处理操作还可包括与音频i/o和/或显示i/o有关的操作。

[0066]

在一些实施例中,处理器2404包括多个处理核心(也称为核心)2408a、2408b、2408c。虽然在图15中只图示了三个核心2408a、2408b、2408c,但处理器2404可包括任何其他适当数目的处理核心,例如数十个或者甚至数百个处理核心。处理器核心2408a、2408b、2408c可被实现在单个集成电路(ic)芯片上。此外,芯片可包括一个或多个共享的和/或私有的缓存、总线或互连、图形和/或存储器控制器,或者其他组件。

[0067]

在一些实施例中,处理器2404包括缓存2406。在一示例中,缓存2406的一些部分可专用于个体核心2408(例如,缓存2406的第一部分专用于核心2408a,缓存2406的第二部分专用于核心2408b,等等依此类推)。在一示例中,缓存2406的一个或多个部分可以在两个或

更多个核心2408之间共享。缓存2406可被分割成不同的级别,例如第1级(l1)缓存、第2级(l2)缓存、第3级(l3)缓存,等等。

[0068]

在一些实施例中,处理器核心2404可包括取得单元来取得指令(包括带有条件分支的指令)以供核心2404执行。可以从诸如存储器2430之类的任何存储设备取得指令。处理器核心2404也可包括解码单元来对取得的指令进行解码。例如,解码单元可以将取得的指令解码成多个微操作。处理器核心2404可包括调度单元来执行与存储经解码的指令相关联的各种操作。例如,调度单元可保存来自解码单元的数据,直到指令准备好调谴为止,例如,直到解码的指令的所有源值变得可用为止。在一个实施例中,调度单元可调度和/或发出(或调谴)解码的指令到执行单元以供执行。

[0069]

执行单元可在调谴的指令被解码(例如,被解码单元解码)和派谴(例如,被调度单元调谴)之后执行这些指令。在一实施例中,执行单元可包括多于一个执行单元(例如,成像计算单元、图形计算单元、通用计算单元,等等)。执行单元也可以执行各种算术操作,例如加法、减法、乘法和/或除法,并且可包括一个或多个算术逻辑单元(arithmetic logic unit,alu)。在一实施例中,协处理器(未示出)可联合执行单元来执行各种算术操作。

[0070]

另外,执行单元可无序地执行指令。因此,处理器核心2404在一个实施例中可以是无序处理器核心。处理器核心2404也可包括引退单元。引退单元可以在执行的指令被提交之后引退这些指令。在一实施例中,执行的指令的引退可导致从指令的执行中提交处理器状态、指令所使用的物理寄存器被解除分配,等等。处理器核心2404也可以包括总线单元,以使得处理器核心2404的组件和其他组件之间能够经由一条或多条总线进行通信。处理器核心2404也可以包括一个或多个寄存器来存储被核心2404的各种组件访问的数据(例如,与指派的应用优先级和/或子系统状态(模式)关联有关的值)。

[0071]

在一些实施例中,设备2400包括连通性电路2431。例如,连通性电路2431包括硬件设备(例如,无线和/或有线连接器和通信硬件)和/或软件组件(例如,驱动器、协议栈),来例如使得设备2400能够与外部设备通信。设备2400可以与诸如其他计算设备、无线接入点或基站等等之类的外部设备相分离。

[0072]

在一示例中,连通性电路2431可以包括多种不同类型的连通性。概括来说,连通性电路2431可以包括蜂窝连通性电路、无线连通性电路,等等。连通性电路2431的蜂窝连通性电路一般指的是由无线运营商提供的蜂窝网络连通性,例如经由以下所列项来提供的蜂窝网络连通性:gsm(global system for mobile communications,全球移动通信系统)或者变体或衍生物,cdma(code division multiple access,码分多址接入)或者变体或衍生物,tdm(time division multiplexing,时分复用)或者变体或衍生物,第3代合作伙伴计划(3rd generation partnership project,3gpp)通用移动电信系统(universal mobile telecommunications systems,umts)系统或者变体或衍生物,3gpp长期演进(long-term evolution,lte)系统或者变体或衍生物,3gpp lte高级版(lte-advanced,lte-a)系统或者变体或衍生物,第五代(5g)无线系统或者变体或衍生物,5g移动网络系统或者变体或衍生物,5g新无线电(new radio,nr)系统或者变体或衍生物,或者其他蜂窝服务标准。连通性电路2431的无线连通性电路(或无线接口)指的是非蜂窝的无线连通性,并且可包括个人区域网(例如蓝牙、近场,等等)、局域网(例如wi-fi)和/或广域网(例如wimax),和/或其他无线通信。在一示例中,连通性电路2431可包括网络接口,例如有线或无线接口,例如,使得系统

实施例可被包含到无线设备中,例如,蜂窝电话或个人数字助理。

[0073]

在一些实施例中,设备2400包括控制中枢2432,该控制中枢表示关于与一个或多个i/o设备的交互的硬件设备和/或软件组件。例如,处理器2404可以经由控制中枢2432与显示器2422、一个或多个外围设备2424、存储设备2428、一个或多个其他外部设备2429等等中的一个或多个进行通信。控制中枢2432可以是芯片组、平台控制中枢(platform control hub,pch),等等。

[0074]

例如,控制中枢2432说明了连接到设备2400的附加设备的一个或多个连接点,例如,用户可以通过这些附加设备与系统进行交互。例如,可以附接到设备2400的设备(例如,设备2429)包括麦克风设备、扬声器或立体声系统、音频设备、视频系统或其他显示设备、键盘或小键盘设备、或者用于特定应用的其他i/o设备,例如读卡器或其他设备。

[0075]

如上所述,控制中枢2432可以与音频设备、显示器2422等等进行交互。例如,通过麦克风或其他音频设备的输入可以为设备2400的一个或多个应用或功能提供输入或命令。此外,取代显示输出,或者除了显示输出以外,还可以提供音频输出。在另一示例中,如果显示器2422包括触摸屏,则显示器2422也充当输入设备,该输入设备可至少部分由控制中枢2432来管理。在计算设备2400上也可以有额外的按钮或开关来提供由控制中枢2432管理的i/o功能。在一个实施例中,控制中枢2432管理诸如加速度计、相机、光传感器或其他环境传感器之类的设备,或者可被包括在设备2400中的其他硬件。输入可以是直接用户交互的一部分,以及向系统提供环境输入以影响其操作(例如,对噪声进行过滤,调整显示器以进行亮度检测,对相机应用闪光灯,或者其他特征)。

[0076]

在一些实施例中,控制中枢2432可以利用任何适当的通信协议耦合到各种设备,例如pcie(peripheral component interconnect express,快速外围组件互连)、usb(universal serial bus,通用串行总线)、雷电(thunderbolt)、高清晰度多媒体接口(high definition multimedia interface,hdmi)、火线(firewire),等等。

[0077]

在一些实施例中,显示器2422表示提供视觉和/或触觉显示来供用户与设备2400交互的硬件(例如,显示设备)和软件(例如,驱动器)组件。显示器2422可包括显示接口、显示屏、和/或用于向用户提供显示器的硬件设备。在一些实施例中,显示器2422包括向用户提供输出和输入两者的触摸屏(或触摸板)设备。在一示例中,显示器2422可以直接与处理器2404进行通信。显示器2422可以是像在移动电子设备或膝上型电脑设备中那样的内部显示设备或者经由显示接口(例如,displayport等等)附接的外部显示设备中的一个或多个。在一个实施例中,显示器2422可以是头戴式显示器(head mounted display,hmd),例如立体显示设备,来用于虚拟现实(virtual reality,vr)应用或增强现实(augmented reality,ar)应用中。

[0078]

在一些实施例中,虽然在附图中没有图示,但除了处理器2404以外(或者取代处理器2004),设备2400还可以包括图形处理单元(graphics processing unit,gpu),该图形处理单元包括一个或多个图形处理核心,其可控制在显示器2422上显示内容的一个或多个方面。

[0079]

控制中枢2432(或者平台控制器中枢)可包括硬件接口和连接器,以及软件组件(例如,驱动器、协议栈),来进行例如到外围设备2424的外围连接。

[0080]

将会理解,设备2400既可以是其他计算设备的外围设备,也可以有外围设备连接

到它。设备2400可具有“坞接”连接器来连接到其他计算设备,以便例如管理设备2400上的内容(例如,下载和/或上传、改变、同步)。此外,坞接连接器可以允许设备2400连接到某些外设,这些外设允许计算设备2400控制例如到视听或其他系统的内容输出。

[0081]

除了专属坞接连接器或其他专属连接硬件以外,设备2400还可以经由常见的或者基于标准的连接器来进行外围连接。常见类型可以包括通用串行总线(universal serial bus,usb)连接器(其可包括若干种不同硬件接口中的任何一种)、包括minidisplayport(mdp)的显示端口,高清晰度多媒体接口(high definition multimedia interface,hdmi)、火线、或者其他类型。

[0082]

在一些实施例中,连通性电路2431可耦合到控制中枢2432,例如除了直接耦合到处理器2404以外或者取代直接耦合到处理器2404。在一些实施例中,显示器2422可以耦合到控制中枢2432,例如除了直接耦合到处理器2404以外或者取代直接耦合到处理器2404。

[0083]

在一些实施例中,设备2400包括存储器2430,其经由存储器接口2434耦合到处理器2404。存储器2430包括用于存储设备2400中的信息的存储器设备。存储器可包括非易失性存储器设备(如果到存储器设备的电力中断,状态不会变化)和/或易失性存储器设备(如果到存储器设备的电力中断,则状态是不确定的)。存储器设备2430可以是动态随机存取存储器(dynamic random access memory,dram)设备、静态随机存取存储器(static random access memory,sram)设备、闪存设备、相变存储器设备、或者具有适当的性能来用作进程存储器的某种其他存储器设备。在一个实施例中,存储器2430可充当设备2400的系统存储器,以存储数据和指令来在一个或多个处理器2404执行应用或进程时使用。存储器2430可存储应用数据、用户数据、音乐、照片、文档或其他数据,以及与设备2400的应用和功能的执行有关的系统数据(无论是长期的还是暂时的)。

[0084]

各种实施例和示例的元素也可以以用于存储计算机可执行指令(例如,实现本文论述的任何其他过程的指令)的机器可读介质(例如,存储器2430)的形式来提供。机器可读介质(例如,存储器2430)可包括但不限于闪存、光盘、cd-rom、dvd rom、ram、eprom、eeprom、磁卡或光卡、相变存储器(phase change memory,pcm)、或者适合用于存储电子或计算机可执行指令的其他类型的机器可读介质。例如,本公开的实施例可以作为计算机程序(例如,bios)被下载,该计算机程序可经由通信链路(例如,调制解调器或网络连接)借由数据信号被从远程计算机(例如,服务器)传送到作出请求的计算机(例如,客户端)。

[0085]

在一些实施例中,设备2400包括温度测量电路2440,例如用于测量设备2400的各种组件的温度。在一示例中,温度测量电路2440可以被嵌入,或者耦合或附接到其温度要被测量和监视的各种组件。例如,温度测量电路2440可测量核心2408a、2408b、2408c、电压调节器2414、存储器2430、soc 2401的主板和/或设备2400的任何适当组件中的一个或多个的温度(或者其内的温度)。

[0086]

在一些实施例中,设备2400包括功率测量电路2442,例如用于测量设备2400的一个或多个组件消耗的功率。在一示例中,除了测量功率以外,或者取代测量功率,功率测量电路2442还可以测量电压和/或电流。在一示例中,功率测量电路2442可以被嵌入,或者耦合或附接到其功率、电压和/或电流消耗要被测量和监视的各种组件。例如,功率测量电路2442可测量由一个或多个电压调节器2414供应的功率、电流和/或电压、供应到soc 2401的功率、供应到设备2400的功率、由设备2400的处理器2404(或任何其他组件)消耗的功率,等

等。

[0087]

在一些实施例中,设备2400包括一个或多个电压调节器电路,统称为电压调节器(voltage regulator,vr)2414。vr 2414按适当的电压水平生成信号,这些信号可被供应来操作设备2400的任何适当组件。仅作为示例,vr 2414被图示为向设备2400的处理器2404供应信号。在一些实施例中,vr 2414接收一个或多个电压标识(voltage identification,vid)信号,并且基于vid信号生成处于适当水平的电压信号。对于vr 2414可利用各种类型的vr。例如,vr 2414可包括“降压”vr、“升压”vr、降压和升压vr的组合、低压差(low dropout,ldo)调节器、开关dc-dc调节器,等等。降压vr一般被用于其中输入电压需要被以小于单位一的比率变换成输出电压的电力输送应用中。升压vr一般被用于其中输入电压需要被以大于单位一的比率变换成输出电压的电力输送应用中。在一些实施例中,每个处理器核心具有其自己的vr,该vr被pcu 2410a/b和/或pmic 2412控制。在一些实施例中,每个核心具有分布式ldo的网络,来提供对功率管理的高效控制。ldo可以是数字的、模拟的或者是数字或模拟ldo的组合。

[0088]

在一些实施例中,设备2400包括一个或多个时钟生成器电路,统称为时钟生成器2416。时钟生成器2416可按适当的频率水平生成时钟信号,这些信号可被供应给设备2400的任何适当组件。仅作为示例,时钟生成器2416被图示为向设备2400的处理器2404供应时钟信号。在一些实施例中,时钟生成器2416接收一个或多个频率标识(frequency identification,fid)信号,并且基于fid信号按适当的频率生成时钟信号。时钟生成器2416是可如参考各种实施例所述提供自适应频率输出的自适应时钟源。

[0089]

在一些实施例中,设备2400包括向设备2400的各种组件供应电力的电池2418。仅作为示例,电池2418被图示为向处理器2404供应电力。虽然在附图中没有图示,但设备2400可包括充电电路,以例如基于从交流电(alternating current,ac)适配器接收的ac电力供应来对电池进行再充电。

[0090]

在一些实施例中,设备2400包括功率控制单元(power control unit,pcu)2410(也称为功率管理单元(power management unit,pmu)、功率控制器,等等)。在一示例中,pcu 2410的一些部分可由一个或多个处理核心2408实现,并且pcu 2410的这些部分被利用虚线框来象征性图示并且被标注为pcu 2410a。在一示例中,pcu 2410的一些其他部分可在处理核心2408外部实现,并且pcu 2410的这些部分被利用虚线框来象征性图示并且被标注为pcu 2410b。pcu 2410可为设备2400实现各种功率管理操作。pcu 2410可包括硬件接口、硬件电路、连接器、寄存器等等,以及软件组件(例如,驱动器、协议栈),来为设备2400实现各种功率管理操作。

[0091]

在一些实施例中,设备2400包括功率管理集成电路(power management integrated circuit,pmic)2412,以例如为设备2400实现各种功率管理操作。在一些实施例中,pmic 2412是可重配置功率管理ic(reconfigurable power management ic,rpmic)和/或imvp(mobile voltage positioning,移动电压定位)。在一示例中,pmic在与处理器2404分离的ic芯片内。这可为设备2400实现各种功率管理操作。pmic 2412可包括硬件接口、硬件电路、连接器、寄存器,等等,以及软件组件(例如,驱动器、协议栈),来为设备2400实现各种功率管理操作。

[0092]

在一示例中,设备2400包括pcu 2410或pmic 2412中的一者或两者。在一示例中,

pcu 2410或者pmic 2412中的任何一者可以不存在于设备2400中,因此这些组件是利用虚线来图示的。

[0093]

设备2400的各种功率管理操作可以由pcu 2410、由pmic 2412或者由pcu 2410和pmic 2412的组合来执行。例如,pcu 2410和/或pmic 2412可以为设备2400的各种组件选择功率状态(例如,p状态)。例如,pcu 2410和/或pmic 2412可以为设备2400的各种组件选择功率状态(例如,根据acpi(advanced configuration and power interface,高级配置和电力接口)规范)。仅作为示例,pcu 2410和/或pmic 2412可以使得设备2400的各种组件转变到睡眠状态、转变到活跃状态、转变到适当的c状态(例如,c0状态,或者另一适当的c状态,根据acpi规范),等等。在一示例中,pcu 2410和/或pmic 2412可控制由vr 2414输出的电压和/或由时钟生成器输出的时钟信号的频率,例如分别通过输出vid信号和/或fid信号。在一示例中,pcu 2410和/或pmic 2412可控制电池功率使用、电池2418的充电、以及与省电操作有关的特征。

[0094]

时钟生成器2416可包括锁相环(phase locked loop,pll)、锁频环(frequency locked loop,fll)、或者任何适当的时钟源。在一些实施例中,处理器2404的每个核心具有其自己的时钟源。这样,每个核心可按独立于其他核心的操作频率的频率来进行操作。在一些实施例中,pcu2410和/或pmic 2412执行适应性的或者动态的频率缩放或调整。例如,如果核心没有在其最大功率消耗阈值或限度下进行操作,则可增大该处理器核心的时钟频率。在一些实施例中,pcu 2410和/或pmic 2412确定处理器的每个核心的操作条件,并且当pcu 2410和/或pmic 2412确定核心在低于目标性能水平下操作时,适时地调整该核心的频率和/或供电电压,而核心钟控源(例如,该核心的pll)不会失去锁定。例如,如果核心在从电力供应轨汲取电流,该电流小于为该核心或处理器2404分配的总电流,则pcu 2410和/或pmic 2412可临时增大对于该核心或处理器2404的功率汲取(例如,通过增大时钟频率和/或电力供应电压水平),使得该核心或处理器2404可以按更高的性能水平来运转。这样,可以在不违反产品可靠性的情况下,为处理器2404临时增大电压和/或频率。

[0095]

在一示例中,pcu 2410和/或pmic 2412可例如至少部分地基于从功率测量电路2442、温度测量电路2440接收测量、接收电池2418的充电水平、和/或接收可用于功率管理的任何其他适当的信息,来执行功率管理操作。为此,pmic 2412通信地耦合到一个或多个传感器,来感测/检测对于系统/平台的功率/热行为有影响的一个或多个因素中的各种值/变化。一个或多个因素的示例包括电流、电压下降、温度、操作频率、操作电压、功率消耗、核心间通信活动,等等。这些传感器中的一个或多个可被设置为与计算系统的一个或多个组件或者逻辑/ip块物理地近邻(和/或与其热接触/耦合)。此外,在至少一个实施例中,(一个或多个)传感器可以直接耦合到pcu 2410和/或pmic 2412,以允许pcu 2410和/或pmic 2412至少部分地基于由这些传感器中的一个或多个检测到的(一个或多个)值来管理处理器核心能量。

[0096]

还图示了设备2400的示例软件栈(虽然没有图示该软件栈的所有元素)。仅作为示例,处理器2404可以执行应用程序2450、操作系统2452、一个或多个功率管理(power management,pm)特定应用程序(例如,一般称为pm应用2458),等等。pm应用2458也可被pcu 2410和/或pmic 2412执行。os 2452也可包括一个或多个pm应用2456a、2456b、2456c。os 2452也可包括各种驱动器2454a、2454b、2454c等等,其中一些可专用于功率管理目的。在一

些实施例中,设备2400还可包括基本输入/输出系统(basic input/output system,bios)2420。bios 2420可以与os 2452通信(例如,经由一个或多个驱动器2454),与处理器2404通信,等等。

[0097]

例如,pm应用2458、2456、驱动器2454、bios 2420等等中的一个或多个可用于实现功率管理特定任务,例如用于控制设备2400的各种组件的电压和/或频率,控制设备2400的各种组件的唤醒状态、睡眠状态和/或任何其他适当的功率状态,控制电池功率使用、电池2418的充电、与功率节省操作有关的特征,等等。

[0098]

说明书中提及“一实施例”、“一个实施例”、“一些实施例”或者“其他实施例”的意思是联系这些实施例描述的特定特征、结构或特性被包括在至少一些实施例中,但不一定包括在所有实施例中。“一实施例”、“一个实施例”或者“一些实施例”的各种出现不一定全都指的是相同的实施例。如果说明书陈述“可”、“可能”或者“可以”包括某一组件、特征、结构或特性,那么并不是必须要包括该特定组件、特征、结构或特性。如果说明书或权利要求提及“一”或“一个”元素,那么并不意味着只有一个该元素。如果说明书或权利要求提及“一额外”元素,那么并不排除有多于一个的该额外元素。

[0099]

此外,在一个或多个实施例中可按任何适当的方式来组合特定的特征、结构、功能或特性。例如,在与第一实施例和第二实施例相关联的特定特征、结构、功能或特性不互斥的任何地方,可将两个实施例相组合。

[0100]

虽然已经结合其特定实施例描述了本公开,但本领域普通技术人员根据前述描述,将会清楚这种实施例的许多替换、修改和变化。本公开的实施例旨在包含落在所附权利要求的宽广范围内的所有这样的替换、修改和变化。

[0101]

此外,为了图示和论述的简单起见,并且为了不模糊本公开,在给出的附图内可能示出或者不示出到集成电路(ic)芯片和其他组件的公知电力/接地连接。另外,可能以框图形式示出了布置以避免模糊本公开,并且同时也考虑到了如下事实:关于这种框图布置的实现方式的具体细节是高度取决于要在其内实现本公开的平台的(即,这种具体细节应当完全在本领域技术人员的认知内)。在阐述具体细节(例如,电路)以便描述本公开的示例实施例的情况下,本领域技术人员应当清楚,没有这些具体细节,或者利用这些具体细节的变体,也可实现本公开。因此,说明书应当被认为是说明性的,而不是限制性的。

[0102]

以下示例涉及进一步实施例。示例中的具体细节可被用在一个或多个实施例中的任何地方。也可对于方法或过程实现本文描述的装置的所有可选特征。

[0103]

示例1:一种装置,包括:控制器,用于生成模式信号,其中,所述模式信号指示出两个或更多个互连中的第一互连和第二互连的操作模式,其中,所述操作模式包括以下各项中的一项:第一模式、第二模式或者第三模式;以及与所述控制器通信地耦合的第一仲裁器,其中,所述第一仲裁器用于将所述两个或更多个互连中的第一互连配置为处于所述第一模式、所述第二模式或所述第三模式之一中;以及与所述控制器通信地耦合的第二仲裁器,其中,所述第二仲裁器用于将所述两个或更多个互连中的第二互连配置为处于与所述两个或更多个互连中的第一互连相同的模式中。

[0104]

示例2:如示例1所述的装置,其中,所述第一仲裁器和所述第二仲裁器可操作为:将所述两个或更多个互连中的第一互连的输入短接;将所述两个或更多个互连中的第一互连的输入连接到所述第一仲裁器或所述第二仲裁器的输入端口或输出端口;或者将所述两

个或更多个互连中的第一互连之一的输入与所述第一仲裁器或所述第二仲裁器的输入端口或输出端口断开连接。

[0105]

示例3:如示例1所述的装置,其中,所述两个或更多个互连中的第一互连中的至少一者和所述两个或更多个互连中的第二互连中的至少一者被电力供应线或地线所屏蔽。

[0106]

示例4:如示例1所述的装置,其中,所述第一模式是带宽模式,其中,所述第一仲裁器和所述第二仲裁器使得在所述两个或更多个互连中的第一互连和第二互连上传播单独的信号。

[0107]

示例5:如示例1所述的装置,其中,所述第二模式是时延模式,其中,所述第一仲裁器和所述第二仲裁器使得在所述两个或更多个互连中的第一互连上传播第一相同信号,并且在所述两个或更多个互连中的第二互连上传播第二相同信号。

[0108]

示例6:如示例1所述的装置,其中,所述第三模式是能量模式,其中,所述第一仲裁器和所述第二仲裁器使得交替地在所述两个或更多个互连中的第一互连上并交替地在所述两个或更多个互连中的第二互连上传播信号。

[0109]

示例7:如示例1所述的装置,其中,所述控制器是功率管理单元,该功率管理单元也可操作为执行动态电压和频率缩放。

[0110]

示例8:一种装置,包括:功率管理单元(pmu),用于生成模式控制;以及与所述pmu耦合的仲裁器的网格网络,其中,所述仲裁器的网格网络包括:第一仲裁器,与所述pmu通信地耦合并且接收所述模式控制;第二仲裁器,与所述pmu通信地耦合并且接收所述模式控制;第一对信号路径,具有与所述第一仲裁器耦合的第一驱动器和第二驱动器,以及与所述第二仲裁器耦合的第一接收器和第二接收器;以及第二对信号路径,具有与所述第二仲裁器耦合的第三驱动器和第四驱动器,以及与所述第一仲裁器耦合的第三接收器和第四接收器;其中,所述第一仲裁器和所述第二仲裁器根据所述模式控制将所述第一对信号路径和所述第二对信号路径配置为处于第一模式、第二模式或第三模式之一中。

[0111]

示例9:如示例8所述的装置,其中,所述pmu用于执行动态电压和频率缩放。

[0112]

示例10:如示例8所述的装置,其中,所述第一仲裁器和所述第二仲裁器可操作为:将所述第一对信号路径的每个输入连接到所述第一仲裁器或所述第二仲裁器的每个输入端口或输出端口;或者将所述第一对信号路径的输入短接到所述第一仲裁器或所述第二仲裁器的同一信号端口。

[0113]

示例11:如示例8所述的装置,其中,所述第一仲裁器和所述第二仲裁器可操作为:将所述第一对信号路径中的信号路径之一的输入的一个电路径开路;或者将所述第一对信号路径的每个输入连接到所述第一仲裁器或所述第二仲裁器的每个输入端口或输出端口。

[0114]

示例12:如示例8所述的装置,其中,所述第一仲裁器和所述第二仲裁器可操作为:将所述第二对信号路径的每个输入连接到所述第一仲裁器或所述第二仲裁器的每个输入端口或输出端口;或者将所述第二对信号路径的输入短接到所述第一仲裁器或所述第二仲裁器的同一信号端口。

[0115]

示例13:如示例8所述的装置,其中,所述第一仲裁器和所述第二仲裁器可操作为:将所述第二对信号路径中的信号路径之一的输入的一个电路径开路;或者将所述第一对信号路径的每个输入连接到所述第一仲裁器或所述第二仲裁器的每个输入端口或输出端口。

[0116]

示例14:如示例8所述的装置,其中,所述第一模式是带宽模式,其中,所述第一仲

裁器和所述第二仲裁器使得在所述第一对信号路径和所述第二对信号路径上传播单独的信号。

[0117]

示例15:如示例8所述的装置,其中,所述第二模式是时延模式,其中,所述第一仲裁器和所述第二仲裁器使得在所述第一对信号路径上传播第一相同信号,并且在所述第二对信号路径上传播第二相同信号。

[0118]

示例16:如示例8所述的装置,其中,所述第三模式是能量模式,其中,所述第一仲裁器和所述第二仲裁器使得交替地在所述第一对信号路径和所述第二对信号路径中的信号路径上传播信号。

[0119]

示例17:一种系统,包括:存储器;与所述存储器耦合的处理器核心;功率管理单元(pmu),与所述核心耦合并且在所述处理器核心上执行动态电压和频率缩放;包括网格网络或环线网络的片上网络(noc),其中,所述noc包括:与所述pmu耦合的仲裁器的网络,其中,所述仲裁器的网络包括:第一仲裁器,与所述pmu通信地耦合并且接收模式控制;第二仲裁器,与所述pmu通信地耦合并且接收所述模式控制;第一对信号路径,具有与所述第一仲裁器耦合的第一驱动器和第二驱动器,以及与所述第二仲裁器耦合的第一接收器和第二接收器;以及第二对信号路径,具有与所述第二仲裁器耦合的第三驱动器和第四驱动器,以及与所述第一仲裁器耦合的第三接收器和第四接收器,其中,所述第一仲裁器和所述第二仲裁器根据所述模式控制将所述第一对信号路径和所述第二对信号路径配置为处于第一模式、第二模式或第三模式之一中;以及无线接口,用于允许所述处理器核心与另一设备进行通信。

[0120]

示例18:如示例17所述的系统,其中,所述第一模式是带宽模式,其中,所述第一仲裁器和所述第二仲裁器使得在所述第一对信号路径和所述第二对信号路径上传播单独的信号。

[0121]

示例19:如示例17所述的系统,其中,所述第二模式是时延模式,其中,所述第一仲裁器和所述第二仲裁器使得在所述第一对信号路径上传播第一相同信号,并且在所述第二对信号路径上传播第二相同信号。

[0122]

示例20:如示例17所述的系统,其中,所述第三模式是能量模式,其中,所述第一仲裁器和所述第二仲裁器使得交替地在所述第一对信号路径和所述第二对信号路径中的信号路径上传播信号。

[0123]

提供了摘要,它将允许读者确定本技术公开内容的性质和主旨。摘要是带着如下理解提交的:它不会被用于限制权利要求的范围或含义。特此将所附权利要求纳入到详细描述中,其中每个权利要求独立作为一个单独的实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。