1.本发明涉及多媒体播放技术领域,特别涉及多路视频码流实时处理、同屏播放方法及相关系统。

背景技术:

2.在当前数字信息时代,伴随着人工智能(artificial intelligence,ai)产业的飞速发展,已存在大量网络摄像机ip camera,而这些相关的ip camera目前主要作为监控视频的用途,ai推动这些存量的ip camera面向更多的新需求,而多路实时视频处理方式和多窗口实时监控画面展现可降低大量的资金成本,故实现对多路ip camera实时拍摄的视频进行同步处理和多窗口同步播放是目前亟待解决的技术问题。

技术实现要素:

3.公开号为cn101668206a,名称为“基于h.264的多路视频解码显示方法及系统”的中国专利,提供了一种多路视频流显示的方法。该方案实现了多路同时播放视频显示,可对各个视频分别控制。该方案流程如下:

4.1.选择播放窗口,选择欲播放的视频文件,判断当前窗口的视频播放状态是否为停止;

5.2.如果是则进行下一步骤,否则先停止该窗口正在播放的视频;

6.3.然后进行下一步骤,取得所选择视频文件的路径和名称,显示于屏幕上指定位置;

7.4.根据选择的窗口号创建相应的播放线程,用于在所选择的窗口位置播放显示视频文件,判断是否又有新的视频文件要播放,是则进行第一步骤,否则进行下一步,执行播放线程函数。

8.上述方案虽然提供了视频码流分别控制的思想,但无法提供网络实时视频码流的方案,且无法实现pipeline的方式,如当前输入高清视频时,进行多路视频显示会造成高清视频占用cpu性能过高,从而降低屏幕显示(on-screen display,osd)的流畅度。

9.公开号为cn1767601a,名称为“一种支持多源流媒体的同步播放控制方法”的中国专利,提供了一种支持多源流媒体的同步播放控制方法,实现该方法的装置包括分离器、解码器组、多源流媒体同步模块、多源视频流融合模块、osd模块以及音频滤镜模块;分离器将多个本地媒体文件或多路流媒体中的视音频数据进行分离;解码器组调用相应解码器,解码后数据被送至多源流媒体同步模块;多源流媒体同步模块采用多粒度分层同步控制机制对媒体对象之间以及媒体对象内的多路流媒体进行同步控制;多路视频由多源视频融合模块融合为一路视频;osd模块将融合后的数据与音量大小、当前播放时间或字幕信息叠加后进行视频输出;多路音频由音频滤镜模块进行格式转换、线性叠加后进行音频输出。

10.上述方案在osd数据融合过程中会造成大量的yuv数据拷贝,容易导致cpu性能低下;且针对网络流媒体,无法进行自适应码流控制,在播放流畅度体验上比较差,如多路显

示视频,osd数据融合过程中对于高清视频,会出现耗时的数据拷贝,造成整体性能下降;该方案针对多源不同帧率的视频码流,在显示频率上做出解决方案,会造成osd刷新频率固定下,显示丢帧的情况。

11.鉴于上述问题,提出了本发明以便提供一种克服上述问题或者至少部分地解决上述问题的多路视频码流实时处理、同屏播放方法及相关系统。

12.第一方面,本发明实施例提供一种多路视频码流实时处理方法,包括:

13.并行接收各视频服务器通过关联的码流接收通道发送的实时视频码流,将接收的实时视频码流拆分为多帧数据帧,将数据帧加入对应缓存队列,所述码流接收通道与分配的cpu内存绑定,所述码流接收通道与所述缓存队列一一对应;

14.针对每个缓存队列,按设定间隔向对应硬件解码缓存区域发送数据帧;

15.并行对各解码缓存区域中的数据帧进行硬件解码,将得到的解码后数据帧输送到对应渲染缓存区域;

16.并行离屏渲染各渲染缓存区域中的解码后数据帧,得到用于播放的渲染后数据帧。

17.第二方面,本发明实施例提供一种多路视频码流同屏播放方法,包括:

18.并行接收各视频服务器通过关联的码流接收通道发送的实时视频码流,将接收的实时视频码流拆分为多帧数据帧,将数据帧加入对应缓存队列,所述码流接收通道与分配的cpu内存绑定,所述码流接收通道与所述缓存队列一一对应;

19.针对每个缓存队列,按设定间隔向对应硬件解码缓存区域发送数据帧;

20.并行对各解码缓存区域中的数据帧进行硬件解码,将得到的解码后数据帧输送到对应渲染缓存区域;

21.根据对应子窗口的位置并行离屏渲染各渲染缓存区域中的解码后数据帧,在所述子窗口播放渲染后数据帧,实现各路实时视频码流的同屏播放。

22.第三方面,本发明实施例提供一种多路视频码流实时处理系统,包括实时码流接收模块、实时码流缓存模块、硬件解码组件和渲染模块;

23.所述实时码流接收模块,用于并行接收各视频服务器通过关联的码流接收通道发送的实时视频码流,将接收的实时视频码流拆分为多帧数据帧,将数据帧加入所述实时码流缓存模块中的对应缓存队列,所述码流接收通道与分配的cpu内存绑定,所述码流接收通道与所述缓存队列一一对应;

24.所述实时码流缓存模块,用于针对每个缓存队列,按设定间隔向所述硬件解码组件的对应硬件解码缓存区域发送数据帧;

25.所述硬件解码组件,用于并行对各解码缓存区域中的数据帧进行硬件解码,将得到的解码后数据帧输送到所述渲染模块的对应渲染缓存区域;

26.所述渲染模块,用于并行离屏渲染各渲染缓存区域中的解码后数据帧,得到用于播放的渲染后数据帧。

27.第四方面,本发明实施例提供一种多路视频码流同屏播放系统,包括实时码流接收模块、实时码流缓存模块、硬件解码组件和视频显示模块;

28.所述实时码流接收模块,用于并行接收各视频服务器通过关联的码流接收通道发送的实时视频码流,将接收的实时视频码流拆分为多帧数据帧,将数据帧加入所述实时码

流缓存模块中的对应缓存队列,所述码流接收通道与分配的cpu内存绑定,所述码流接收通道与所述缓存队列一一对应;

29.所述实时码流缓存模块,用于针对每个缓存队列,按设定间隔向所述硬件解码组件的对应硬件解码缓存区域发送数据帧;

30.所述硬件解码组件,用于并行对各解码缓存区域中的数据帧进行硬件解码,将得到的解码后数据帧输送到所述视频显示模块的对应渲染缓存区域;

31.所述视频显示模块,用于根据对应子窗口的位置并行离屏渲染各渲染缓存区域中的解码后数据帧,在所述子窗口播放渲染后数据帧,实现各路实时视频码流的同屏播放。

32.第五方面,本发明实施例提供一种终端设备,所述终端设备设置有上述多路视频码流实时处理系统,或设置有上述多路视频码流同屏播放系统。

33.第六方面,本发明实施例提供一种多路视频码流同屏播放系统,包括播放设备和多路视频服务器,所述播放设备设置有上述多路视频码流同屏播放系统;

34.所述终端设备用于同屏播放各路所述视频服务器发送的实时视频码流。

35.第七方面,本发明实施例提供一种计算机可读存储介质,其上存储有计算机指令,当该指令被处理器执行时实现上述多路视频码流实时处理方法,或实现上述多路视频码流同屏播放方法。

36.本发明实施例提供的上述技术方案的有益效果至少包括:

37.(1)本发明实施例提供的多路视频码流实时处理方法,并行接收各视频服务器通过关联的码流接收通道发送的实时视频码流,将接收的实时视频码流拆分为多帧数据帧,将数据帧加入对应缓存队列,码流接收通道与分配的cpu内存绑定,码流接收通道与所述缓存队列一一对应;针对每个缓存队列,按设定间隔向对应硬件解码缓存区域发送数据帧;并行对各解码缓存区域中的数据帧进行硬件解码,将得到的解码后数据帧输送到对应渲染缓存区域;并行离屏渲染各渲染缓存区域中的解码后数据帧,得到用于播放的渲染后数据帧。通过各码流接收通道与cpu资源绑定的方式,实现了cpu资源的合理利用,避免了单路通道占用cpu资源过高的现象,从而保证系统的整体运行流畅;解码后数据帧直接输送到对应渲染缓存区域,而不是在cpu本地缓存,即解码后数据帧直通屏幕显示(on-screen display,osd),避免了过多数据拷贝带来的cpu资源大量占用,提供了cpu使用效率,加快了数据渲染速度。故本发明实施例提供的多路视频码流并行处理方法实现了多路视频码流实时并线处理,且优化了cpu资源的占用。

38.(2)本发明实施例提供的多路视频码流实时处理方法,将通过码流接收通道接收的实时视频码流拆分为数据帧后加入与接收通道对应的缓存队列,按设定间隔向对应硬件解码缓存区域发送缓存队列中的数据帧,即通过pipeline的方式,实现了自适应码流控制;实时视频码流动态缓存队列控制,可以很好的解决网络时延抖动的问题,同时可以解决码流数据堆积而内存溢出的问题;按设定间隔向硬件解码缓存区域发送数据帧,可以充分发挥硬件解码组件的解码性能。

39.(3)本发明实施例提供的多路视频码流实时处理方法,采用硬件解码,支持多路同时解码,减少cpu的性能占用,可以增加接入的视频码流路数。以16路视频码流解码为例,cpu占用可减低300%。

40.(4)本发明实施例提供的多路视频码流同屏播放方法,并行接收各视频服务器通

过关联的码流接收通道发送的实时视频码流,将接收的实时视频码流拆分为多帧数据帧,将数据帧加入对应缓存队列,码流接收通道与分配的cpu内存绑定,码流接收通道与缓存队列一一对应;针对每个缓存队列,按设定间隔向对应硬件解码缓存区域发送数据帧;并行对各解码缓存区域中的数据帧进行硬件解码,将得到的解码后数据帧输送到对应渲染缓存区域;根据对应子窗口的位置并行离屏渲染各渲染缓存区域中的解码后数据帧,在子窗口播放渲染后数据帧,实现各路实时视频码流的同屏播放。实现了多路视频码流的实时多窗口同屏播放,同时可分别控制各路视频码流的播放。

41.下面通过附图和实施例,对本发明的技术方案做进一步的详细描述。

附图说明

42.附图用来提供对本发明的进一步理解,并且构成说明书的一部分,与本发明的实施例一起用于解释本发明,并不构成对本发明的限制。在附图中:

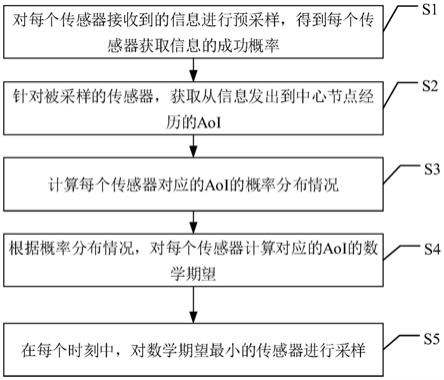

43.图1为本发明实施例一所述的多路视频码流实时处理方法流程图;

44.图2为图1中的步骤s12的一种具体实现流程图;

45.图3为图1中的步骤s11的一种具体实现流程图;

46.图4为图1中的步骤s12的另一种具体实现流程图;

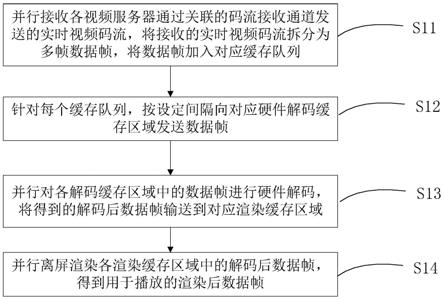

47.图5为本发明实施例二所述的多路视频码流同屏播放方法的流程图;

48.图6为本发明实施例二中fbo方式离屏渲染的具体实现流程图;

49.图7为本发明实施例中ai融合的一种具体实现流程图;

50.图8为本发明实施例中一种多路视频码流实时处理系统的结构示意图;

51.图9为本发明实施例中一种多路视频码流同屏播放系统的结构示意图;

52.图10为本发明实施例中一种多路视频码流同屏播放系统的结构示意图。

具体实施方式

53.下面将参照附图更详细地描述本公开的示例性实施例。虽然附图中显示了本公开的示例性实施例,然而应当理解,可以以各种形式实现本公开而不应被这里阐述的实施例所限制。相反,提供这些实施例是为了能够更透彻地理解本公开,并且能够将本公开的范围完整的传达给本领域的技术人员。

54.为了实现对多路视频码流同步实时处理和同屏播放,本发明实施例提供一种多路视频码流实时处理方法和相关系统,能够实现多路视频码流实时并线处理和同屏播放,且优化了cpu内存资源的占用。

55.实施例一

56.本发明实施例一提供一种多路视频码流实时处理方法,其流程如图1所示,包括如下步骤:

57.步骤s11:并行接收各视频服务器通过关联的码流接收通道发送的实时视频码流,将接收的实时视频码流拆分为多帧数据帧,将数据帧加入对应缓存队列。

58.具体的,上述码流接收通道与分配的cpu内存绑定,码流接收通道与缓存队列一一对应。

59.码流接收通道可以是预先建立好的,也可以是在监测到新接入的视频服务器后实

时创建;缓存队列可以是预先建立好的,即在预先建立码流接收通道时建立与其一一对应的缓存队列,可选的,缓存队列也可以是在接收到新的视频服务器发送视频码流时实时创建。

60.为码流接收通道分配cpu资源,可以是平均分配闲置的cpu资源;也可以是根据码流接收通道关联的视频服务器的码流的码率和/或分辨率,为码流接收通道分配cpu资源。cpu内存的分配与绑定可以更好的支持多路视频码流的并行实时接收,且有效分配了cpu资源。

61.接收视频服务器通过关联的码流接收通道发送的实时视频码流,可以是接收支持实时流传输协议(real time streaming protocol,rtsp)的视频服务器通过socket通信发送的实时视频码流。

62.将接收的实时视频码流拆分为多帧数据帧,具体可以包括,将接收的实时视频码流解析后封装为数据包;将数据包拆分为多帧数据帧,为每帧数据帧填加预先从视频服务器回复的描述会话的协议(session description protocol,sdp)信息中解析出的视频参数集(video parameter set,vps)、图像参数集(pps picture parameter set,pps)和序列参数集(sequence parameter set,sps)。

63.具体码流接收通道及其通信连接的创建和具体视频码流的实时接收后续详细介绍。

64.步骤s12:针对每个缓存队列,按设定间隔向对应硬件解码缓存区域发送数据帧。

65.具体的,参照图2所示,缓存队列按设定间隔向对应硬件解码缓存区域发送数据帧,可以包括下述步骤:

66.步骤s1211:开始。

67.步骤s1212:判断当前时间与向对应硬件解码缓存区域发送上一数据帧的时间的间隔是否不小于设定间隔。

68.设定间隔可以是根据视频服务器对应的摄像机帧率确定。例如,帧率为25帧/秒,则设定间隔为1000/framerate(ms),即40ms。数据发送过快或过慢,均会影响硬件解码组件的解码性能。

69.上述摄像机的帧率,为摄像机配置好的;也可以是解析出的帧率,但解析的帧率往往会与真实的帧率存在一定的误差。

70.若步骤s1212判断为是,则执行步骤s1216;若步骤s1212判断为否,则执行步骤s1213。

71.步骤s1213:等待至当前时间与向对应硬件解码缓存区域发送上一数据帧的时间的间隔等于设定间隔。

72.阻塞,等待剩余间隔的差值等于设定间隔。

73.步骤s1214:判断当前缓存队列中数据帧的帧数是否大于设定帧数。

74.具体的,设定帧数可以是gop_num,为一组画面组包含的数据帧的帧数;更具体的,为两个关键帧之间的间隔数,即关键帧到相邻的下一关键帧间的帧数(包含关键帧,不包含下一关键帧)。关键帧可以是i帧。

75.若步骤s1214判断为是,执行步骤s1215;若步骤s1214判断为否,执行步骤s1216。

76.步骤s1215:按接收时间由先到后的顺序遍历当前缓存队列,直至当前遍历的数据

帧为关键帧。

77.具体的,按接收时间由先到后的顺序遍历当前缓存队列,若当前遍历的数据帧不是关键帧,释放当前数据帧,直至当前遍历的数据帧为关键帧;或,

78.按接收时间由先到后的顺序遍历当前缓存队列,直至当前遍历的数据帧为关键帧,释放遍历过的非关键数据帧。

79.当前帧队列中的待发送的数据帧较多时(多于一组画面组包含的数据帧的帧数),及时释放过多的数据帧,即不会影响播放的流畅度,又不影响解码组件的解码性能,保证了视频码流处理和最终播放的实时性。

80.步骤s1216:向对应解码缓存区域发送当前数据帧。

81.循环执行上述步骤s1212~s1216,直到接收到视频码流传输结束的消息,执行步骤s1217。

82.步骤s1217:结束。

83.步骤s13:并行对各解码缓存区域中的数据帧进行硬件解码,将得到的解码后数据帧输送到对应渲染缓存区域。

84.上述硬件解码缓存区域与缓存队列是一一对应的,硬件解码缓存区域与渲染缓存区域也是一一对应的。

85.硬件解码就是通过硬件进行视频码流的解码工作,硬件解码可以是由gpu来进行的,使用gpu解码能够降低cpu的工作负荷,降低功耗;软件解码则是通过软件本身占用的cpu内存进行解码。

86.在一些实施例中,若判断cpu存在闲置内存,还可以包括,缓存队列按设定间隔向对应软件解码缓存区域发送数据帧;相应的,并行对各硬件解码缓存区域中的数据帧进行硬件解码,还可以包括:并行对各软件解码缓存区域中的数据帧进行软件解码。

87.通过软硬件组合解码的方式,充分发挥cpu的内存使用率。

88.步骤s14:并行离屏渲染各渲染缓存区域中的解码后数据帧,得到用于播放的渲染后数据帧。

89.利用帧缓冲区对象(frame buffer object,fbo)方式离屏渲染各渲染缓存区域中的解码后数据帧。

90.本发明实施例一提供的多路视频码流实时处理方法,通过各码流接收通道与cpu资源绑定的方式,实现了cpu资源的合理利用,避免了单路通道占用cpu资源过高的现象,从而保证系统的整体运行流畅;解码后数据帧直接输送到对应渲染缓存区域,而不是在cpu本地缓存,即解码后数据帧直通屏幕显示(on-screen display,osd),避免了过多数据拷贝带来的cpu资源大量占用,提供了cpu使用效率,加快了数据渲染速度。故本发明实施例提供的多路视频码流并行处理方法实现了多路视频码流实时并线处理,且优化了cpu资源的占用。

91.本发明实施例一提供的多路视频码流实时处理方法,将通过码流接收通道接收的实时视频码流拆分为数据帧后加入与接收通道对应的缓存队列,按设定间隔向对应硬件解码缓存区域发送缓存队列中的数据帧,即通过pipeline的方式,实现了自适应码流控制;实时视频码流动态缓存队列控制,可以很好的解决网络时延抖动的问题,同时可以解决码流数据堆积而内存溢出的问题;按设定间隔向硬件解码缓存区域发送数据帧,可以充分发挥硬件解码组件的解码性能。

92.本发明实施例一提供的多路视频码流实时处理方法,采用硬件解码,支持多路同时解码,减少cpu的性能占用,可以增加接入的视频码流路数。以16路视频码流解码为例,cpu占用可减低300%。

93.具体的,参见图3所示,上述步骤s11的具体实现可以包含下述步骤:

94.(1)开始。

95.(2)初始化client id。

96.确定当前连接的每个视频服务器client的标识id,用视频服务器的id来标识其发送的视频码流,从而区分各路视频码流。

97.(3)初始化cpu绑定。

98.确定当前闲置的cpu内存,为各码流接收通道合理分配闲置的cpu内存,可均衡cpu性能,保证各路视频码流接收的实时性。

99.上述步骤(2)和(3)完成了创建多线程任务,然后每一线程通过后续步骤接收对应的视频服务器通过关联的码流接收通道发送的实时视频码流。具体的,可以是,每一线程与对应的rtspserver创建socket通信,接收一路支持rtsp协议的视频源发送的实时视频码流。

100.每一线程与rtspserver创建socket通信,并通过socket通信接收实时视频码流的过程包含下述步骤(4)~(9)。

101.(4)请求options。

102.向rtspserver请求rtsp协议options应答,即请求rtspserver支持的rtsp操作,例如,建立连接、码流描述、setup、play、pose和teardown等操作。

103.(5)解析sdp。

104.解析rtspserver回复的sdp信息,用于获取视频参数集vps、图像参数集pps和序列参数集sps等信息。

105.vps可能包含的信息有:多个子层和操作点共享的语法元素;会话所需的有关操作点的关键信息,如档次、级别;以及其他不属于sps的操作点特性信息。

106.sps中所含的语法元素,其内容大致可能包含以下几个部分:

107.图像格式的信息:包括采样格式、图像分辨率、量化深度、解码图像是否需要裁剪输出以及相关的裁剪参数;编码参数信息;与参考图像相关的信息:包括短期参考图像的设置,长期参考图像的使用和数目,长期参考图像的poc和其能否作为当前图像的参考图像;档次、层和级相关参数;时域分级信息;可视化可用性信息(video usability information,vui),用于表征视频格式等额外信息;其他信息:包括当前sps引用的vps编号、sps标识号和sps扩展信息。

108.pps中所涉及的具体的语法元素,内容大致可能包含以下几个部分:

109.编码工具的可用性标志:指明片头中一些工具是否可用;量化过程相关句法元素:包括每个slce中qp初始值的设定以及计算每个cu的qp时所需的参数;tile相关句法元素;去方块滤波相关句法元素;片头中的控制信息;其他编码一幅图像时可以共用的信息:包括id标识符、参考图像的数目和并行产生merge候选列表的能力等。

110.(6)请求setup。

111.请求rtspserver创建应答,与rtspserver创建连接。

112.(7)请求play。

113.请求rtspserverplay应答,即通知rtspserver可以发送视频码流了,用于启动接收码流信息。

114.(8)接收码流。

115.具体包括下述步骤:

116.1)接收rtsp码流。

117.接收rtp实时视频码流。

118.2)解析playload。

119.负载playload是数据传输中所欲传输的实际信息,通常也被称作实际数据或者数据体,解析接收到的实际数据体。

120.3)加载生成packet。

121.将解析后的playload封装为packet包。

122.4)分割为frame。

123.将封装的数据包packets分割成frame数据帧。

124.以完整的数据帧为单位,可以解决硬件解码组件缓存空间数据由于数据堆积,单路视频解码占据性能而阻塞的问题。

125.5)加载sdp头信息。

126.将每帧数据前缀加上sdp中的vps、pps和sps相关信息。

127.6)组合为frame。

128.分割后的数据帧前缀中填加vps、pps和sps相关信息后组合为新的数据帧frame。

129.7)加载到decoder缓存区。

130.加载frame数据到硬件解码组件缓冲区,即gpu缓冲区。

131.循环操作1)到7)步骤,接收实时视频码流,直至退出循环操作。

132.(9)请求teardown。

133.请求rtspserver断开视频码流。

134.具体的上述步骤(4)~(9)可以是按照实时传输控制协议(real-time transport control protocol,rtcp)进行,步骤(8)中的子步骤1)~7)可以是按照实时传输协议(real-time transport protocol,rtp)执行。

135.(10)结束。

136.具体的,参见图4所示,上述步骤s12的具体实现可以包含下述步骤:

137.步骤s1221:开始。

138.步骤s1222:判断当前时间与向对应硬件解码缓存区域发送上一数据帧的时间的间隔是否不小于设定间隔。

139.若步骤s1222判断为是,则执行步骤s1227;若步骤s1222判断为否,则执行步骤s1223。

140.步骤s1223:等待至当前时间与向对应硬件解码缓存区域发送上一数据帧的时间的间隔等于设定间隔。

141.阻塞,等待剩余间隔的差值等于设定间隔。

142.步骤s1224:判断当前缓存队列中数据帧的帧数是否大于设定帧数。

143.具体的,设定帧数可以是gop_num,为一组画面组包含的数据帧的帧数;更具体的,为两个关键帧之间的间隔数,即关键帧到相邻的下一关键帧间的帧数(包含关键帧,不包含下一关键帧)。关键帧可以是i帧。

144.若步骤s1224判断为是,执行步骤s1225;若步骤s1224判断为否,执行步骤s1227。

145.步骤s1225:判断当前数据帧是否为关键帧。

146.若是,执行步骤s1227;若否,执行步骤s1226。

147.步骤s1226:删除当前数据帧。

148.步骤s1226后返回执行步骤s1225,这里的当前数据帧,为按照接收时间由先到后的顺序依次遍历的待发送的当前数据帧。

149.步骤s1227:向对应解码缓存区域发送当前数据帧。

150.循环执行上述步骤s1222~s1227,直到接收到视频码流传输结束的消息,执行步骤s1228。

151.步骤s1228:结束。

152.实施例二

153.本发明实施例二提供一种多路视频码流同屏播放方法,其流程如图5所示,包括如下步骤:

154.步骤s51:并行接收各视频服务器通过关联的码流接收通道发送的实时视频码流,将接收的实时视频码流拆分为多帧数据帧,将数据帧加入对应缓存队列。

155.码流接收通道与分配的cpu内存绑定,码流接收通道与缓存队列一一对应。

156.步骤s52:针对每个缓存队列,按设定间隔向对应硬件解码缓存区域发送数据帧。

157.步骤s53:并行对各解码缓存区域中的数据帧进行硬件解码,将得到的解码后数据帧输送到对应渲染缓存区域。

158.步骤s54:根据对应子窗口的位置并行离屏渲染各渲染缓存区域中的解码后数据帧,在子窗口播放渲染后数据帧,实现各路实时视频码流的同屏播放。

159.预先定义好各路视频码流在屏幕中的播放位置,即子窗口的位置,对视频码流进行渲染过程中,根据对应子窗口的位置离屏渲染对应渲染缓存区域中的解码后数据帧,并在子窗口播放渲染后数据帧,从而实现各路实时视频码流的同屏播放,且各路视频码流的播放分别可控。

160.本发明实施例二提供的多路视频码流同屏播放方法,并行接收各视频服务器通过关联的码流接收通道发送的实时视频码流,将接收的实时视频码流拆分为多帧数据帧,将数据帧加入对应缓存队列,码流接收通道与分配的cpu内存绑定,码流接收通道与缓存队列一一对应;针对每个缓存队列,按设定间隔向对应硬件解码缓存区域发送数据帧;并行对各解码缓存区域中的数据帧进行硬件解码,将得到的解码后数据帧输送到对应渲染缓存区域;根据对应子窗口的位置并行离屏渲染各渲染缓存区域中的解码后数据帧,在子窗口播放渲染后数据帧,实现各路实时视频码流的同屏播放。实现了多路视频码流的实时多窗口同屏播放,同时可分别控制各路视频码流的播放。

161.具体的,可以是利用fbo方式根据对应子窗口的位置离屏渲染各渲染缓存区域中的解码后数据帧,参见图6所示,具体实现可以包含下述步骤:

162.步骤s61:开始。

163.步骤s62:初始化vbo数组。

164.初始化顶点缓冲对象vbo数组。

165.步骤s63:初始化fbo数组。

166.初始化帧缓冲区对象fbo数组,确定对应子窗口的坐标位置。

167.步骤s64:编译链接用于渲染的顶点着色器程序。

168.步骤s65:创建纹理。

169.创建相关的纹理,用于加载视频数据。具体的,创建一个2d纹理,用于连接fbo颜色附着。主要可以包括下述步骤:

170.步骤s651:创建fbo纹理。

171.步骤s652:绑定fbo纹理。

172.步骤s653:将fbo纹理连接到fbo附着。

173.步骤s654:分配gpu内存。

174.步骤s655:创建定时绘制线程。

175.每条线程执行的任务主要包括:

176.步骤s6551:刷新定时器信号。

177.按照接收到的定时刷新信号,刷新定时器信号。

178.步骤s6552:设置视口。

179.即设置显示的窗口位置,具体根据预先分配好的子窗口位置设置。

180.步骤s6553:设置纹理显示位置。

181.步骤s6554:刷新fbo绑定纹理。

182.步骤s6555:fbo离屏渲染。

183.步骤s6556:释放资源。

184.循环操作步骤s6551~步骤s6555,直到接收到播控退出的消息。

185.步骤s66:结束。

186.在一些实施例中,上述方法还可以包括,将从渲染缓存区域获取的渲染后数据帧发送到ai缓存区域;将ai缓存区域中的各路视频码流的渲染后数据帧进行时间对齐,将各路视频码流的同一时间的渲染后数据帧融合为一帧,得到融合后数据帧。

187.上述ai融合,即将多帧数据帧融合为一帧,参见图7所示,具体实现可以包含下述步骤:

188.步骤s71:开始。

189.步骤s72:获取一帧源数据的步长值。

190.获取融合前的数据,即源数据src数据的步长stride值,融合前的源数据的格式可以是rgba数据。rgba数据代表red(红色)、green(绿色)、blue(蓝色)和alpha的色彩空间。

191.可以是通过源数据的一帧数据的宽width与4的最小公倍数获取。

192.步骤s73:获取融合后目标数据的步长值。

193.即获取融合后目标dst数据的stride值。具体的,步长值的获取也根据相应数据的宽度获取。

194.步骤s74:根据源数据在目标数据的融合的位置(to_x,to_y),计算出偏移内存地址(dst=to_x*width to_y)。

195.步骤s75:加速拷贝一行像素。

196.采用neon指令系统的汇编指令加速拷贝一行像素。

197.步骤s76:根据src_stride计算src拷贝的偏移位置(src =src_stride)。

198.步骤s77:根据dst_stride计算目标数据被复制到的偏移位置(dst =dst_stride (width-to_x))。

199.步骤s78:判断计算次数是否等于源数据的高。

200.若是,执行步骤s79;若否,返回执行步骤s74。

201.步骤s79:结束。

202.解码后数据直通ai缓存区域,加快了ai运算。

203.上述实施例一和实施例二中的方法可运用到城市实时监控管理系统、多视角机器人、安防系统、电力监控系统和实时视频会议等众多领域中。

204.基于本发明的发明构思,本发明实施例还提供一种多路视频码流实时处理系统,能够实现上述多路视频码流实时处理方法。该系统的结构如图8所示,包括实时码流接收模块81、实时码流缓存模块82、硬件解码组件83和渲染模块84;

205.实时码流接收模块81,用于并行接收各视频服务器通过关联的码流接收通道发送的实时视频码流,将接收的实时视频码流拆分为多帧数据帧,将数据帧加入所述实时码流缓存模块中的对应缓存队列,所述码流接收通道与分配的cpu内存绑定,所述码流接收通道与所述缓存队列一一对应;

206.实时码流缓存模块82,用于针对每个缓存队列,按设定间隔向所述硬件解码组件的对应硬件解码缓存区域发送数据帧;

207.硬件解码组件83,用于并行对各解码缓存区域中的数据帧进行硬件解码,将得到的解码后数据帧输送到所述渲染模块的对应渲染缓存区域;

208.渲染模块84,用于并行离屏渲染各渲染缓存区域中的解码后数据帧,得到用于播放的渲染后数据帧。

209.进一步的,上述实时码流接收模块81和实时码流缓存模块82为利用cpu资源运行的模块;硬件解码组件83和渲染模块84为利用gpu资源运行的模块。

210.基于本发明的发明构思,本发明实施例还提供一种多路视频码流同屏播放系统,能够实现上述多路视频码流同屏播放方法。该系统的结构如图9所示,包括实时码流接收模块91、实时码流缓存模块92、硬件解码组件93和视频显示模块94;

211.实时码流接收模块91,用于并行接收各视频服务器通过关联的码流接收通道发送的实时视频码流,将接收的实时视频码流拆分为多帧数据帧,将数据帧加入所述实时码流缓存模块中的对应缓存队列,所述码流接收通道与分配的cpu内存绑定,所述码流接收通道与所述缓存队列一一对应;

212.实时码流缓存模块92,用于针对每个缓存队列,按设定间隔向所述硬件解码组件的对应硬件解码缓存区域发送数据帧;

213.硬件解码组件93,用于并行对各解码缓存区域中的数据帧进行硬件解码,将得到的解码后数据帧输送到所述视频显示模块的对应渲染缓存区域;

214.视频显示模块94,用于根据对应子窗口的位置并行离屏渲染各渲染缓存区域中的解码后数据帧,在所述子窗口播放渲染后数据帧,实现各路实时视频码流的同屏播放。

215.进一步的,上述实时码流接收模块91和实时码流缓存模块92为利用cpu资源运行的模块;硬件解码组件93和视频显示模块94为利用gpu资源运行的模块。

216.关于上述实施例中的系统,其中各个模块执行操作的具体方式已经在有关该方法的实施例中进行了详细描述,此处将不做详细阐述说明。

217.基于本发明的发明构思,本发明实施例还提供一种终端设备,该终端设备设置有上述多路视频码流实时处理系统,或设置有上述多路视频码流同屏播放系统。

218.基于本发明的发明构思,本发明实施例还提供一种多路视频码流同屏播放系统,该系统的结构如图10所示,包括播放设备101和多路视频服务器102,播放设备101设置有上述多路视频码流同屏播放系统;

219.终端设备101用于同屏播放各路视频服务器102发送的实时视频码流。

220.基于本发明的发明构思,本发明实施例还提供了一种非临时性计算机可读存储介质,其上存储有计算机指令,当该指令被处理器执行时实现上述多路视频码流实时处理方法,或实现上述多路视频码流同屏播放方法。

221.除非另外具体陈述,术语比如处理、计算、运算、确定、显示等等可以指一个或更多个处理或者计算系统、或类似设备的动作和/或过程,所述动作和/或过程将表示为处理系统的寄存器或存储器内的物理(如电子)量的数据操作和转换成为类似地表示为处理系统的存储器、寄存器或者其他此类信息存储、发射或者显示设备内的物理量的其他数据。信息和信号可以使用多种不同的技术和方法中的任何一种来表示。例如,在贯穿上面的描述中提及的数据、指令、命令、信息、信号、比特、符号和码片可以用电压、电流、电磁波、磁场或粒子、光场或粒子或者其任意组合来表示。

222.应该明白,公开的过程中的步骤的特定顺序或层次是示例性方法的实例。基于设计偏好,应该理解,过程中的步骤的特定顺序或层次可以在不脱离本公开的保护范围的情况下得到重新安排。所附的方法权利要求以示例性的顺序给出了各种步骤的要素,并且不是要限于所述的特定顺序或层次。

223.在上述的详细描述中,各种特征一起组合在单个的实施方案中,以简化本公开。不应该将这种公开方法解释为反映了这样的意图,即,所要求保护的主题的实施方案需要清楚地在每个权利要求中所陈述的特征更多的特征。相反,如所附的权利要求书所反映的那样,本发明处于比所公开的单个实施方案的全部特征少的状态。因此,所附的权利要求书特此清楚地被并入详细描述中,其中每项权利要求独自作为本发明单独的优选实施方案。

224.本领域技术人员还应当理解,结合本文的实施例描述的各种说明性的逻辑框、模块、电路和算法步骤均可以实现成电子硬件、计算机软件或其组合。为了清楚地说明硬件和软件之间的可交换性,上面对各种说明性的部件、框、模块、电路和步骤均围绕其功能进行了一般地描述。至于这种功能是实现成硬件还是实现成软件,取决于特定的应用和对整个系统所施加的设计约束条件。熟练的技术人员可以针对每个特定应用,以变通的方式实现所描述的功能,但是,这种实现决策不应解释为背离本公开的保护范围。

225.结合本文的实施例所描述的方法或者算法的步骤可直接体现为硬件、由处理器执行的软件模块或其组合。软件模块可以位于ram存储器、闪存、rom存储器、eprom存储器、eeprom存储器、寄存器、硬盘、移动磁盘、cd-rom或者本领域熟知的任何其它形式的存储介质中。一种示例性的存储介质连接至处理器,从而使处理器能够从该存储介质读取信息,且

可向该存储介质写入信息。当然,存储介质也可以是处理器的组成部分。处理器和存储介质可以位于asic中。该asic可以位于用户终端中。当然,处理器和存储介质也可以作为分立组件存在于用户终端中。

226.对于软件实现,本技术中描述的技术可用执行本技术所述功能的模块(例如,过程、函数等)来实现。这些软件代码可以存储在存储器单元并由处理器执行。存储器单元可以实现在处理器内,也可以实现在处理器外,在后一种情况下,它经由各种手段以通信方式耦合到处理器,这些都是本领域中所公知的。

227.上文的描述包括一个或多个实施例的举例。当然,为了描述上述实施例而描述部件或方法的所有可能的结合是不可能的,但是本领域普通技术人员应该认识到,各个实施例可以做进一步的组合和排列。因此,本文中描述的实施例旨在涵盖落入所附权利要求书的保护范围内的所有这样的改变、修改和变型。此外,就说明书或权利要求书中使用的术语“包含”,该词的涵盖方式类似于术语“包括”,就如同“包括,”在权利要求中用作衔接词所解释的那样。此外,使用在权利要求书的说明书中的任何一个术语“或者”是要表示“非排它性的或者”。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。