1.本发明属于遥感图像处理技术领域,具体涉及一种辐射计信号处理机的数字相关处理方法及装置。

背景技术:

2.辐射计,又称“放射计”,是一种测量电磁辐射的辐射通量的装置,通过被动的接收各个空间高度的热电辐射信号来完成目标探测、测量温湿度等任务。其最早进入工程实用阶段是在上世纪三十年代左右,当时国外的科研人员使用辐射计主要是为了射电天文和大气观测等方面的研究。目前,辐射计已经广泛应用在社会生产生活的多个领域,根据所观测的具体对象不同,应用领域可以大致的分为气象监测(例如温度监测与预报)、农林预报(例如森林火灾预警与病虫害监测等)、地质勘测(例如矿物分布和河流流向等)和军事应用(地表物体识别和隐身飞行物识别等)等领域。

3.辐射计中核心部件为信号处理机,信号处理机用于完成信号采集、数字正交下变频、幅相补偿、相关等处理操作。其中,相关处理是指利用信号的相关特性将有用信号从干扰和噪声中提取出来的过程,它是辐射计信号处理中非常重要的一个步骤。最初的复相关器是由模拟器件构成的,主要包括功分器单元、复相关器单元和积分视放单元,天线接收到的信号经过功分器单元处理后得到中频模拟信号,中频模拟信号再由复相关器单元进行相关处理,最后再由积分视放单元处理得到最终的输出。由于复相关器单元是由两个乘法器构成,因此随着天线单元的增长所需要乘法器的个数会呈指数级增长,继而积分视放单元的数目也会随之增多,系统的复杂性极大的增大,重量和功耗也会显著增长,因此模拟相关器在实际应用中存在诸多弊端。

4.现有辐射计数字相关技术的改进方案,包括在数字域运用延时相关的方法来减少信号处理的相关次数从而降低系统复杂度,以及利用asic技术降低数字相关器的功耗等多种基于不同改进角度的实例,但是这些方案始终存在着以下不足:采用延时相关的方法会一定程度上降低信噪比;数字相关器asci设计的除降低功耗之外的其他优化性能尚未得到验证,而且相关研究的后端设计也比较缺乏,算法迭代不方便。因此,随着数字技术的飞速发展,现有辐射计在精度、速率和灵活使用性能方面难以满足实际应用的需求。

技术实现要素:

5.有鉴于此,本发明提供了一种辐射计信号处理机的数字相关处理方法及装置,能够利用的数字相关技术进行复相关计算完成辐射计中信号的数字相关处理。

6.本发明提供的一种辐射计信号处理机的数字相关处理方法,包括:

7.步骤1、将信号经过数模转换得到m路中频实信号,对所述m路中频实信号进行下变频处理得到m路零中频复信号;对所述m路零中频复信号进行幅相一致性补偿校正,得到补偿校正后的m路复信号;

8.步骤2、将所述m路复信号同时进行两两之间的互相关操作及每路信号的自相关操

作,得到m*(m-1)/2 m路相关信号;再对所述m*(m-1)/2 m路相关信号各自进行连续的累加时间长度内的累加得到m*(m-1)/2 m路累加时间长度为δt的相关计算结果;

9.步骤3、根据窗口长度对m*(m-1)/2 m路的相关计算结果进行滑动窗口累加得到窗口累加结果;再根据输出帧频对所述窗口累加结果进行采样完成帧频调整,得到数字相关处理的结果。

10.进一步地,所述步骤2中将所述m路复信号同时进行两两之间的互相关操作及每路信号的自相关操作,得到m*(m-1)/2 m路相关信号,计算过程如下:

[0011][0012]

其中,yi(t)与yj(t)分别表示参与相关计算的第i路和第j路通道号,v(i,j) 表示相关计算的计算结果。

[0013]

进一步地,所述窗口长度由相关总时长t除以累加时间长度δt得到。

[0014]

进一步地,所述步骤3中根据窗口长度对m*(m-1)/2 m路的相关计算结果进行滑动窗口累加得到窗口累加结果,具体过程为:将每一路δt内的相关计算结果逐个排列,以每个δt内的相关计算结果为所述窗口长度内的单元格,对所述窗口长度内的单元格作加法运算,计算结果作为当前窗口长度的滑窗处理结果,窗口每次滑动一个单元格。

[0015]

本发明提供的一种辐射计信号处理机的数字相关处理装置,包括数据接收模块、数字下变频模块、幅相补偿模块、相关计算模块、滑窗处理模块和通信模块;

[0016]

其中,所述数据接收模块,用于接收adc采集到的天线的m路中频实信号;所述数字下变频模块,用于对所述数据接收模块采集到的m路中频实信号作下变频ddc处理,得到m路零中频复信号;所述幅相补偿模块,用于对m 路零中频复信号作幅相一致性补偿校正得到m路复信号;所述相关计算模块,用于对所述m路复信号进行两两作互相关操作、对所述m路复信号的每路作自相关操作,并对相关结果作δt时间长度的累加,得到m*(m-1)/2 m个相关时间长度为δt的相关计算结果;所述滑窗处理模块,用于根据相关总时长与输出帧频对m*(m-1)/2 m个相关计算结果进行滑动窗口累加与帧频调整,得到最终相关计算结果;所述通信模块,用于输出所述最终相关计算结果。

[0017]

进一步地,所述幅相补偿模块,能够根据设定的幅相补偿信息对m路零中频复信号作幅相一致性补偿校正。

[0018]

进一步地,所述滑窗处理模块根据相关总时长与输出帧频对 m*(m-1)/2 m个相关计算结果进行滑动窗口累加与帧频调整的方式为:将每一路δt内的相关计算结果逐个排列,以每个δt内的相关计算结果为所述窗口长度内的单元格,对所述窗口长度内的单元格作加法运算,计算结果作为当前窗口长度的滑窗处理结果,窗口每次滑动一个单元格。

[0019]

进一步地,所述数字相关处理装置采用fpga芯片实现。

[0020]

有益效果:

[0021]

1、本发明通过采集处理m路通道中频信号,将模拟信号高速的转化为数字信号,再对m路高速数字信号作并行数字相关处理,得到m*(m-1)/2 m路相关计算输出结果,能够实现利用的数字相关技术进行复相关计算就能有效的解决系统复杂性的问题,具备高时间分辨率多通道采集,同时可实现相关时间长度与输出帧频灵活可控,有效的增加的辐射计的精度、速度指标与灵活适用性能。

[0022]

2、本发明提出采用fpga芯片完成数字相关计算,充分利用了fpga芯片所具有的功能强大、逻辑速度快、功耗低及可移植性强等优势,在实现多路高速率信号处理的同时,能够灵活改变相关时长和输出帧频,进一步提高了辐射计的精度、处理速度指标与灵活使用性能。

附图说明

[0023]

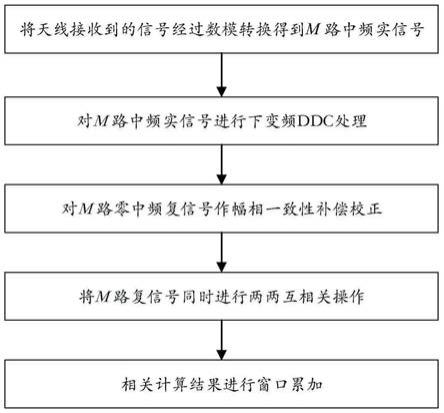

图1为本发明提供的一种辐射计信号处理机的数字相关处理方法的流程图。

[0024]

图2为本发明提供的一种辐射计信号处理机的数字相关处理方法中相关计算过程的示意图。

[0025]

图3为本发明提供的一种辐射计信号处理机的数字相关处理方法中滑窗处理过程的示意图。

[0026]

图4为本发明提供的一种辐射计信号处理机的数字相关处理装置的结构图。

[0027]

图5为本发明提供的一种辐射计信号处理机的数字相关处理装置的滑窗处理模块的实现结构示意图。

具体实施方式

[0028]

下面结合附图并举实施例,对本发明进行详细描述。

[0029]

本发明提供的一种辐射计信号处理机的数字相关处理方法及装置,其核心思想是:通过对采集得到的m路通道中频信号进行下变频处理得到零中频复信号,再对零中频复信号进行补偿校正,然后对校正后的信号进行数字相关处理,在此基础上进行滑动窗口累加后按照输出帧频进行采样,从而完成信号的数字相关处理。

[0030]

本发明提供的一种辐射计信号处理机的数字相关处理方法,流程如图1所示,具体包括以下步骤:

[0031]

步骤1、将天线接收到的信号经过数模转换得到m路中频实信号。

[0032]

辐射计信号处理机包含m个相互独立的高时间分辨率的采集通道,每一数据采集通道采集中频模拟信号并转换为高速数字信号传给fpga。

[0033]

步骤2、对步骤1得到的m路中频实信号进行下变频ddc处理,得到m 路零中频复信号。

[0034]

步骤3、根据设定的幅相补偿信息对m路零中频复信号作幅相一致性补偿校正,得到补偿校正后的m路复信号。其中,幅相补偿信息可以为上位机下发的具体参数。

[0035]

步骤4、将补偿校正后得到的m路复信号同时进行两两之间的互相关操作,以及每路信号的自相关操作,得到m*(m-1)/2 m路相关信号;再对 m*(m-1)/2 m路相关信号各自进行连续的设定的累加时间长度内的累加,设定的累加时间长度记为δt,由此得到m*(m-1)/2 m路累加时间长度为δt的相关计算结果。计算过程如图2所示。

[0036]

具体来说,本发明中对m*(m-1)/2 m路相关信号分别进行δt时间长度上累加的过程为:以选定时间为零点开始计时,在此期间对每路信号的所有采样点逐一进行累加,当记录时长达到δt时,当前的累加结果即为该路信号在δt的累加时间长度内的信号输出,然后当前记录的时间清零,再从零点重新计时,开始下一轮的以δt作为累加时间长度的信号累加,以此类推直至信号终止或处理结束。

[0037]

步骤4中对于m路通道的零中频复信号的相关计算过程,可表示为如下公式:

[0038][0039]

其中,δt为累加时间长度,yi(t)与yj(t)分别表示参与相关计算的第i路和第j路通道号,v(i,j)表示相关计算的计算结果。

[0040]

步骤5、根据累加时间长度δt和相关总时长t计算出累加的窗口长度,对步骤4输出的m*(m-1)/2 m路的相关计算结果进行滑动窗口累加;再根据输出帧频对所有的窗口累加结果进行采样完成帧频调整,输出数字相关处理的结果。

[0041]

步骤5的处理过程如图3所示。即将m*(m-1)/2 m路的相关计算结果中每一路δt的累加时间长度的计算输出结果逐个排列,每个δt的累加时间长度的相关计算结果作为滑窗窗口累加中窗口长度内的单元格,窗口长度为相关总时长t除以δt得到的数值,窗口内的单元格作加法运算输出当前窗口的滑窗处理结果,窗口每次滑动一个单元格。由此可知窗口输出结果的帧频为δt,再根据需要的输出帧频对该输出结果进一步作采用处理即可得到最终满足相关总时长与输出帧频要求的结果。

[0042]

现有技术中,最初的复相关器是由模拟器件构成的,主要包括功分器单元、复相关器单元和积分视放单元,天线接收到的信号经过功分器单元处理后得到中频模拟信号,中频模拟信号再由复相关器单元进行相关处理,最后再由积分视放单元处理得到最终的输出。

[0043]

本发明提供的一种辐射计信号处理机的数字相关处理装置,如图4所示,包括adc数据接收模块、ddc数字下变频模块、幅相补偿模块、相关计算模块、滑窗处理模块和通信模块。

[0044]

其中,adc数据接收模块,用于接收adc采集到的天线的m路中频实信号。

[0045]

ddc数字下变频模块,用于对adc数据接收模块采集到的m路中频实信号作下变频ddc处理,得到m路零中频复信号。

[0046]

幅相补偿模块,用于根据上位机下发的幅相补偿信息对m路零中频复信号作幅相一致性补偿校正。

[0047]

相关计算模块,用于对幅相补偿后的m路复信号两两作互相关、每路作自相关并对结果作δt时间长度的累加,得到m*(m-1)/2 m个相关时间长度为δt 的相关计算结果。

[0048]

滑窗处理模块,用于根据上位机下发的相关时间长度与输出帧频对 m*(m-1)/2 m个相关计算结果作进一步的自加积累与帧频调整。

[0049]

通信模块,用于将相关运算结果上传至上位机进行后续的反演运算。

[0050]

其中,相关计算模块的处理过程如图2所示,采用如下公式对于m路通道的零中频复信号的相关计算:

[0051][0052]

其中,δt为累加时间长度,yi(t)与yj(t)分别表示参与相关计算的第i路和第j路通道号,v(i,j)表示相关计算的计算结果。

[0053]

滑窗处理模块的处理过程如图3所示。将m*(m-1)/2 m路的每一路δt时间长度计算输出结果逐个排列,每个δt时间长度的相关计算结果组成了滑窗处理中的最小单元格,

窗的长度为相关计算总时长t除以δt得到的数值,窗内单元格作加法运算并输出,窗口每次滑动一个单元格。可知窗口输出结果的帧频为δt,根据所需求的输出帧频对该输出结果进一步作抽取处理即可得到最终满足相关时长与输出帧频要求的结果。

[0054]

随着数字技术的飞速发展,辐射计的实现使对精度、速率和灵活使用性能具备越来越高的要求,这些要素也成为衡量辐射计性能的关键性指标。鉴于 fpga具备的功能强大、逻辑速度快、功耗低及可移植性强的优势,通过综合改进,本发明提出的数字相关处理方法采用fpga芯片完成数字相关计算,最终在实现多路高速率信号处理的同时,能够灵活改变相关时长和输出帧频,辐射计的精度、处理速度指标与灵活使用性能也得到了有效提高。

[0055]

采用fpga芯片完成数字相关计算,每两路信号做互相关运算,每一路信号做自相关运算,共得到m*(m-1)/2 m个计算结果,每个计算结果作δt时长的积累并输出至滑窗处理模块;滑窗处理模块根据上位机下发的相关时长与输出帧频指令对δt时长的相关计算结果作进一步积累与输出帧频转换。

[0056]

滑窗处理模块在fpga上的实现结构示意图,如图5所示。将 m*(m-1)/2 m路的每一路δt时间长度计算输出结果分为两个信号支路,其中一个信号支路作为减法器的被减数数据输入。另一个信号支路存储在存储器中,经与相关总时长相同时间的延迟后读出,读出的延迟数据作为减法器的减数数据输入。减法器输出的数据作为累加器输入的数据,累加器输出得到滑窗处理的输出数据,由输出帧频产生信号抽取使能信号,在信号抽取使能的上升沿时刻存储当前滑窗处理输出数据,并作为相关计算与滑窗处理的最终输出数据。两路信号先做差后累加的结构与两路信号先分别累加后做差的结构相比,避免了累加器一直累加引起的数据溢出,同时也节省了一个累加器资源。

[0057]

实施例:

[0058]

本实施例是本发明提供的一种辐射计信号处理机的数字相关处理装置的具体实施方式,具体内容如下:

[0059]

本发明应用于包含1片xilinx公司的virtex-7系列fpga芯片和4片高速adc芯片的信号处理机,每片adc芯片可分为4个1ghz采样率的信号通道,共组成15个信号通道与1个备用通道,其中fpga中信号处理的时钟为 250mhz。15路1gsps高速采样信号在fpga内经ddc下变频转换为15路 250msps低速零中频复信号,15路复信号经过幅相补偿处理后进行相关运算,得到120个相关时间长度为10ms的相关运算结果。将每个10ms相关运算结果作为最小单元窗格,滑窗模块对相关运算顺序输出的最小单元窗格作进一步的累加,本实例支持10ms~10s时间内任意10ms的整数倍时间的总相关时长。滑窗模块每10ms输出一次累加相关结果,根据设置的输出帧频抽取后得到最终输出相关结果,本实例支持1~50hz的输出帧频。

[0060]

综上所述,以上仅为本发明的较佳实施例而已,并非用于限定本发明的保护范围。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。