led芯片及其制备方法

技术领域

1.本发明涉及半导体技术领域,具体而言,涉及led芯片及其制备方法。

背景技术:

2.gan基led具有发光效率高、节能、环保、寿命长、体积小等优点,基于led的半导体照明被认为是最有可能替代传统照明的新型固态冷光源。近年来超高效率led芯片的研究备受研究人员青睐,进一步提高gan基led芯片的发光效率是半导体照明替代传统照明的关键因素。

3.众所周知,高反射率pn型欧姆接触电极,可解决了金属电极吸光引起的光损耗问题,但是高质量的低欧姆接触在algan/gan照明器件中目前仍是一大难题。

4.目前,在led电极蒸镀技术中,因高反射率材料,如al、ag与n-gan无法实现很好的欧姆接触,底层多采用功函数相对低的ti材料,但是这也带来了电极反射率的降低,电极反射率降低5%-10%。

5.现有技术中,例如申请号为202020874738.1的专利文件公布了一种提高外量子效率的led芯片的制作方法,采用al电极作为底层接触电极,该专利公布在点测电流为60ma情况下,电压提高了0.019v,亮度提高了3.76%。但是,该专利技术未对电极与半导体间的欧姆接触进行改善。

6.有鉴于此,特提出本发明。

技术实现要素:

7.本发明的第一目的在于提供一种led芯片,所述led芯片的发光结构中,在第一半导体和/或第二半导体成表面掺杂一定浓度的第一杂质,进而可有效降低第一电极和/或第二电极的接触电阻,提高电极基层与第一半导体层和/或第二半导体层的欧姆接触,尤其是高反射率电极材料(例如al、ag和铜)与半导体层的欧姆接触。并且,该电极结构适用于正装或倒装的led芯片,均可以提高提高电极基层与第一半导体层和/或第二半导体层的欧姆接触。

8.本发明的第二目的在于提供一种led芯片的制备方法,该方法在刻蚀得到台阶区后,沉积电子阻挡层和电流扩展层,采用含第一掺杂杂质的气体对第一半导体层进行处理,得到具有一定厚度的第一电极接触层从而提高电极基层与第一半导体层的欧姆接触。并在沉积第一电极和第二电极之前,对待沉积表面进行酸洗,去除表面氧化物,提高电极接触层表面的洁净度,避免由于氧化物的绝缘作用导致的金属电极层与半导体层欧姆接触不良的情况。

9.本发明的第三目的在于提供另一种led芯片的制备方法,该方法在刻蚀得到台阶区后,采用含第一掺杂杂质的气体对第一半导体层和第二半导体层进行处理,得到具有一定厚度的第一电极接触层和第二电极接触层,从而提高电极基层与第一半导体层和第二半导体层的欧姆接触。并在沉积第一电极和第二电极之前,对待沉积表面进行酸洗,去除表面

氧化物,提高电极接触层表面的洁净度,避免由于氧化物的绝缘作用导致的金属电极层与半导体层欧姆接触不良的情况。

10.为了实现本发明的上述目的,特采用以下技术方案:

11.本发明所提供的一种led芯片,所述led芯片包括沉积于衬底表面的具有mesa台阶的发光结构,所述发光结构包括第一半导体层、多量子阱层和第二半导体层,至少一第一电极设置于所述mesa台阶的所述第一半导体层上,至少一第二电极设置于所述第二半导体层上;

12.所述第一半导体层含有第一掺杂杂质,所述第二半导体层含有第二掺杂杂质,所述第一掺杂杂质与所述第二掺杂杂质不同;

13.所述第一电极与所述第一半导体层的接触面处的所述第一掺杂杂质的浓度大于所述第一半导体层中所述第一掺杂杂质的浓度;

14.和/或;

15.所述第二电极与所述第二半导体层的接触面处的所述第一掺杂杂质的浓度大于所述第二半导体层中所述第二掺杂杂质的浓度。

16.本发明所提供的一种led芯片的制备方法,包括以下步骤:

17.(a)、提供一衬底,在所述衬底上沉积发光结构,所述发光结构包括依次第一半导体层、多量子阱层、第二半导体层;其中,所述第一半导体层含有第一掺杂杂质,所述第二半导体层含有第二掺杂杂质;

18.(b)、从上至下依次刻蚀所述第二半导体层、多量子阱层直至暴露出部分所述第一半导体层,得到mesa台阶;

19.(c)、在所述第二半导体层上依次沉积电子阻挡层和电流扩展层;

20.(d)、采用含第一掺杂杂质的气体对所述发光结构进行处理,从所述mesa台阶处的所述第一半导体层的上表面至所述衬底的方向上,得到具有一定厚度的第一电极接触层;

21.(e)、在所述第一电极接触层上沉积第一电极;在所述电流扩展层上沉积第二电极。

22.本发明所提供的另一种led芯片的制备方法,包括以下步骤:

23.(a)、提供一衬底,在所述衬底上沉积发光结构,所述发光结构包括依次第一半导体层、多量子阱层、第二半导体层;其中,所述第一半导体层含有第一掺杂杂质,所述第二半导体层含有第二掺杂杂质;

24.(b)、从上至下依次刻蚀所述第二半导体层、多量子阱层直至暴露出部分所述第一半导体层,得到mesa台阶;

25.(c)、采用含第一掺杂杂质的气体对所述发光结构进行处理,从所述mesa台阶处的所述第一半导体层的上表面至所述衬底的方向上,得到具有一定厚度的第一电极接触层;从所述第二半导体层的上表面至所述衬底的方向上,得到具有一定厚度的第二电极接触层;

26.(d)、在所述第二半导体层上依次沉积电子阻挡层和电流扩展层;

27.(e)、在所述第一电极接触层上沉积第一电极;在所述电流扩展层上沉积第二电极;

28.其中,所述第二半导体层上表面设置有掺杂浓度大于所述第二掺杂杂质的浓度的

第一掺杂杂质。

29.与现有技术相比,本发明的有益效果为:

30.(1)本发明所提供的led芯片,所述led芯片的发光结构中,在第一半导体和/或第二半导体成表面掺杂一定浓度的第一杂质,进而可有效降低第一电极和/或第二电极的接触电阻,提高电极基层与第一半导体层和/或第二半导体层的欧姆接触,尤其是高反射率电极材料(例如al、ag和铜)与半导体层的欧姆接触。

31.(2)本发明所提供的led芯片,所述led芯片的发光结构中,在第一半导体和/或第二半导体成表面形成具有一定厚度的第一电极接触层和/或第二电极接触层,提高电极基层与第一半导体层和/或第二半导体层的欧姆接触,尤其是高反射率电极材料(例如al、ag和铜)与半导体层的欧姆接触。

32.(3)本发明所提供的一种led芯片的制备方法,该方法在刻蚀得到台阶区后,采用含第一掺杂杂质的气体对第一半导体层和/或第二半导体层进行处理,得到具有一定厚度的第一电极接触层和/或第二电极接触层,从而提高电极基层与第一半导体层和/或第二半导体层的欧姆接触。

33.(4)本发明所提供的一种led芯片的制备方法,在沉积第一电极和第二电极之前,对待沉积的表面进行酸洗,去除表面氧化物,提高电极接触层表面的洁净度,避免由于氧化物的绝缘作用导致的金属电极层与半导体层欧姆接触不良的情况,从而提高led芯片的亮度。

附图说明

34.为了更清楚地说明本发明具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

35.图1为本发明实施例所提供的发光结构示意图;

36.图2为本发明实施例所提供的蚀刻后的发光结构形成mesa台阶示意图;

37.图3为本发明实施例所提供的制备电子阻挡层和电流扩展层的示意图;

38.图4为本发明实施例所提供的含si气体处理的示意图;

39.图5为本发明又一实施例所提供的含si气体处理的示意图;

40.图6为本发明又一实施例所提供的制备电子阻挡层和电流扩展层的示意图;

41.图7为本发明实施例所提供的沉积第一电极和第二电极后的示意图;

42.图8为本发明实施例1所提供的正装led芯片俯视图;

43.图9为本发明图8沿a-a方向的剖视图;

44.图10为本发明酸洗处理步骤示意图;

45.图11为本发明实施例2所提供的倒装led芯片俯视图;

46.图12为本发明图11沿a-a方向的剖视图;

47.图13为本发明实施例3所提供的倒装led芯片俯视图;

48.图14为本发明图13沿a-a方向的剖视图;

49.图15为第一电极的结构示意图;

50.图16为本发明实施例4所提供的正装led芯片俯视图;

51.图17为本发明图16沿a-a方向的剖视图;

52.图18为本发明实施例所提供的含c气体处理的示意图;

53.图19为本发明实施例5所提供的倒装led芯片俯视图;

54.图20为本发明图19沿a-a方向的剖视图;

55.图21为本发明实施例6所提供的倒装led芯片俯视图;

56.图22为本发明图21沿a-a方向的剖视图;

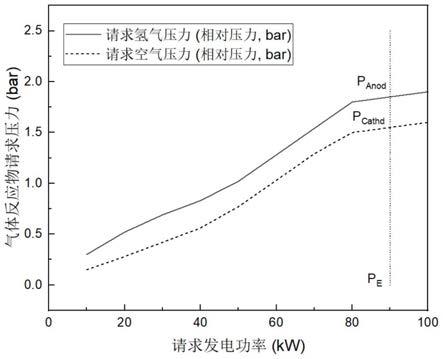

57.图23为本发明实验例1中含si气体处理前后硅浓度的对比图;

58.图24为本发明实验例2中电压数据的对比图;

59.图25为本发明实验例2中led芯片的亮度数据对比图。

60.附图标记:

61.10-衬底;20-第一半导体层;201-mesa台阶;

62.202-第一电极接触层202a-第一表面202b-第二表面;

63.21-多量子阱层;22-第二半导体层;221-第二电极接触层;

64.221a-第三表面;221b-第四表面;30-电子阻挡层;

65.40-电流扩展层;50-iso隔离槽;61-p-finger电极;

66.611-p-finger垫电极;612-p-finger第一延伸电极;613-p-finger第二延伸电极;

67.62-n-finger电极;621-n-finger垫电极;

68.622-n-finger第一延伸电极;623-n-finger第二延伸电极;

69.62a-基层;62b-缓冲层;62c-保护层;

70.62d-连接层;63-掩膜层;70-第一绝缘层;

71.71-第二绝缘层;81-p-pad电极;82-n-pad电极;

72.91-p-metal电极;92-n-metal电极。

具体实施方式

73.下面将结合附图和具体实施方式对本发明的技术方案进行清楚、完整地描述,但是本领域技术人员将会理解,下列所描述的实施例是本发明一部分实施例,而不是全部的实施例,仅用于说明本发明,而不应视为限制本发明的范围。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。实施例中未注明具体条件者,按照常规条件或制造商建议的条件进行。所用试剂或仪器未注明生产厂商者,均为可以通过市售购买获得的常规产品。

74.本发明实施例所提供的一种led芯片,可以为正装led芯片或倒装led芯片。如图1所示,包括第一半导体层20、多量子阱层21和第二半导体层22,并经过刻蚀形成具有mesa台阶201的发光结构,如图2所示。第一半导体层20掺杂有第一掺杂杂质,第二半导体层22掺杂有第二掺杂杂质,第一掺杂杂质与第二掺杂杂质不同。

75.优选地,所述第一半导体层20为n型半导体层,例如n-gan层,但不局限于此;第一掺杂杂质为n型掺杂杂质。第二半导体层22为p型半导体层,例如p-gan层,但不局限于此;第二掺杂杂质为p型掺杂杂质。如图4所示,例如采用含硅离子的气体对台阶处的第一半导体

层20,或者如图5所示,采用含硅离子的气体对台阶处的第一半导体层20和第二半导体层22进行处理。可以增加第一半导体层20表面和第二半导体层22表面第一掺杂杂质(si)的浓度。从而降低第一电极和/或第二电极的接触电阻。

76.所述第一电极与所述第一半导体层20的接触面处的所述第一掺杂杂质的浓度大于所述第一半导体层20中所述第一掺杂杂质的浓度。

77.和/或;所述第二电极与所述第二半导体层22的接触面处的所述第一掺杂杂质的浓度大于所述第二半导体层22中所述第二掺杂杂质的浓度。

78.进一步地,如图3所示,沉积电子阻挡层30和电流扩展层40;或者如图6所示,掺杂第一杂质后再进行电子阻挡层30和电流扩展层40的沉积。再如图7所示制备第一电极和第二电极。优选地,第一电极为n-finger电极62,第二电极为p-finger电极61。

79.在本发明一种优选的实施方式中,如图8和图9所示的正装led芯片的结构示意图,所述第一电极与所述第一半导体层20的接触面为第一表面202a,从所述第一表面202a至所述衬底10方向上的一定厚度的所述第一半导体层20为第一电极接触层202,所述第一半导体层20与所述第一电极接触层202的接触面为所述第一电极接触层202的第二表面202b;

80.在所述第一电极接触层202中,从所述第一表面202a至所述第二表面202b的方向上,所述第一掺杂杂质的浓度逐渐降低。

81.在本发明一种优选的实施方式中,如图16和图17所示的正装led芯片的结构示意图,所述第二电极与所述第二半导体层22的接触面为第三表面221a,定义从所述第三表面221a至所述衬底10方向上的一定厚度的所述第二半导体层22为第二电极接触层221,所述第二半导体层22与所述第二电极接触层221的接触面为所述第二电极接触层221的第四表面221b;

82.在所述第二电极接触层221中,从所述第三表面221a至所述第四表面221b的方向,所述第一掺杂杂质的浓度逐渐降低。

83.在本发明一种优选的实施方式中,所述第一表面202a中的第一掺杂杂质的浓度大于1e

20

atom/cm3。

84.进一步地,所述第一表面202a与所述第二表面202b中的第一杂质原子的浓度差为0~6e

21

atom/cm3,且不为0;更优选的浓度差为2e

20

atom/cm3~6e

21

atom/cm3,例如2e

20

atom/cm3、5e

20

atom/cm3、8e

20

atom/cm3、1e

21

atom/cm3、1e

21

atom/cm3、3e

21

atom/cm3、6e

21

atom/cm3。在本发明一种优选的实施方式中,所述第三表面221a中的第一掺杂杂质的浓度大于1e

20

atom/cm3。

85.进一步地,所述第三表面221a与所述第三表面221a中的第一杂质原子的浓度差为0~6e

21

atom/cm3,且不为0;更优选的浓度差为2e

20

atom/cm3~6e

21

atom/cm3,例如2e

20

atom/cm3、5e

20

atom/cm3、8e

20

atom/cm3、1e

21

atom/cm3、1e

21

atom/cm3、3e

21

atom/cm3、6e

21

atom/cm3。

86.在本发明一种优选的实施方式中,所述第一表面202a中的第一掺杂杂质的浓度大于所述第一电极接触层202内部第一掺杂杂质的平均浓度。

87.进一步地,所述第一电极接触层202的厚度d1为例如

优选地,

88.优选地,所述第二电极接触层221的厚度d2为例如例如例如优选地,

89.在本发明一种优选的实施方式中,所述第一掺杂杂质为n型掺杂杂质,包括c、si、ge、sn和pb中的任意一种或多种的组合,第二掺杂杂质可以为常规的p型掺杂杂质。

90.在本发明一种优选的实施方式中,如图15所示,所述第一电极从下至上依次包括基层62a、缓冲层62b和保护层62c;

91.其中,所述基层62a包括al或ag;

92.优选地,所述缓冲层62b包括tipt、tini、nipt和tial中的至少一种;

93.优选地,所述保护层62c包括au、al和alti中的至少一种。

94.在本发明一种优选的实施方式中,所述led芯片还包括位于所述第一电极之上并与所述第一电极电性连接的第一上电极,所述第一电极还包括与所述第一上电极直接接触的连接层62d;

95.和/或;所述led芯片还包括位于所述第二电极之上并与所述第二电极电性连接的第二上电极,所述第二电极还包括与所述第二上电极直接接触的连接层62d;

96.优选地,所述连接层62d包括ti和pt中的至少一种。

97.在本发明一种优选的实施方式中,所述第二电极与所述第二半导体层22之间还设置有电子阻挡层30和电流扩展层40。

98.本发明所提供的一种led芯片的制备方法,可以实现上述led芯片所具有的结构组成,包括以下步骤:

99.(a)、如图1所示,提供一衬底10,在所述衬底10上沉积发光结构,所述发光结构包括依次第一半导体层20、多量子阱层21、第二半导体层22;其中,所述第一半导体层20含有第一掺杂杂质,所述第二半导体层22含有第二掺杂杂质。

100.(b)、如图2所示,从上至下依次刻蚀所述第二半导体层22、多量子阱层21直至暴露出部分所述第一半导体层20,得到mesa台阶201。

101.(c)、如图3所示,在所述第二半导体层22上依次沉积电子阻挡层30和电流扩展层40。

102.(d)、如图4所示,采用含第一掺杂杂质的气体对所述发光结构进行处理,从所述第一台阶处的所述第一半导体层20的上表面至所述衬底10的方向上,得到具有一定厚度的第一电极接触层202。

103.优选地,所述含第一掺杂杂质的气体包括含c气体、含si气体、含ge气体、含pb气体中的任意一种或多种。

104.更优选地,含第一掺杂杂质的气体可以是包含杂质的原子形态或离子形态的气体,例如sih4、sih2cl2、sicl4、sif4、co2、co、ch4、geh4、c8h

20

pb等。

105.例如,如图18所示,采用单独的含c气体进行处理。更优选地,可以是含c气体和含si气体的混合气体。

106.(e)、常规地进行掩膜的沉积,并在所述第一电极接触层202上沉积第一电极;在所

述电流扩展层40上沉积第二电极。

107.或者,另一实施例提供了一种制备方法,具体包括以下步骤:

108.(a)、如图1所示,提供一衬底10,在所述衬底10上沉积发光结构,所述发光结构包括依次第一半导体层20、多量子阱层21、第二半导体层22;其中,所述第一半导体层20含有第一掺杂杂质,所述第二半导体层22含有第二掺杂杂质。

109.(b)、如图2所示,从上至下依次刻蚀所述第二半导体层22、多量子阱层21直至暴露出部分所述第一半导体层20,得到mesa台阶201。

110.(c)、如图4所示,采用含第一掺杂杂质的气体对所述发光结构进行处理,从所述第一台阶处的所述第一半导体层20的上表面至所述衬底10的方向上,得到具有一定厚度的第一电极接触层202;从所述第二半导体层22的上表面至所述衬底10的方向上,得到具有一定厚度的第二电极接触层221。

111.优选地,所述含第一掺杂杂质的气体包括含c气体、含si气体、含ge气体、含sn气体和含pd气体中的任意一种或多种。

112.更优选地,含第一掺杂杂质的气体可以是包含杂质的原子形态或离子形态的气体,例如sih4、sih2cl2、sicl4、sif4、co2、co、ch4、geh4、c8h

20

pb等。

113.例如,如图18所示,采用单独的含c气体进行处理。更优选地,可以是含c气体和含si气体的混合气体。

114.进一步地,常规制备电子阻挡层30和电流扩展,如图6所示。

115.(d)、如图7所示,常规地进行掩膜的沉积,并在所述第一电极接触层202上沉积第一电极;在所述第二电极接触层221上沉积第二电极。

116.其中,所述第二半导体层22上表面设置有掺杂浓度大于所述第二掺杂杂质的浓度的第一掺杂杂质。

117.在本发明一种优选的实施方式中,所述第一电极接触层202与所述第一电极相接触的表面为第一表面202a,与所述第一半导体层20相接触的表面为第二表面202b,所述第一表面202a的第一掺杂杂质的浓度大于所述第二表面202b的第一掺杂杂质的浓度;

118.和/或;所述第二电极接触层221与所述第二电极相接触的表面为第三表面221a,与所述第二半导体层22相接触的表面为第四表面221b,所述第三表面221a的第一掺杂杂质的浓度大于所述第四表面221b的第一掺杂杂质的浓度。

119.在本发明一种优选的实施方式中,所述采用含第一掺杂杂质的气体对所述发光结构进行处理,具体包括:采用含c气体、含si气体、含ge气体和含pb气体中的任意一种或多种对所述第一半导体层20和/或所述第二半导体层22进行射频轰击处理和/或离子刻蚀处理,通过射频轰击处理和/或离子刻蚀处理,杂质沉积在半导体层表面,并随着处理时间的增加,表面处的第一掺杂杂质浓度的增加,原子或离子向下扩散,第一半导体层20和/或第二半导体层22从上表面往下一定厚度内形成具有浓度递减的第一电极接触层202和/或第二电极接触层221。

120.在本发明一种优选的实施方式中,可以通过处理时间,调节第一电极接触层202和/或第二电极接触层221的厚度以及浓度变化,所述处理的时间为50~2000s,例如50s、100s、200s、500s、1000s、1200s、1500s、1800s、2000s。

121.在本发明一种优选的实施方式中,在步骤(c)之后、在步骤(d)之前,即在掩膜层63

沉积并做开口处理之后、电极沉积之前,如图10所示,还包括:先采用酸性溶液对含第一掺杂杂质的气体处理后的表面进行清洗,再采用水进行清洗,去除表面氧化物,提高电极接触层表面的洁净度,避免由于氧化物的绝缘作用导致的金属电极层与半导体层欧姆接触不良的情况。

122.在本发明一种优选的实施方式中,所述酸性溶液包括但不限于boe(缓冲氧化物刻蚀液)和/或盐酸溶液。

123.实施例1

124.参考图8和图9所示的正装led芯片的结构示意图,包括:

125.衬底10、第一半导体层20、多量子阱层21、第二半导体层22,刻蚀得到mesa台阶201,常规制备电子阻挡层30和电流扩展层40后,采用含si气体进行处理后,在第一半导体层20得到一定厚度的第一电极接触层202,常规地进行掩膜的沉积,并在所述第一电极接触层202上沉积第一电极;在所述电流扩展层40第二电极接触层221上沉积第二电极。

126.沉积第一绝缘层70,即pv保护层62c。

127.图8为俯视图,可以具体看到n-finger电极包括:n-finger垫电极621以及n-finger第一延伸电极622和n-finger第二延伸电极623;p-finger电极61包括:p-finger垫电极611以及p-finger第一延伸电极612和p-finger第二延伸电极613。

128.实施例2

129.参考图11和图12所示的倒装led芯片的结构示意图,包括:

130.衬底10、第一半导体层20、多量子阱层21、第二半导体层22,刻蚀得到mesa台阶201,常规制备电子阻挡层30和电流扩展后,采用含si气体进行处理后,在第一半导体层20得到一定厚度的第一电极接触层202,刻蚀形成iso隔离槽50。

131.沉积掩摸,刻蚀后,采用酸性溶液对刻蚀后裸露的表面进行清洗,然后沉积p-finger电极61和n-finger电极62,n-finger电极62的基层62a为al。沉积第一绝缘层70,刻蚀后沉积焊盘层(p-pad电极81和n-pad电极82),形成dbr结构。

132.实施例3

133.参考图13和图14所示的倒装led芯片的结构示意图,在实施例2的基础上,在p-finger电极61和n-finger电极62的基础上,沉积第二电极层,即p-metal电极91和n-metal电极,然后沉积第二绝缘层71,刻蚀后沉积焊盘层(p-pad电极81和n-pad电极82),形成odr结构。

134.实施例4

135.参考图16和图17所示的正装led芯片的结构示意图,包括:

136.衬底10、第一半导体层20、多量子阱层21、第二半导体层22,刻蚀得到mesa台阶201,经过含si气体处理后,分别在第一半导体层20和第二半导体层22得到一定厚度的第一电极接触层202和第二电极接触层221,并进一步常规制备电子阻挡层30和电流扩展层40,在第一电极接触层202和电流扩展层40分别沉积第一电极和第二电极。

137.沉积第一绝缘层70,即pv保护层62c。

138.图16为俯视图,可以具体看到n-finger电极61包括:n-finger垫电极621以及n-finger第一延伸电极622和n-finger第二延伸电极623;p-finge电极包括:p-finger垫电极611以及p-finger第一延伸电极612和p-finger第二延伸电极613。

139.实施例5

140.参考图19和图20所示的倒装led芯片的结构示意图,包括:

141.衬底10、第一半导体层20、多量子阱层21、第二半导体层22,刻蚀得到mesa台阶201,经过含si气体处理后,分别在第一半导体层20和第二半导体层22得到一定厚度的第一电极接触层202和第二电极接触层221,并进一步常规制备电子阻挡层30和电流扩展层40,刻蚀形成iso隔离槽50。

142.沉积掩摸,刻蚀后,采用酸性溶液对刻蚀后裸露的表面进行清洗,然后沉积p-finger电极61和n-finger电极62,n-finger电极62的基层62a为al。沉积第一绝缘层70,刻蚀后沉积焊盘层(p-pad电极81和n-pad电极82),形成dbr结构。

143.实施例6

144.参考图21和图22所示的倒装led芯片的结构示意图,在实施例2的基础上,在p-finger电极61和n-finger电极62的基础上,沉积第二电极层,即p-metal电极91和n-metal电极92,然后沉积第二绝缘层71,刻蚀后沉积焊盘层(p-pad电极81和n-pad电极82),形成odr结构。

145.实施例7

146.与实施例2基本相同,不同的是采用含c气体对第一半导体层20进行处理。

147.实施例8

148.与实施例4基本相同,不同的是采用含c气体对第一半导体层20和第二半导体层22进行处理。

149.实验例1处理后的第一半导体层的杂质离子浓度测试

150.base组:第一半导体层20和第二半导体无任何处理的常规mesa台阶201。

151.实验组:实验组为在base组的基础上,采用含硅气体对第一半导体层20进行处理。

152.测试方法:将上述base组和实验组的两个样片制作均无图形,直接对发光结构进行轰击,轰击后样品真空打样进行smis分析。

153.测试结果如图23所示,实验组中,第一半导体层20表面的硅离子的浓度在第一表面202a处的浓度最高,明显高于base组的表面,随着检测深度的不断增加,从第一表面202a自上而下方向,即从第一表面202a到第二表面202b的方向上,硅的浓度逐渐降低,与base组差异越来越小。

154.本实施例中含硅气体的处理时间为200s,该时间处理下,如图23所示,base组与实验组浓度差异最大范围在

155.实验例2 led芯片电压对比和亮度对比结果

156.实验组:实施例2所提供的倒装led芯片结构。

157.base组:与实施例2相比,不采用含硅气体对第一半导体层20进行处理的半导体结构。

158.测试方法:测试芯片为常规dbr倒装芯片,芯片尺寸为14*32mil,电性测试电流为65ma,矽电倒装测试机,反射率采用u-3900分光光谱仪。采用同一外延机台,同一炉同一圈发光结构,分为实验组和base进行测试,除本技术提到的处理外,其他工艺流程都同时作业。

159.base组在icp刻蚀后及finger电极沉积前,不经过含si气体的处理以及酸洗处理,

第一电极的基层62a为cr18a,然后再连接al层,电极反射率只有78%。实验组的第一电极的基层62a为al,不需要cr18a层进行连接,电极的反射率可以达到89%。除上述差异外,制程端不存在任何差异,片源为同run同圈发光结构,可忽略外延差异导致的亮度差异。

160.从图24和图25可知,采用本发明所提供的方法进行处理后,芯片cot亮度提高3%左右,电压降低0.01v。

161.此外,当采用其他杂质(例如c、ge和pb)对第一半导体层20进行处理时,也可以在一定厚度的第一半导体层20内形成具有杂质浓度梯度的第一接触层,从而实现高反电极与半导体的欧姆接触。

162.另外,在对第一半导体层20和第二半导体层22同时进行处理时,可以同时实现欧姆接触,实现高反电极与半导体的接触,避免电压太高。

163.综上,通常高反射率电极,例如al,通常需要采用cr作为底层(例如base组),反射率也只能达到78%。但是,采用本技术所提供的发光结构,在第一半导体层20和/或第二半导体层22分别得到一定厚度的第一电极接触层202和/或第二电极接触层221,可以直接采用al作为电极基层62a,反射率可以达到89%以上。

164.尽管已用具体实施例来说明和描述了本发明,然而应意识到,以上各实施例仅用以说明本发明的技术方案,而非对其限制;本领域的普通技术人员应当理解:在不背离本发明的精神和范围的情况下,可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围;因此,这意味着在所附权利要求中包括属于本发明范围内的所有这些替换和修改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。