处理基为模6为零点数dft的方法、设备、装置及存储介质

技术领域

1.本发明涉及通信技术领域,尤其涉及一种处理基为模6为零点数离散傅里叶变换(dft)的方法、设备、装置及存储介质。

背景技术:

2.nr(new radio)系统为由第三代合作伙伴计划(3rd generation partnership project,3gpp)主导的第五代移动通信系统(5g),其中涉及离散傅里叶变换扩频的正交频分复用多址接入(dft-s-ofdm)的调制技术,这需要采用多个点数的、非2指数次幂的傅里叶变换处理器。

3.但是,在满足5g的超低时延特性以及资源消耗尽可能少等要求的情形下,非2指数次幂的傅里叶变换处理器比较难以实现。

技术实现要素:

4.本发明解决的技术问题是非2指数次幂的傅里叶变换处理器比较难以实现等问题。

5.为解决上述技术问题,本发明实施例提供一种处理基为模6为零点数离散傅里叶变换的方法,包括:

6.基于素因子算法将6倍数点分解,从而获得如下基于若干个系数的第一分解式和第二分解式:

[0007][0008][0009]

其中,m为系数的个数,n为模6为零点数,第一分解式中n为离散傅里叶变换中输入数据的序并且大于或等于0而小于n,ni为序n的系数并且具有相应的取值范围,ai为与ni对应的第一分解参数,第二分解式中k为离散傅里叶变换中输出数据的序并且大于或等于0而小于n,ki为k的系数并且具有相应的取值范围,bi为与ki对应的第二分解参数;

[0010]

分别将系数n0至nm的可取值个数作为小点数基而进行m 1轮运算,在每轮运算中,进行小点数基离散傅里叶变换而得到计算结果,其中,各系数的取值满足第一分解式;

[0011]

将计算结果作为每轮中的输出数据而存储于存储器的存储地址,其中,存储地址包括存储块号和相对存储地址,其通过如下公式选择:

[0012][0013][0014]

其中,bank_sel为存储块号,bank_addr为相对存储地址,ci和di分别为第一调节参数和第二调节参数;

[0015]

基于第二分解式获取离散傅里叶变换的最终输出数据。

[0016]

可选地,上述方法包括,存储器接收并且存储离散傅里叶变换的初始输入数据以

及每轮运算中的输出数据,在第一轮运算中获取初始输入数据而进行小点数基离散傅里叶变换,在后续各轮运算中获取前一轮运算的输出数据而作为该轮运算的输入数据以进行小点数基离散傅里叶变换。

[0017]

可选地,上述方法包括将每轮运算中的输出数据存储于该轮运算中输入数据所存储的存储地址。

[0018]

可选地,上述方法包括,在每轮运算中,使可取值个数作为小点数基的系数在其取值范围内取值,使其余系数中的部分系数在其范围内取值和/或乒乓取值,并且遍历其余系数中的剩余系数以进行小点数基离散傅里叶变换,从而得到计算结果。

[0019]

可选地,在存储块号的计算公式中,取值范围为2、3、5的系数所对应的第一调节参数分别为3、2、1。

[0020]

可选地,相对存储地址的计算公式包括关于n0至nm的多项,其中,第一个取值范围为2的系数所对应的第二调节参数为0,第一个取值范围为3的系数所对应的第二调节参数为0,第一个不为0的第二调节参数为1,其余不为0的第二调节参数为其前面紧邻的、第二调节参数不为0的项中相应系数可取值的个数与相应第二调节参数的乘积。

[0021]

可选地,基于第二分解式获取离散傅里叶变换的最终输出数据包括,基于第二分解式获取k的系数的取值,基于k的系数的取值获取对应的n的系数的取值,基于n的系数的取值、存储块号的计算公式和相对存储地址的计算公式计算输出数据的存储地址,以及基于存储地址获取最终输出数据。

[0022]

本发明实施例还提供一种处理离散傅里叶变换的设备,包括存储器和处理模块,存储器适于接收并且存储离散傅里叶变换的初始输入数据以及每轮运算中的输出数据,处理模块适于执行上述处理基为模6为零点数离散傅里叶变换的方法的步骤。

[0023]

可选地,上述设备包括于网络设备或者用户设备。

[0024]

可选地,处理模块包括处理单元,其适于执行1个5点或2个3点或3个2点离散傅里叶变换。

[0025]

本发明实施例还提供一种存储介质,其上存储有计算机指令,计算机指令运行时执行上述处理基为模6为零点数离散傅里叶变换的方法的步骤。

[0026]

本发明实施例还提供一种处理基为模6为零点数离散傅里叶变换的装置,包括:

[0027]

分解模块,其适于基于素因子算法将6倍数点分解,从而获得如下基于若干个系数的第一分解式和第二分解式:

[0028][0029][0030]

其中,m为系数的个数,n为模6为零点数,第一分解式中n为离散傅里叶变换中输入数据的序并且大于或等于0而小于n,ni为序n的系数并且具有相应的取值范围,ai为与ni对应的第一分解参数,第二分解式中k为离散傅里叶变换中输出数据的序并且大于或等于0而小于n,ki为k的系数并且具有相应的取值范围,bi为与ki对应的第二分解参数;

[0031]

运算模块,其适于分别将系数n0至nm的可取值个数作为小点数基而进行m 1轮运算,在每轮运算中,进行小点数基离散傅里叶变换而得到计算结果,其中,各系数的取值满足第一分解式;

[0032]

存储模块,其适于将计算结果作为每轮中的输出数据而存储于存储器的存储地址,其中,存储地址包括通过如下公式确定的存储块号和相对存储地址:

[0033][0034][0035]

其中,bank_sel为存储块号,bank_addr为相对存储地址,ci和di分别为第一调节参数和第二调节参数;

[0036]

获取模块,其适于基于第二分解式获取离散傅里叶变换的最终输出数据。

[0037]

可选地,存储模块适于接收并且存储离散傅里叶变换的初始输入数据以及每轮运算中的输出数据,在第一轮运算中获取初始输入数据而进行小点数基离散傅里叶变换,在后续各轮运算中获取前一轮运算的输出数据而作为该轮运算的输入数据以进行小点数基离散傅里叶变换。

[0038]

可选地,存储模块适于将每轮运算中的输出数据存储于该轮运算中输入数据所存储的存储地址。

[0039]

可选地,运算模块适于在每轮运算中,使可取值个数作为小点数基的系数在其取值范围内取值,使其余系数中的部分系数在其范围内取值和/或乒乓取值,并且遍历其余系数中的剩余系数以进行小点数基离散傅里叶变换,从而得到计算结果。

[0040]

可选地,获取模块适于:基于第二分解式获取k的系数的取值,基于k的系数的取值获取对应的n的系数的取值,基于n的系数的取值、存储块号的计算公式和相对存储地址的计算公式计算输出数据的存储地址,以及基于存储地址获取最终输出数据。

[0041]

与现有技术相比,本发明实施例的技术方案具有以下有益效果。

[0042]

例如,在本发明的实施例中,对于基为模6为零点数离散傅里叶变换,将6倍数点分解,从而获得基于若干个系数的第一分解式和第二分解式,分别将各个系数的可取值个数作为小点数基而进行m 1轮运算,并且将计算结果作为每轮中的输出数据而存储于存储器的存储地址,从而获取离散傅里叶变换的最终输出数据;该技术方案可以极大地降低dft实现的复杂度,显著地减少对计算和存储资源的消耗,并且有效地满足5g关于超低时延特性的要求。

[0043]

又例如,在本发明的实施例中,存储器包括多个存储块(bank),而存储块号通过bank_sel选择;这可以增大运算的并发度,从而显著地减少处理时间,降低运算时延。

[0044]

又例如,在本发明的实施例中,将每轮运算中的输出数据存储于该轮运算中输入数据所存储的存储地址,使得在离散傅里叶变换的过程中存储器的存储地址被同址使用,从而使得存储地址能够高效地复用。

附图说明

[0045]

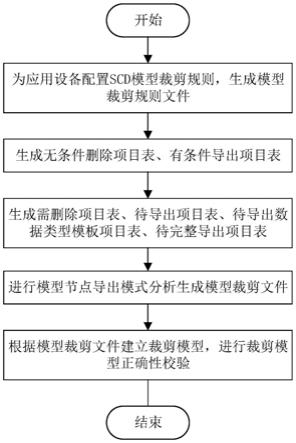

图1为本发明实施例中处理基为模6为零点数离散傅里叶变换的方法的流程图;

[0046]

图2为本发明实施例中处理离散傅里叶变换的设备的结构示意图;

[0047]

图3为本发明实施例中处理基为模6为零点数离散傅里叶变换的装置的结构示意图。

具体实施方式

[0048]

为了使本发明的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

[0049]

图1示出了本发明实施例一种处理基为模6为零点数离散傅里叶变换的方法100的流程图。

[0050]

离散傅里叶变换可以通过如下公式表示:

[0051][0052]

其中,n为点数,n和k均在0至n-1之间取值,x(n)为离散傅里叶变换的输入数据,x(k)为离散傅里叶变换的输出数据。

[0053]

在本发明的实施例中,n为模6为零点数。

[0054]

具体而言,5g nr标准的dft-s-ofdm技术中离散傅里叶变换的点数具有多种,其中的一部分为模6为0的点数(即6的倍数),有14种,包括:6、18、30、54、90、150、162、270、450、486、750、810、1350、1458。

[0055]

方法100包括步骤110、120、130和140。

[0056]

在步骤110的执行中,可以基于素因子算法将6倍数点分解。

[0057]

具体而言,根据素因子算法(pfa),n可以被分解为互素的二个数,即n=n1n2,其中,n1和n2互素;并且,n、k可以通过如下公式表示:

[0058][0059][0060][0061]

n1和n2中的至少一者仍可以继续分解,直至分解的因子仅包括5、3、2。此时,n被分解,从而获得基于若干个系数的第一分解式和第二分解式,分别通过如下公式(4)和(5)表示:

[0062][0063][0064]

其中,m为系数的个数,n为模6为零点数,n为离散傅里叶变换中输入数据的序并且大于或等于0而小于n,ni为序n的系数并且具有相应的取值范围,ai为与ni对应的第一分解参数,k为离散傅里叶变换中输出数据的序并且大于或等于0而小于n,ki为k的系数并且具有相应的取值范围,bi为与ki对应的第二分解参数。

[0065]

系数n0到nm分别为所分解的各因子的索引,系数n0到nm的取值范围分别与对应因子的数值相关,例如,系数ni对应的因子为i,则ni的取值范围为0至i-1。

[0066]

在本发明的实施例中,可以按照因子5、3、2的先后顺序进行分解,以使得分解的步骤简化而有效。

[0067]

在步骤120的执行中,可以分别将系数n0至nm的可取值个数作为小点数基而进行m 1轮运算;在每轮运算中,进行小点数基离散傅里叶变换而得到计算结果,其中,各系数的取值满足第一分解式。

[0068]

在每轮运算中,可以使可取值个数作为小点数基的系数在其取值范围内取值,使其余系数中的部分系数在其范围内取值和/或乒乓取值。

[0069]

小点数基离散傅里叶变换包括如下三种情形。

[0070]

在情形一下,于第ni轮运算中,ni在其取值范围(0至p-1)内取值,除ni之外的其余系数中,可以取出系数nq(其取值范围为0至q-1)的值,从而实现一次做q个基为p的小点数离散傅里叶变换。

[0071]

在情形二下,于第ni轮运算中,ni在其取值范围(0至p-1)内取值,除ni之外的其余系数中,可以通过乒乓方式取系数nr的值,从而实现一次做2个基为p的小点数离散傅里叶变换。

[0072]

在情形三下,于第ni轮运算中,ni在其取值范围(0至p-1)内取值,除ni之外的其余系数中,可以取出系数ns(其取值范围为0至s-1)的值、并且通过乒乓方式取系数nt的值,从而实现一次做2s个基为p的小点数离散傅里叶变换。

[0073]

接着,遍历其余系数中的剩余系数以进行小点数基离散傅里叶变换,从而得到计算结果。

[0074]

在具体实施中,对其余系数中的剩余系数,可以通过嵌套循环(例如基于for语句的嵌套循环)覆盖剩余系数中各个系数取值的所有组合方式。

[0075]

可以通过处理模块进行小点数基离散傅里叶变换。

[0076]

在具体实施中,处理模块可以包括执行1个5点或2个3点或3个2点离散傅里叶变换的处理单元。

[0077]

通过该处理单元的设置,使得小点数基离散傅里叶变换的处理过程有序并且简化。

[0078]

在步骤130的执行中,可以将计算结果作为每轮中的输出数据而存储于存储器的存储地址。

[0079]

存储器接收和存储离散傅里叶变换的初始输入数据x(n);每轮运算中的输出数据也回传到存储器进行存储,并且作为下一轮运算的输入数据。

[0080]

可以将每轮运算中的输出数据存储于该轮运算中输入数据所存储的存储,以进行同址回写,在一轮运算结束后,n个数据都完成了更新,从而使得存储地址能够高效地复用。

[0081]

在第一轮运算中从存储器获取初始输入数据x(n)而进行小点数基离散傅里叶变换;在后续各轮运算中获取前一轮运算的输出数据以作为该轮运算的输入数据,从而进行小点数基离散傅里叶变换。

[0082]

存储器可以包括一个、二个或多个,例如,设置二个或者多个存储器以用于乒乓取值。

[0083]

每个存储器可以包括多个存储块,例如,6个存储块;这可以增大运算的并发度,从而显著地减少处理时间,降低运算时延。

[0084]

可以将计算结果作为每轮中的输出数据而存储于存储器的存储地址,其中,存储地址包括存储块号和相对存储地址,可以通过如下公式选择:

[0085][0086][0087]

其中,bank_sel为存储块号,bank_addr为相对存储地址,ci和di分别为第一调节参数和第二调节参数。

[0088]

可以基于设置规则确定第一调节参数和第二调节参数。

[0089]

在一些实施例中,公式(6)中取值范围为2、3、5的系数所对应的第一调节参数分别为3、2、1;公式(7)中关于系数n0至nm的多项可以按照n0、n1、

……

、nm的顺序从前向后排列,其中,第一个取值范围为2的系数所对应的第二调节参数为0,第一个取值范围为3的系数所对应的第二调节参数为0,第一个不为0的第二调节参数为1,其余不为0的第二调节参数为其前面紧邻的、第二调节参数不为0的项中相应系数可取值的个数与相应第二调节参数的乘积。

[0090]

通过设置第一调节参数和第二调节参数,可以使得数据能够分散存储于存储器中,避免了数据存储时的地址冲突。

[0091]

在步骤140的执行中,可以基于第二分解式获取离散傅里叶变换的最终输出数据x(k)。

[0092]

具体而言,k可以在0至n-1之间取值,基于k的各个取值,根据第二分解式(即公式(5))获取k的系数的取值。

[0093]

在离散傅里叶变换中,由于k的系数与n的系数具有对应关系,因此,基于k的系数的取值可以获取对应的n的系数的取值。

[0094]

基于n的系数的取值、存储块号的计算公式(即公式(6))和相对存储地址的计算公式(即公式(7))计算输出数据的存储地址,以及基于存储地址获取最终输出数据x(k)。

[0095]

以下描述基为1350离散傅里叶变换的运算过程。

[0096]

可以基于素因子算法将1350按照5、3、2的先后顺序进行分解,即,1350=5*5*3*3*3*2;系数n0到n5分别为因子5、5、3、3、3、2的索引,对应的取值范围分别为0至4、0至4、0至2、0至2、0至2、0至1。

[0097]

序n和k可以通过如下公式表示:

[0098]

n=(270n0 54n1 450n2 150n3 50n4 675n5)mod1350

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(8)

[0099]

k=(1026k0 1080k1 1000k2 300k3 900k4 675k5)mod1350

ꢀꢀꢀꢀ

(9)

[0100]

其中,n0的取值范围为0至4,n1的取值范围为0至4,n2的取值范围为0至2,n3的取值范围为0至2,n4的取值范围为0至2,n5的取值范围为0至1;k0的取值范围为0至4,k1的取值范围为0至4,k2的取值范围为0至2,k3的取值范围为0至2,k4的取值范围为0至2,k5的取值范围为0至1。

[0101]

可以设置6个存储块以进行并发运算。

[0102]

如前文所述,可以通过设置规则确定存储块号的计算公式和相对存储地址的计算公式中的第一调节参数和第二调节参数;基为1350时,离散傅里叶变换中存储块号和相对存储地址可以通过如下公式选择:

[0103]

bank_sel=(3n5 2n4 2n3 2n2 n1 n0)mod6

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(10)

[0104]

bank_addr=0n5 75n4 25n3 0n2 5n1 n0

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(11)

[0105]

需要经过6轮(依次从n0轮到n5轮)以完成基为1350离散傅里叶变换的运算。

[0106]

在n0轮,取n0的5个值0到4,从而实现一次进行1个基为5离散傅里叶变换的并行运算。

[0107]

具体而言,通过如下方式对n5、n4、n3、n2、n1的5个值进行遍历选取:

[0108][0109]

在如上{}处,基于n0而取出5个值进行基为5离散傅里叶变换,共进行1350/5=270次运算,每次运算包括1个基为5离散傅里叶变换。

[0110]

将各系数(n0至n5)每次选取的值代入公式(10)和(11)而获得存储地址(包括存储块号和相对存储地址),并且将该次运算的输出数据存储于该存储地址。

[0111]

n1轮与n0轮的处理过程类似。

[0112]

在n2轮,取n2的3个值0到2,取n5的值为(0)和(1)并且进行乒乓取值,从而实现一次进行2个基为3离散傅里叶变换的并行运算。

[0113]

具体而言,通过如下方式对n4、n3、n1、n0的4个值进行遍历选取:

[0114][0115]

在如上{}处,基于n1和n5而取出2组3个值进行基为3离散傅里叶变换,共进行1350/6=225次、每次2组基为3离散傅里叶变换。

[0116]

将各系数(n0至n5)每次选取的值代入公式(10)和(11)而获得存储地址(包括存储块号和相对存储地址),并且将该次运算的输出数据存储于该存储地址。

[0117]

n3、n4轮与n2轮的处理过程类似。

[0118]

在n5轮,取n5的2个值0到1,取n2的值为(0)、(1)和(2)并且进行乒乓取值,从而实现一次进行3个基为2离散傅里叶变换的并行运算。

[0119]

具体而言,通过如下方式对n4、n3、,n1、n0的4个值进行遍历选取:

[0120][0121]

在如上{}处,基于n5和n2而取出3组2个值进行基为2离散傅里叶变换,共进行1350/6=225次、每次3组基为2离散傅里叶变换。

[0122]

将各系数(n0至n5)每次选取的值代入公式(10)和(11)而获得存储地址(包括存储块号和相对存储地址),并且将该次运算的输出数据存储于该存储地址。

[0123]

完成以上6轮运算后,可以基于第二分解式(即公式(9))获取基为1350离散傅里叶变换的最终输出数据。

[0124]

上文描述基为1350离散傅里叶变换的运算过程,应理解,基为其他模6为零点数离散傅里叶变换具有类似的运算过程。

[0125]

如前文所述,可以通过设置规则确定存储块号的计算公式和相对存储地址的计算公式中的第一调节参数和第二调节参数;基为其他模6为零点数时,离散傅里叶变换中存储块号和相对存储地址可以通过如下公式选择。

[0126]

1458点:

[0127]

bank_sel=(3n6 2n5 2n4 2n3 2n2 2n1 2n0)mod 6,

[0128]

bank_addr=0n6 81n5 27n4 9n3 3n2 n1 0n0;

[0129]

810点:

[0130]

bank_sel=(3n5 2n4 2n3 2n2 2n1 n0)mod 6,

[0131]

bank_addr=0n5 45n4 15n3 5n2 0n1 n0;

[0132]

750点:

[0133]

bank_sel=(3n4 2n3 n2 n1 n0)mod 6,

[0134]

bank_addr=0n4 0n3 25n2 5n1 n0;

[0135]

486点:

[0136]

bank_sel=(3n5 2n4 2n3 2n2 2n1 2n0)mod 6,

[0137]

bank_addr=0n5 27n4 9n3 3n2 n1 0n0;

[0138]

450点:

[0139]

bank_sel=(3n4 2n3 2n2 n1 n0)mod 6,

[0140]

bank_addr=0n4 25n3 0n2 5n1 n0;

[0141]

270点:

[0142]

bank_sel=(3n4 2n3 2n2 2n1 n0)mod 6,

[0143]

bank_addr=0n4 15n3 5n2 0n1 n0;

[0144]

162点:

[0145]

bank_sel=(3n4 2n3 2n2 2n1 2n0)mod 6,

[0146]

bank_addr=0n4 9n3 3n2 n1 0n0;

[0147]

150点:

[0148]

bank_sel=(3n3 2n2 n1 n0)mod 6,

[0149]

bank_addr=0n3 0n2 5n1 n0;

[0150]

90点:

[0151]

bank_sel=(3n3 2n2 2n1 n0)mod 6,

[0152]

bank_addr=0n3 5n2 0n1 n0;

[0153]

54点:

[0154]

bank_sel=(3n3 2n2 2n1 2n0)mod 6,

[0155]

bank_addr=0n3 3n2 1n1 0n0;

[0156]

30点:

[0157]

bank_sel=(3n2 2n1 n0)mod 6,

[0158]

bank_addr=0n2 0n1 n0;

[0159]

18点:

[0160]

bank_sel=(3n2 2n1 2n0)mod 6,

[0161]

bank_addr=0n2 n1 0n0;

[0162]

6点:

[0163]

bank_sel=(2n1 3n0)mod 6,

[0164]

bank_addr=0n1 0n0。

[0165]

本发明实施例还提供一种处理离散傅里叶变换的设备。

[0166]

在一些实施例中,处理离散傅里叶变换的设备为5g系统中的调制器,其使用dft-s-ofdm调制技术,将时域信号转换到频域进行扩展,然后再经过快速傅里叶逆变换(ifft)变换来发送信号。

[0167]

在具体实施中,处理离散傅里叶变换的设备可以包括于网络设备或者用户设备(user equipment,ue)内,而属于其中的一个部件。

[0168]

在图2所示的实施例中,处理离散傅里叶变换的设备200包括存储器和处理模块220。

[0169]

存储器可以包括一个、二个或多个。例如,包括一个存储器210,其用于接收并且存储离散傅里叶变换的初始输入数据和每轮运算中的输出数据、并且向处理模块220输出数据;还可以包括另一个存储器215,其与存储器210一起用于乒乓取值。

[0170]

每个存储器可以包括多个存储块,例如,6个存储块;这可以增大运算的并发度,从而显著地减少处理时间,降低运算时延。

[0171]

处理模块220接收存储器输出的数据,进行小点数基离散傅里叶变换,并且可以执行上述处理基为模6为零点数离散傅里叶变换方法的步骤。

[0172]

在具体实施中,处理模块220可以包括处理单元而进行小点数基离散傅里叶变换,其中,处理单元可以执行1个5点或2个3点或3个2点离散傅里叶变换。

[0173]

通过该处理单元的设置,使得小点数基离散傅里叶变换的处理过程有序并且简化。

[0174]

在具体实施中,处理离散傅里叶变换的设备内各元件及其关系都可以参考上述关

于处理基为模6为零点数离散傅里叶变换方法的描述,此处不再赘述。

[0175]

本发明实施例还提供一种存储介质,其上存储有计算机指令,该计算机指令运行时执行上述处理基为模6为零点数离散傅里叶变换方法的步骤。

[0176]

本发明实施例还提供一种处理基为模6为零点数离散傅里叶变换的装置。

[0177]

在图3所示的实施例中,处理基为模6为零点数离散傅里叶变换的装置300包括分解模块310、运算模块320、存储模块330和获取模块340。

[0178]

分解模块310可以基于素因子算法将6倍数点分解,从而获得如下基于若干个系数的第一分解式和第二分解式:

[0179][0180][0181]

其中,m为系数的个数,n为模6为零点数,第一分解式中n为离散傅里叶变换中输入数据的序并且大于或等于0而小于n,ni为序n的系数并且具有相应的取值范围,ai为与ni对应的第一分解参数,第二分解式中k为离散傅里叶变换中输出数据的序并且大于或等于0而小于n,ki为k的系数并且具有相应的取值范围,bi为与ki对应的第二分解参数。

[0182]

运算模块320可以分别将系数n0至nm的可取值个数作为小点数基而进行m 1轮运算,在每轮运算中,进行小点数基离散傅里叶变换而得到计算结果,其中,各系数的取值满足第一分解式。

[0183]

存储模块330可以将计算结果作为每轮中的输出数据而存储于存储器的存储地址,其中,存储地址包括通过如下公式确定的存储块号和相对存储地址:

[0184][0185][0186]

其中,bank_sel为存储块号,bank_addr为相对存储地址,ci和di分别为第一调节参数和第二调节参数。

[0187]

获取模块340可以基于第二分解式获取离散傅里叶变换的最终输出数据。

[0188]

在具体实施中,存储模块330可以接收并且存储离散傅里叶变换的初始输入数据以及每轮运算中的输出数据,在第一轮运算中获取初始输入数据而进行小点数基离散傅里叶变换,在后续各轮运算中获取前一轮运算的输出数据而作为该轮运算的输入数据以进行小点数基离散傅里叶变换。

[0189]

在具体实施中,存储模块330可以将每轮运算中的输出数据存储于该轮运算中输入数据所存储的存储地址。

[0190]

在具体实施中,运算模块320可以在每轮运算中,使可取值个数作为小点数基的系数在其取值范围内取值,使其余系数中的部分系数在其范围内取值和/或乒乓取值,并且遍历其余系数中的剩余系数以进行小点数基离散傅里叶变换,从而得到计算结果。

[0191]

在具体实施中,获取模块340可以基于第二分解式获取k的系数的取值,基于k的系数的取值获取对应的n的系数的取值,基于n的系数的取值、存储块号的计算公式和相对存储地址的计算公式计算输出数据的存储地址,以及基于存储地址获取最终输出数据。

[0192]

在具体实施中,处理基为模6为零点数离散傅里叶变换的装置内的各模块及其关

系都可以参考上述关于处理基为模6为零点数离散傅里叶变换方法的描述,此处不再赘述。

[0193]

在本发明的实施例中,各技术方案可以应用于3g、4g、5g系统以及未来演进的共用陆地移动通信网络(public land mobile network,plmn)等系统,其中,5g系统包括两种组网,即非独立组网(non-standalone,nsa)和独立组网(standalone,sa)。

[0194]

在本发明的实施例中,ue可以为接入终端、用户单元、用户站、移动站、移动台(mobile station,建成ms)、远方站、远程终端、移动设备、用户终端、终端设备(terminal equipment)、无线通信设备或者用户代理;ue还可以为蜂窝电话、无绳电话、会话启动协议(session initiation protocol,ip)电话、无线本地环路(wireless local loop,wll)站、个人数字处理(personal digital assistant,pda)、具有无线通信功能的手持设备、计算设备或连接到无线调制解调器的其它处理设备、车载设备、可穿戴设备,未来5g网络中的ue或者未来演进的plmn中的ue等。

[0195]

在本发明的实施例中,网络设备可以是一种部署在无线接入网(radio access network,ran)用以提供无线通信功能的装置,包括但不限于3g、4g、5g系统以及未来演进的plmn系统中提供基站功能的设备,例如在3g网络中提供基站功能的设备包括节点b(nodeb)、在4g网络中提供基站功能的设备包括演进的节点b(evolved nodeb,enb)、在无线局域网络(wireless local area networks,wlan)中提供基站功能的设备(即接入点,access point,ap)、5g nr中的提供基站功能的设备gnb、以及继续演进的节点b(ng-enb)等。

[0196]

在本发明的实施例中,处理器可以为中央处理单元(central processing unit,cpu),该处理器还可以是其他通用处理器、数字信号处理器(digital signal processor,dsp)、专用集成电路(application specific integrated circuit,asic)、现成可编程门阵列(field programmable gate array,fpga)、其他可编程逻辑器件、分立门或晶体管逻辑器件、或者分立硬件组件等。通用处理器可以是微处理器或者该处理器也可以是任何常规的处理器等。

[0197]

在本发明的实施例中,存储器可以是易失性存储器或非易失性存储器,或可包括易失性和非易失性存储器两者。其中,非易失性存储器可以是只读存储器(read-only memory,rom)、可编程只读存储器(programmable rom,prom)、可擦除可编程只读存储器(erasable prom,eprom)、电可擦除可编程只读存储器(electrically eprom,eeprom)或闪存。易失性存储器可以是随机存取存储器(random access memory,ram),其用作外部高速缓存。通过示例性但不是限制性说明,许多形式的ram可用,例如静态随机存取存储器(static ram,sram)、动态随机存取存储器(dram)、同步动态随机存取存储器(synchronous dram,sdram)、双倍数据速率同步动态随机存取存储器(double data rate sdram,ddr sdram)、增强型同步动态随机存取存储器(enhanced sdram,esdram)、同步连接动态随机存取存储器(synchlink dram,sldram)和直接内存总线随机存取存储器(direct rambus ram,dr ram)。

[0198]

在本发明的实施例中,存储介质包括u盘、移动硬盘、rom、ram、非挥发性存储器(non-volatile)、非瞬态(non-transitory)存储器、磁碟或者光盘等各种可以存储程序代码的介质。

[0199]

关于上述实施例中描述的各个装置、产品包含的各个模块/单元,其可以是软件模

块/单元,也可以是硬件模块/单元,或者也可以部分是软件模块/单元,部分是硬件模块/单元。例如,对于应用于或集成于芯片的各个装置、产品,其包含的各个模块/单元可以都采用电路等硬件的方式实现,或者,至少部分模块/单元可以采用软件程序的方式实现,该软件程序运行于芯片内部集成的处理器,剩余的(如果有)部分模块/单元可以采用电路等硬件方式实现;对于应用于或集成于芯片模组的各个装置、产品,其包含的各个模块/单元可以都采用电路等硬件的方式实现,不同的模块/单元可以位于芯片模组的同一组件(例如芯片、电路模块等)或者不同组件中,或者,至少部分模块/单元可以采用软件程序的方式实现,该软件程序运行于芯片模组内部集成的处理器,剩余的(如果有)部分模块/单元可以采用电路等硬件方式实现;对于应用于或集成于终端的各个装置、产品,其包含的各个模块/单元可以都采用电路等硬件的方式实现,不同的模块/单元可以位于终端内同一组件(例如,芯片、电路模块等)或者不同组件中,或者,至少部分模块/单元可以采用软件程序的方式实现,该软件程序运行于终端内部集成的处理器,剩余的(如果有)部分模块/单元可以采用电路等硬件方式实现。

[0200]

虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。