1.本发明关于一种半导体电路,且特别是关于一种静电放电保护电路。

背景技术:

2.随着集成电路的半导体工艺的发展,半导体元件尺寸已缩小至次微米阶段,以增进集成电路的性能以及运算速度,但元件尺寸的缩减,却出现了一些可靠度的问题,尤以集成电路对静电放电(electrostatic discharge,esd)的防护能力影响最大。当元件尺寸由于先进的工艺技术而减小,静电放电的防护能力也降低许多,结果造成元件的esd耐受力大幅降低。因此,需要静电放电保护电路来保护元件不受静电放电所损坏。然而,传统的静电放电保护电路包括一电容-电阻电路,其占用较大的面积,不利于集成电路的尺寸缩小化。

技术实现要素:

3.本发明的一实施例提供一种静电放电保护电路,可其用于一半导体元件。此半导体元件具有一第一漏/源极电极以及一第二漏/源极电极,且由一深阱包围。静电放电保护电路包括一第一控制电路以及一第一放电电路。第一控制电路电连接于半导体元件的第一漏/源极电极与一电源端之间,且具有一第一控制端。第一控制端电连接深阱,且第一控制电路产生一第一控制信号。第一放电电路电连接第一漏/源极电极与电源端之间,且受控于第一控制信号。当于第一漏/源极电极上发生一静电放电事件时,第一控制电路根据深阱的电位状态以及第一漏/源极电极的电位状态来产生第一控制信号,且第一放电电路根据第一控制信号提供介于第一漏/源极电极与电源端之间的一第一放电路径。

4.本发明的一实施例提供一种半导体电路。此半导体电路包括一半导体元件、一第一控制电路、以及一第一放电电路。半导体元件形成在一阱,且具有一第一漏/源极电极以及一第二漏/源极电极。阱由一深阱包围。阱具有一第一导电类型,且深阱具有不同于第一导电类型的一第二导电类型。静电放电保护电路包括一第一控制电路以及一第一放电电路。第一控制电路电连接于第一漏/源极电极与一电源端之间,且具有一第一控制端。第一控制端电连接深阱,且第一控制电路产生一第一控制信号。第一放电电路电连接第一漏/源极电极与电源端之间,且受控于第一控制信号。当于第一漏/源极电极上发生一静电放电事件时,第一控制电路根据深阱的一电位状态以及第一漏/源极电极的一电位状态来产生第一控制信号,且第一放电电路根据第一控制信号提供介于第一漏/源极电极与电源端之间的一第一放电路径。

附图说明

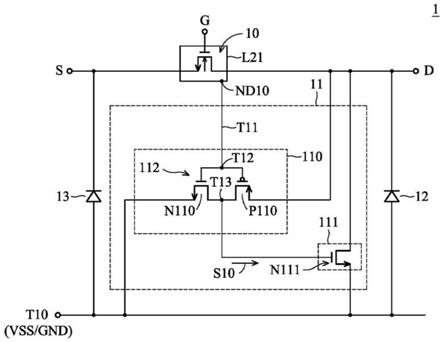

5.图1a表示根据本发明一实施例的半导体电路。

6.图1b表示根据本发明另一实施例的半导体电路。

7.图2a表示根据本发明一实施例的晶体管的结构截面图。

8.图2b表示根据本发明另一实施例的晶体管的结构截面图。

9.图3表示根据本发明另一实施例的半导体电路。

10.附图标记:

11.1:半导体电路

12.10:半导体元件

13.11:静电放电保护电路

14.12、13:二极管

15.20:衬底

16.21:n型深阱

17.22:p型阱

18.23:n型掺杂区(漏极区)

19.24:n型掺杂区(源极区)

20.25:n型掺杂区

21.26:栅极介电层

22.27:栅极层

23.28:n型掺杂区

24.110、110’:控制电路

25.111、111’:放电电路

26.112:反向器

27.113:控制电路

28.114:放电电路

29.115、300:反向器

30.ce20、ce21:接触电极

31.d:漏极电极

32.g:栅极电极

33.gnd:接地电压

34.l21:边界

35.n110、n111、n113、n114、n300:n型晶体管

36.nd10、nd11:节点

37.p110、p113、p300、p301:p型晶体管

38.s:源极电极

39.s10、s10'、s11:控制信号

40.t10:电源端

41.t11、t14:控制端

42.t12、t15、t30:输入端

43.t13、t16、t31:输出端

44.vdd:高操作电压

45.vss:低操作电压

具体实施方式

46.为使本发明的上述目的、特征和优点能更明显易懂,下文特举一较佳实施例,并配合所附图式,作详细说明如下。

47.图1a表示根据本发明一实施例的半导体电路。参阅图1a,半导体电路1包括半导体元件10、静电放电保护电路11、以及二极管12~13。在图1a的实施例中,半导体元件10为一n型晶体管,其具有栅极电极g、漏极电极d、以及源极电极s。于后文中,将以晶体管做为半导体元件10例来说明各实施例。图2a显示晶体管10的结构截面图。

48.参阅图2a,晶体管10形成在衬底20,其中,衬底20的导电类型为p型。一n型深阱21形成在衬底20中,其中,l21表示n型深阱21与衬底20之间的边界。在深阱21中,形成p型阱22以及n型掺杂区25。两n型掺杂区23与24形成在阱22中,且一栅极介电层26形成在衬底20上且介于掺杂区23与24之间。在此实施例中,n型掺杂区25在深阱21形成的位置接近n型掺杂区23。一栅极层27形成在栅极介电层26上,其中,栅极层27为一金属层或多晶硅层。掺杂区23与24以及栅极层27形成晶体管10。如图1a与图2a所示,掺杂区23作为晶体管10的漏极区,与掺杂区23电连接的接触电极作为漏极电极d。掺杂区24作为晶体管10的源极区,与掺杂区24电连接的接触电极作为源极电极s。栅极层27电连接的接触电极作为栅极电极g。在本发明实施例中,一接触电极ce20电连接掺杂区25。当半导体电路1处于正常操作模式时,一高操作电压vdd提供至接触电极ce20;当半导体电路1处于非正常操作模式时,高操作电压vdd未提供至接触电极ce20,即接触电极ce20的电位状态为浮接(floating)。根据图2a的截面图可得知,晶体管10形成在深阱21内,详细来说,晶体管10由深阱21所包围。图1a中显示边界l21,其包围晶体管10,藉以示意图2a中晶体管10与深阱21的配置关系。

49.再次参阅图1a,二极管12的阴极电连接晶体管10的漏极电极d,且其阳极电连接电源端t10。二极管13的阴极电连接晶体管10的源极电极s,且其阳极电连接电源端t10。当半导体电路1处于正常操作模式时,一低操作电压vss或一接地电压gnd提供至电源端t10(在后文中,将以低操操作电压vss为例来说明本发明个实施例);当半导体电路1处于非正常操作模式时,没有任何电压提供至电源端t10,即电源端t10的电位状态为浮接。

50.参阅图1a与图2a,静电放电保护电路11电连接漏极电极d,且包括控制电路110与放电电路111。控制电路110具有一控制端t11,其电连接接触电极ce20于节点nd10。在此实施例中,控制电路110包括反向器112。反向器112具有输入端t12以及输出端t13,且输入端t12电连接控制电路11的控制端t11。反向器112包括p型晶体管p110以及n型晶体管n110。晶体管p110的栅极电连接输入端t12,其源极电连接晶体管10的漏极电极d,且其漏极电连接输出端t13。晶体管n110的栅极电连接输入端t12,其漏极电连接输出端t13,且其源极电连接电源端t10。放电电路111包括n型晶体管n111。晶体管n111的栅极电连接反向器112的输出端t13,其漏极电连接晶体管10的漏极电极d,且其源极电连接电源端t10。基于控制电路110的电路架构与晶体管10的连接,控制电路110根据深阱21的电位状态,且基于漏极电极d的电位状态或电源端t10的电位状态来产生控制信号s10。相关叙述请参阅后文。

51.当半导体电路1处于非正常操作模式时,高操作电压vdd未提供至接触电极ce20,且没有任何电压提供至电源端t10,即接触电极ce20与电源端t10的电位状态皆为浮接。由于反向器112的输入端t12通过控制端t11与节点nd10电连接接触电极ce20,因此,输入端t12亦处于浮接状态(floating),使得晶体管p110导通而晶体管n110关闭。当于漏极电极d

上发生一静电放电事件时,漏极电极d的电位瞬间提高。通过导通的晶体管p110,输出端t13处于一高电位状态,即控制信号s10具有一高电压位。晶体管n111根据此高电压位的控制信号s10而导通,使得在漏极电极d与电源端t10之间具有一放电路径。漏极电极d上的静电电荷通过此放电路径传导至电源端t10,藉此保护耦接晶体管10的电路或元件不受静电电荷的破坏。

52.在此实施例中,当半导体电路1处于非正常操作模式且于漏极电极d上发生一静电放电事件时,由于晶体管n111导通且二极管13的连接架构(其阳极电连接电源端t10,且其阴极电连接源极电极s),另一放电路径形成于在电源端t10与源极电极s之间。因此,当漏极电极d上发生一静电放电事件时,漏极电极d上的静电电荷除了可传导至电源端t10,更可传导至源极电极s。

53.当半导体电路1处于正常操作模式时,高操作电压vdd提供至接触电极ce20且低操作电压vss提供至电源端t10,即接触电极ce20处于高电位状态,而电源端t10处于低电位状态。在正常操作模式下,由于反向器112的输入端t12通过控制端t11与节点nd10电连接接触电极ce20,输入端t12处于一高电位状态,使得晶体管n110导通而晶体管p110关闭。输出端t13则基于低操作电压vss而处于一低电位状态,即控制信号s10具有一低电压位。晶体管n111根据此低电压位的控制信号s10而关闭。在正常操作模式下,由于晶体管n111关闭,使得漏极电极d与电源端t10不具有放电路径,即阻断了前述的放电路径。

54.在其他实施例中,静电放电保护电路11也电连接源极电极s。在此实施例中,如图2b所示,在深阱21中更形成n型掺杂区28,且一接触电极ce21电连接掺杂区28。当半导体电路1处于正常操作模式时,高操作电压vdd提供至接触电极ce21;当半导体电路1处于非正常操作模式时,高操作电压vdd未提供至接触电极ce21,即接触电极ce21的电位状态为浮接。在此实施例中,n型掺杂区28在深阱21形成的位置接近n型掺杂区(源极区)24。参阅图1b,静电放电保护电路11更包括控制电路113与放电电路114。控制电路113具有一控制端t14,其电连接接触电极ce21于节点nd11。控制电路113包括反向器115。反向器115具有输入端t15以及输出端t16,且输入端t15电连接控制电路113的控制端t14。反向器115包括p型晶体管p113以及n型晶体管n113。晶体管p113的栅极电连接输入端t15,其源极电连接晶体管10的源极电极s,且其漏极电连接输出端t16。晶体管n113的栅极电连接输入端t15,其漏极电连接输出端t16,且其源极电连接电源端t10。放电电路114包括n型晶体管n114。晶体管n114的栅极电连接反向器115的输出端t16,其漏极电连接晶体管10的源极电极s,且其源极电连接电源端t10。基于控制电路113的电路架构与晶体管10的连接,控制电路113根据深阱21的电位状态,且基于源极电极s的电位状态或电源端t10的电位状态来产生控制信号s11。相关叙述请参阅后文。

55.当半导体电路1处于非正常操作模式时,高操作电压vdd未提供至接触电极ce21,且没有任何电压提供至电源端t10,即接触电极ce21与电源端t10的电位状态皆为浮接。由于反向器115的输入端t15通过控制端t14与节点nd11电连接接触电极ce21,因此,输入端t15亦处于浮接状态,使得晶体管p113导通而晶体管n113关闭。当于源极电极s上发生一静电放电事件时,源极电极s的电位瞬间提高。通过导通的晶体管p113,输出端t16处于一高电位状态,即控制信号s11具有一高电压位。晶体管n114根据此高电压位的控制信号s11而导通,使得在源极电极s与电源端t10之间具有一放电路径。源极电极s上的静电电荷通过此放

电路径传导至电源端t10,藉此保护耦接晶体管10的电路或元件不受静电电荷的破坏。

56.在此实施例中,当半导体电路1处于非正常操作模式且于源极电极s上发生一静电放电事件时,由于晶体管n114导通且二极管12的连接架构(其阳极电连接电源端t10,且其阴极电连接漏极电极d),另一放电路径形成于在电源端t10与漏极电极d之间。因此,当源极电极s上发生一静电放电事件时,源极电极s上的静电电荷除了可传导至电源端t10,更可传导至漏极电极d。

57.当半导体电路1处于正常操作模式时,高操作电压vdd提供至接触电极ce21且低操作电压vss提供至电源端t10,即接触电极ce21处于高电位状态,而电源端t10处于低电位状态。在正常操作模式下,由于反向器115的输入端t15通过控制端t14与节点nd11电连接接触电极ce21,输入端t15处于一高电位状态,使得晶体管n113导通而晶体管p113关闭。输出端t16则基于低操作电压vss而处于一低电位状态,即控制信号s11具有一低电压位。晶体管n114根据此低电压位的控制信号s11而关闭。在正常操作模式下,由于晶体管n114关闭,使得源极电极s与电源端t10不具有放电路径,即阻断了前述的放电路径。

58.在其他实施例中,与晶体管10的漏极电极d电连接的静电放电保护电路具有其他电路架构。参阅图1a与图3,与图1a比较起来,图3中静电放电电路11的控制电路110’更包括反向器300。反向器300具有输入端t30以及输出端t31,且输入端t30电连接反向器112的输出端t13。反向器300包括p型晶体管p300以及n型晶体管n300。晶体管p300的栅极电连接输入端t30,其源极电连接晶体管10的漏极电极d,且其漏极电连接输出端t31。晶体管n300的栅极电连接输入端t30,其漏极电连接输出端t31,且其源极电连接电源端t10。此外,基于控制电路110’的架构,图3中静电放电电路11的放电电路111’包括p型晶体管p301,取代了图1a的n型晶体管n111。参阅图3,晶体管p301的栅极电连接反向器300的输出端t31,其源极电连接晶体管10的漏极电极d,且其漏极电连接电源端t10。

59.参阅前文关于图1a的叙述,在非正常操作模式时,高操作电压vdd未提供至接触电极ce20,且没有任何电压提供至电源端t10,即接触电极ce20与电源端t10的电位状态皆为浮接。当于漏极电极d上发生一静电放电事件时,反向器112的输出端t13处于一高电位状态。根据输出端t13的高电位状态,晶体管n300导通,而晶体管p300关闭。通过导通的晶体管n300,输出端t31基于电源端t10的浮接状态而处于一低电压位,即控制信号s10’具有一低电压位。晶体管p301根据此低电压位的控制信号s10’而导通,使得在漏极电极d与电源端t10之间具有一放电路径。漏极电极d上的静电电荷通过此放电路径传导至电源端t10,藉此保护耦接晶体管10的电路或元件不受静电电荷的破坏。

60.在此实施例中,当半导体电路1处于非正常操作模式且于漏极电极d上发生一静电放电事件时,由于晶体管p301导通且二极管13的连接架构(其阳极电连接电源端t10,且其阴极电连接源极电极s),另一放电路径形成于在电源端t10与源极电极s之间。因此,当漏极电极d上发生一静电放电事件时,漏极电极d上的静电电荷除了可传导至电源端t10,更可传导至源极电极s。

61.同样的,参阅前文关于图1a的叙述,当半导体电路1处于正常操作模式时,高操作电压vdd提供至接触电极ce20且低操作电压vss提供至电源端t10,即接触电极ce20处于高电位状态,而电源端t10处于低电位状态。在正常操作模式下,输出端t13处于一低电位状态。根据输出端t13的低电位状态,晶体管p300导通,而晶体管n300关闭。通过导通的晶体管

p300,输出端t31基于晶体管10操作时漏极电极d的电位而处于一高电压位,即控制信号s10’具有一高电压位。晶体管p301根据此高电压位的控制信号s10’而关闭。在正常操作模式下,由于晶体管p301关闭,使得漏极电极d与电源端t10不具有放电路径,即阻断了前述的放电路径。

62.根据上述各实施例,本发明的静电放电保护电路不具有已知技术所采用的一电容-电阻电路,因此占用较小的面积。

63.虽然本发明已以较佳实施例揭露如上,然其并非用以限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作更动与润饰,因此本发明的保护范围当视申请专利范围所界定者为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。