1.本发明涉及红外焦平面阵列的读出电路技术领域,具体涉及一种红外焦平面像素级数字化读出电路及读出方法。

背景技术:

2.红外读出电路是红外探测器的重要组成部分,其作用一是提供探测像元需要的偏置电压,二是将探测阵列的信息逐行逐列地有序输出。随着读出电路的技术不断发展,读出电路集成的功能也越来越多,如片上模数转换、片上非均匀性校正等功能。其中,片上模数转换分为芯片级、列级及像素级,目前红外读出电路多采用列级模数转换通道,逐行地对阵列信号进行模数转换。

3.随着红外探测器应用场景的多样化,对红外探测器的集成度和智能化提出了进一步要求,像素级数字化得到了众多关注。像素级数字化即在像素内部完成模数转换;像素直接输出数字码。像素级数字化意味着焦平面上所有像素同时积分和模数转换,可以大大提高红外读出电路的输出帧频。

4.像素级数字化读出电路在大面阵、高帧频的发展趋势下,短时间内会产生大量数据,但是,读出电路输出传输速度存在瓶颈,大量含有探测信息的数据无法及时地从像素级数字化读出电路中输出。

技术实现要素:

5.本发明提供一种红外焦平面像素级数字化读出电路及读出方法,具有可以进行数据压缩的电路结构,在探测器端从根本上减小像素级数字化产生的数据量。

6.本发明通过下述技术方案实现:

7.一种红外焦平面像素级数字化读出电路,包括为参考像元提供偏置电压的所述参考探测电桥以及为相邻所述参考像元的旁像元提供偏置电压的所述探测电桥矩阵,

8.所述探测电桥矩阵包括若干个独立设置的探测电桥支路,任一所述探测电桥支路可分别通过开关与所述参考探测电桥构成电桥结构;

9.所述参考探测电桥独立工作,所述参考探测电桥将含有探测信息的电流输送到所述运放复用电路;所述参考探测电桥非独立工作时,将所述探测电桥支路与所述参考探测电桥的电流之差输送到所述运放复用电路;

10.还包括运放复用电路和信号锁存电路,

11.所述运放复用电路可以在电容跨导放大器模式和比较器模式之间进行切换;电容跨导放大器模式对所述参考探测电桥或所述探测电桥矩阵输出的电流进行积分;比较器模式对积分电压和斜坡电压进行比较,并将结果作为锁存使能信号输出给所述信号锁存电路,所述信号锁存电路的锁存信号为bitx信号。

12.本技术方案中,参考像元的读出数据可以根据参考探测电桥的探测电流得到,而参考像元旁边的旁像元的读出数据则根据探测电桥矩阵和参考探测电桥的电流差得到,通

过只传送差值序列,从而减少数据的传输,达到压缩数据的目的。

13.作为优化,所述参考探测电桥包括第一盲像元rb、第一pmos晶体管mp

eb

、第一nmos晶体管mn

sel

、第二nmos晶体管mn

fid

、第一探测像元rs、第三开关s3和第四开关s4,所述第一盲像元rb的一端与第一偏置电压vsk连接,所述第一盲像元rb的另一端与所述第一pmos晶体管mp

eb

的源极连接,所述第一pmos晶体管mp

eb

的漏极与所述第一nmos晶体管mn

sel

的漏极连接,所述第一nmos晶体管mn

sel

的源极与所述第二nmos晶体管mn

fid

的漏极连接,所述第二 nmos晶体管mn

fid

的漏极通过所述第三开关s3与所述第二nmos晶体管mn

fid

的栅极连接,所述第二nmos晶体管mn

fid

的栅极通过所述第四开关s4与第二偏置电压v

fid

连接,所述第二nmos 晶体管mn

fid

的源极与所述第一探测像元rs的一端连接,所述第一探测像元rs的另一端与电源地gnd连接,所述第一pmos晶体管mp

eb

的栅极与第三偏置电压v

eb

连接。

14.作为优化,所述参考探测电桥的输出端为所述第一nmos晶体管mn

sel

的漏极,所述参考探测电桥独立工作时,设置在所述参考探测电桥与所述探测电桥矩阵之间的开关断开,所述运放复用电路的输入电流值的大小为流过所述第一盲像元rb电流和流过所述第一探测像元rs电流之间的差。

15.作为优化,所述探测电桥矩阵包括若干个结构相同的探测电桥支路,所述探测电桥支路包括第二盲像元r

bi

、第二pmos晶体管mp

ebi

、第三nmos晶体管mn

seli

、第四nmos晶体管mn

fidi

、第二探测像元r

si

、第一开关s1i和第二开关s2i,所述第二盲像元r

bi

的一端与所述第一偏置电压vsk连接,所述第二盲像元r

bi

的另一端与所述第二pmos晶体管mp

ebi

的源极连接,所述第二pmos晶体管mp

ebi

的漏极与所述第三nmos晶体管mn

seli

的漏极连接,所述第三nmos晶体管mn

seli

的源极与所述第四nmos晶体管mn

fidi

的漏极连接,所述第四nmos晶体管mn

fidi

的源极连接到所述第二探测像元r

si

的一端连接,所述第二探测像元r

si

的另一端与所述电源地gnd 连接,所述第二pmos晶体管mp

ebi

的栅极通过所述第一开关s1i与所述第一pmos晶体管mp

eb

的栅极连接,所述第四nmos晶体管mn

fidi

的栅极通过所述开关s2i连接到所述第二nmos晶体管mn

fid

的栅极。

16.作为优化,所述探测电桥支路的输出端为所述第三nmos晶体管mn

seli

的漏极,所述参考探测电桥非独立工作时,设置在所述参考探测电桥与所述探测电桥矩阵之间的开关闭合,所述运放复用电路的输入电流值的大小为流过所述第二探测像元r

si

和流过所述第一探测像元rs的电流之差。

17.作为优化,所述运放复用电路包括运算放大器opamp、积分电容c、复位开关rst、第五开关s5、第六开关s6、第七开关s7、第八开关s8、第九开关s9、第十开关s

int1

和第十一开关s

int2

,所述参考探测电桥的输出端通过所述第十开关s

int1

与所述运算放大器opamp的反向输入端连接,所述探测电桥矩阵的输出端通过所述第十一开关s

int2

与所述运算放大器opamp的反向输入端连接,所述运算放大器opamp的同相输入端通过所述第八开关s8与第九开关s9 分别与参考电压v

ref

和斜坡电压v

ramp

相连,所述积分电容c与所述复位开关rst并联在所述运算放大器opamp的反相输入端和输出端之间,所述积分电容c与所述复位开关rst的并联链路与所述运算放大器opamp的输出端连接的一端通过所述第五开关s5与所述参考电压v

ref

连接,同时,所述积分电容c与所述复位开关rst的并联链路与所述运算放大器opamp的输出端之间设有所述第六开关s6,所述运算放大器opamp的输出端与所述信号锁存电路通过所述第七开关s7连接。

18.本发明还提供了一种红外焦平面像素级数字化读出方式,运用上述的读出电路,包括如下步骤:

19.步骤1、所述运放复用电路对所述参考探测电桥独立工作时的输出电流i

int

(t)进行积分,然后再进行模数转换,并通过所述信号锁存电路依次转换出n位数字码;

20.步骤2、所述运放复用电路对所述参考探测电桥非独立工作时的输出电流i

inti

(t)进行积分,然后再进行模数转换,并通过所述信号锁存电路依次转换出m位数字码,m、n均为正整数,且m≤n;

21.步骤3、调节bitx信号和模数转换的比较次数以调节m的数值大小,使所述参考探测电桥非独立工作时的输出电流i

inti

(t)的积分所转换的数字码的每位数不全为1。

22.作为优化,所述运放复用电路包括运算放大器opamp、积分电容c、复位开关rst、第五开关s5、第六开关s6、第七开关s7、第八开关s8、第九开关s9、第十开关s

int1

和第十一开关s

int2

,所述参考探测电桥的输出端通过所述第十开关s

int1

与所述运算放大器opamp的反向输入端连接,所述探测电桥矩阵的输出端通过所述第十一开关s

int2

与所述运算放大器opamp的反向输入端连接,所述运算放大器opamp的同相输入端通过所述第八开关s8与第九开关s9 分别与参考电压v

ref

和斜坡电压v

ramp

相连,所述积分电容c与所述复位开关rst并联在所述运算放大器opamp的反相输入端和输出端之间,所述积分电容c与所述复位开关rst的并联链路与所述运算放大器opamp的输出端连接的一端通过所述第五开关s5与所述参考电压v

ref

连接,同时,所述积分电容c与所述复位开关rst的并联链路与所述运算放大器opamp的输出端之间设有所述第六开关s6,所述运算放大器opamp的输出端与所述信号锁存电路通过所述第七开关s7连接。

23.作为优化,所述步骤1中,所述运放复用电路对所述参考探测电桥独立工作时的输出电流i

int

(t)进行积分具体为:将所述第六开关s6、所述第八开关s8、第十开关s

int1

闭合,将所述第五开关s5、所述第七开关s7、所述第九开关s9和第十一开关s

int2

断开,使得所述运放复用电路中的积分电容c对所述参考探测电桥的输出电流进行积分;

24.步骤2中,所述运放复用电路对所述参考探测电桥非独立工作时的输出电流i

inti

(t)进行积分具体为:将所述第六开关s6、所述第八开关s8、第十一开关s

int2

闭合,将所述第五开关s5、所述第七开关s7、所述第九开关s9和第十开关s

int1

断开,使得所述运放复用电路中的积分电容c对所述探测电桥矩阵的输出电流和参考探测电桥的输出电流之差进行积分。

25.作为优化,所述步骤1和步骤2中,所述运放复用电路对积分后的电流进行模数转换具体为:所述第六开关s6和所述第八开关s8断开,所述第五开关s5、所述第七开关s7和所述第九开关s9闭合,将积分电容c的积分电压和斜坡电压进行比较。

26.本发明与现有技术相比,具有如下的优点和有益效果:

27.本发明减少了读出电路模数转换的数据量,缓解了读出电路大数据量高速输出的问题,此外基于多通道位串行转换,对差值的模数转换中,比较次数可变,即信息压缩后的数字码位数可变,具有灵活性,可有效避免像素间探测信号差异过大或很小,压缩位数固定造成的溢出或压缩位数浪费的问题。

附图说明

28.为了更清楚地说明本发明示例性实施方式的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本发明的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。在附图中:

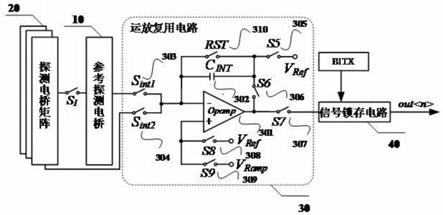

29.图1是本发明一个实施例的像素级数字化读出电路的整体结构示意图。

30.图2是本发明一个实施例的参考探测电桥和探测电桥矩阵的电路示意图。

具体实施方式

31.为使本发明的目的、技术方案和优点更加清楚明白,下面结合实施例和附图,对本发明作进一步的详细说明,本发明的示意性实施方式及其说明仅用于解释本发明,并不作为对本发明的限定。

32.实施例

33.在成像探测中,同一场景下相邻像元具有连续变化、突变较少的特点,可知相邻像素值具有相关性。本发明先选定某一位置上的像元作为参考像元(第一探测像元rs),对其探测信息进行处理及模数转换,而附近的其他像元(第二探测像元r

si

)探测到的信息具有相关性,可以用两者之间差值作为有效信号进行处理转换。这样,可以用比较少的位数进行编码,只传送差值序列,减少数据的传输,达到压缩数据的目的,同时采用多通道位串行转换的结构,其压缩位数可变,可以有效避免相邻像素间探测差异过大,固定压缩位数带来的溢出问题。

34.需要指出的是,2008年,c.h.hwang在论文中提出了像素级模数转换中运放复用的结构,本发明的一个发明实例使用其结构来缓解像素面积小带来的压力。

35.图1是本发明一个实施例的红外焦平面像素级数字化读出电路的整体结构示意图。本发明的一个实施例中,该读出电路用于接收探测像元的模拟信号,对模拟信号进行积分及模数转换,最后予以输出。

36.具体的,本发明的一种红外焦平面像素级数字化读出电路,包括参考探测电桥10和探测电桥矩阵20,还包括运放复用电路30和信号锁存电路40。

37.本实施例中,参考探测电桥10及探测电桥矩阵20用来给探测像元提供第一偏置电压同时输出含探测信息的模拟信号,参考探测电桥10可独立工作并通过第十开关s

int1 303输出(含探测信息)电流信号到运放复用电路30;此外探测电桥矩阵20包括若干个结构相同独立设置的探测电桥支路,任一探测电桥支路可与参考探测电桥10构成电桥结构,并通过第十一开关s

int2 304输出(含探测信息)电流信号到运放复用电路30。

38.具体的,当设置在所述参考探测电桥10与所述探测电桥矩阵20之间的开关断开时,所述参考探测电桥10将含有探测信息的电流通过第十开关s

int1 303输出到运放复用电路30;当设置在所述参考探测电桥10与所述探测电桥矩阵20之间的开关闭合时,将所述探测电桥支路与所述参考探测电桥10的电流之差((含探测信息)电流信号)通过第十一开关s

int2 304 输出到运放复用电路30。

39.所述运放复用电路可以在电容跨导放大器模式和比较器模式之间进行切换;电容跨导放大器模式的所述运放复用电路对所述参考探测电桥或所述探测电桥矩阵输出的电

流进行积分;比较器模式的所述运放复用电路对积分电压和斜坡电压进行比较,并将结果输出。

40.本实施例中,所述运放复用电路30包括运算放大器opamp 301、积分电容c 302、复位开关rst 310、第五开关s5 305、第六开关s6 306、第七开关s7 307、第八开关s8 308、第九开关s9 309、第十开关s

int1 303和第十一开关s

int2 304,所述参考探测电桥10的输出端通过所述第十开关s

int1 303与所述运算放大器opamp 301的反向输入端连接,所述探测电桥矩阵20的输出端通过所述第十一开关s

int2 304与所述运算放大器opamp 301的反向输入端连接,所述运算放大器opamp 301的同相输入端通过所述第八开关s8 308与第九开关s9 309 分别与参考电压v

ref

和斜坡电压v

ramp

相连,所述积分电容c 302与所述复位开关rst 310并联在所述运算放大器opamp 301的反相输入端和输出端之间,所述积分电容c 302与所述复位开关rst 310的并联链路与所述运算放大器opamp 301的输出端连接的一端通过所述第五开关s5 305与所述参考电压v

ref

连接,同时,所述积分电容c 302与所述复位开关rst 310的并联链路与所述运算放大器opamp 301的输出端之间设有所述第六开关s6 306,所述运算放大器opamp 301的输出端与所述信号锁存电路40通过所述第七开关s7 307连接。

41.对电流积分前,复位开关rst 310闭合,对积分电容c 302复位。

42.本实施例中,在积分阶段,所述运放复用电路30为电容跨导放大器模式:所述第六开关 s6 306和所述第八开关s8 308闭合,所述第五开关s5 305、所述第七开关s7 307和所述第九开关s9 309断开,第十开关s

int1 303或第十一开关s

int2 304闭合,运放复用电路30 对参考探测电桥10和/或探测电桥矩阵20传来的电流信号进行积分。积分后运算放大器 opamp 301输出端电压为:

[0043][0044]

其中,t

int

表示积分电容c的积分时间,v

ref

为参考电压,c为积分电容的大小。

[0045]

积分完成后,所述第六开关s6和所述第八开关s8断开,所述第五开关s5、所述第七开关s7和所述第九开关s9闭合,由于积分电容c两端的电压不会突变,运算放大器opamp 301 反相输入端的电压为:

[0046]va-d

=2v

ref-v

int

(t

int

)

ꢀꢀ

(2)

[0047]

其中,v

int

(t

int

)为积分电压,t

int

表示积分时间,v

ref

为参考电压,积分电压v

int

(t

int

)为积分结束后的运算放大器opamp 301输出端电压。

[0048]

运放复用电路转换在数模转换阶段,此时,所述运放复用电路30为比较器模式:对电容跨导放大器模式所产生的积分电压v

int

(t

int

)和斜坡电压v

ramp

进行比较,并将比较结果传输给信号锁存电路40,信号锁存电路40接受1位bitx信号,并根据运放复用电路30的比较结果判断是否锁存bitx信号。

[0049]

所述信号锁存电路40包括锁存使能信号端、锁存信号输入端和信号输出端,所述锁存使能信号端与所述运算放大器opamp的输出端通过所述第七开关s7连接,所述锁存信号输入端连接到bitx信号端。

[0050]

需要说明的是,信号锁存电路40可以是本领域内常用的锁存器,为本领域技术人员的常规技术手段,并非本发明的发明点,因此,在此不再详述其具体结构。

[0051]

本实施例中,在焦平面上均匀选定某些像元放置在参考探测电桥10上,在这些像元附近范围的3个像元中放置探测电桥矩阵20的探测电桥支路,运放复用电路30和信号锁存电路40为参考探测电桥10和探测电桥矩阵20的共用电路,即2

×

2像素共用一组运放复用电路30和信号锁存电路40。

[0052]

本发明的实施例采用多通道位串行转换,对于一个像元的积分电压,每次比较获得1bit 数字码并输出,通过改变bitx信号的变化规律依次完成n次比较,将n次比较获得的数字码合并作为最终的n位数字码。

[0053]

图2是本发明一个实施例的参考探测电桥和探测电桥矩阵的电路示意图。

[0054]

如图2所示,本实施例中,所述参考探测电桥10包括第一盲像元r

b 101、第一pmos晶体管mp

eb 102、第一nmos晶体管mn

sel 103、第二nmos晶体管mn

fid 104、第一探测像元r

s 105、第三开关s3 106和第四开关s4 107,所述第一盲像元r

b 101的一端与第一偏置电压vsk连接,所述第一盲像元r

b 101的另一端与所述第一pmos晶体管mp

eb 102的源极连接,所述第一pmos晶体管mp

eb

102的漏极与所述第一nmos晶体管mn

sel

103的漏极连接,所述第一nmos 晶体管mn

sel 103的源极与所述第二nmos晶体管mn

fid 104的漏极连接,所述第二nmos晶体管 mn

fid 104的漏极通过所述第三开关s3 106与所述第二nmos晶体管mn

fid 104的栅极连接,所述第二nmos晶体管mn

fid 104的栅极通过所述第四开关s4 107与第二偏置电压v

fid

连接,所述第二nmos晶体管mn

fid

104的源极与所述第一探测像元r

s 105的一端连接,所述第一探测像元r

s 105的另一端与电源地gnd连接,所述第一pmos晶体管mp

eb 102的栅极与第三偏置电压v

eb

连接。

[0055]

本实施例中,所述参考探测电桥10的输出端为所述第一nmos晶体管mn

sel 103的漏极,所述参考探测电桥10独立工作时的含有探测信息的输出电流的大小为流过所述第一盲像元 r

b 101电流和流过所述第一探测像元r

s 105电流之间的差。

[0056]

如图2所示,第三开关s3 106、第一开关s1

i 206、第二开关s2

i 207断开,第四开关 s4 107闭合,参考探测电桥10独立工作,参考探测电桥10输出电流大小为流过第一盲像元 r

b 101电流和流过第一探测像元r

s 105电流之间的差,此时电流为:

[0057]iint

(t)=ib(t)-is(t)

ꢀꢀ

(3)

[0058]

其中,is(t)表示流过第一探测像元r

s 105的电流,ib(t)表示流过第一盲像元r

b 101的电流。

[0059]

本实施例中,所述探测电桥矩阵20包括若干个结构相同的探测电桥支路,如图2所示,所述探测电桥支路包括第二盲像元r

bi 201、第二pmos晶体管mp

ebi 202、第三nmos晶体管mn

seli 203、第四nmos晶体管mn

fidi 204、第二探测像元r

si 205、第一开关s1

i 206和第二开关s2

i 207,所述第二盲像元r

bi 201的一端与所述第一偏置电压vsk连接,所述第二盲像元r

bi 201的另一端与所述第二pmos晶体管mp

ebi 202的源极连接,所述第二pmos晶体管mp

ebi 202的漏极与所述第三nmos晶体管mn

seli 203的漏极连接,所述第三nmos晶体管mn

seli 203的源极与所述第四 nmos晶体管mn

fidi 204的漏极连接,所述第四nmos晶体管mn

fidi 204的源极连接到所述第二探测像元r

si 205的一端连接,所述第二探测像元r

si 205的另一端与所述电源地gnd连接,所述第二pmos晶体管mp

ebi 202的栅极通过所述第一开关s1

i 206与所述第一pmos晶体管mp

eb 102 的栅极连接,所述第四nmos晶体管mn

fidi 204的栅极通过所述开关s2

i 207连接到所述第二nmos 晶体管mn

fid 104的栅极。

[0060]

本实施例中,所述探测电桥支路的输出端为所述第三nmos晶体管mn

seli

203的漏极,所述探测电桥支路的输出电流值为流过所述第二探测像元r

si 205和流过所述第一探测像元r

s 105 的电流之差。

[0061]

如图2所示,第三开关s3 106、第一开关s1

i 206、第二开关s2

i 207闭合,第四开关 s4 107断开,探测电桥矩阵20的探测电桥与参考探测电桥10构成电桥。探测电桥矩阵20 的输出值为两条支路电流之差,即流过第二探测像元r

si 205与流过第一探测像元r

s 105的电流之差,此时输出的电流为:

[0062]iinti

(t)=i

si

(t)-is(t)

[0063]

其中,is(t)表示流过第一探测像元r

s 105的电流,i

si

(t)表示流过探测电桥矩阵20中某支路的第二探测像元r

si 205的电流。

[0064]

本发明的一个实施例中,参考探测电桥10独立工作并输出电流i

int

(t)到运放复用电路 30,对i

int

(t)进行积分,在多通道位串行转换结构的基础上,依次转换出14位数字码表示第一探测像元rs的探测信息;之后再选择探测电桥矩阵20的某一探测电桥与参考探测电桥 10构成电桥,输出两探测像元电流之差i

inti

(t)到运放复用电路30,对像元电流之差i

inti

(t) 进行积分,由于相邻像素间的探测信息具有相关性,即is(t)与i

si

(t)之间的差值i

inti

(t)较小,在多通道位串行转换结构的基础上,可依次转化换出8位数字码表示探测像元r

si

与探测像元rs的探测信息之间的差异,减少了读出电路需要输出的数据量。

[0065]

本发明的一个实施例中,由于多通道位串行转换中,每次比较会输出1bit数字码,基于该特点,具体压缩位数可根据实际需要而改变。当探测电桥矩阵20的某一探测电桥与参考探测电桥10构成电桥时,判断差值i

inti

(t)转换出的8位数字码是否存在全为“1”的情况,若8位数字码全为“1”可判定为存在溢出错误,即差值i

inti

(t)过大,8位数字码的范围无法覆盖该数值,在下一帧的模数转换中需要进行压缩位数扩展,扩展方法为增加比较次数,并改变bitx信号的变换规律,可将压缩数字码位数从8位连续调整至13位。相应的,若差值 i

inti

(t)过小,无需8位数字码便可表述其值,可以减少比较次数,减少压缩后的数字码位数。

[0066]

本发明的一个实施例中,在对两像元信号的差值进行模数转换时,通过增加或减少比较次数,改变bitx信号的变换规律,可以实现压缩位数可扩展,避免固定压缩位数造成信息丢失,相比于固定压缩位数,本发明的压缩结构具有灵活性。

[0067]

本发明实施例具有数据压缩结构,减少了读出电路模数转换的数据量,缓解了读出电路大数据量高速输出的问题,避免了传统大面阵读出电路中lvds等高速接口的使用,此外在多通道位串行转换的基础上,通过改变比较次数,其压缩的数字码位数可变,具有灵活性,避免了免固定压缩位数造成信息丢失的问题。

[0068]

以上所述的具体实施方式,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施方式而已,并不用于限定本发明的保护范围,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。