1.本发明涉及微波单片集成电路及微电子技术,特别涉及一种硅基时间调制相控阵馈电网络单元及时间调制相控阵系统。

背景技术:

2.随着无线通信系统的快速发展,相控阵系统被广泛应用在各个领域,其中突出体现在在航空航天、精确制导、近程探测等领域。传统相控阵系统的辐射特性是通过控制馈电网络中的幅度和相位来实现的,其中相位的控制精度有赖于高精度的移相器设计。随着通信速率的不断提升,相控阵系统的设计已经进入毫米波频段,而在微波/毫米波频段,移相器的设计复杂,且移相精度不高。因此时间调制相控阵系统具有非常广泛应用前景。

3.时间调制相控阵系统是将时间维度引入传统的相控阵天线系统的设计,通过外加控制信号令开关周期性的通断,可以实现高精度的移相;另外通过设计时间脉冲调制函数的波形以及引入正交调制可以实现抑制边带信号产生的混叠,但是结构的实现往往有赖于在通路里引入多个射频开关。中国专利申请cn109037972提出了一种基于二重时间调制天线复权重馈电网络,其在单个信号通路上需要引入两个单刀双掷开关;中国专利申请cn113675623a提出的一种时间调制相控阵馈电网络芯片,在单个通路上需要引入一个单刀三掷开关与两个单刀双掷开关。而在微波/毫米波频段,典型的单刀双掷开关的插入损耗为2-3db,因此会增加系统的损耗,大大降低系统的增益与效率。除此之外,在时间脉冲调制函数的波形设计,以及正交调制需要功分/功合器设计中,现有方案都基本基于威尔金森功分器的设计,然而在硅基集成电路的设计中,威尔金森功分器的面积庞大,因此并不适合应用在集成化设计中。

技术实现要素:

4.本发明的目的在于提出一种硅基时间调制相控阵馈电网络单元及时间调制相控阵系统。

5.实现本发明目的的技术解决方案为:一种硅基时间调制相控阵馈电网络单元,包括功分模块、时间调制模块、正交合成模块、放大器模块,信号发射过程中,发射信号经功分模块进入时间调制模块,或者直接进入时间调制模块,在时间调制模块中完成信号移相后,由正交合成模块对移相后的信号进行同相/正交变换和功率合成,再由放大器模块进行信号放大输出;信号接收过程中,射频信号经放大器模块放大后,由正交合成模块进行功分和同相/正交变换,再进入时间调制模块进行信号移相,移相后的信号经功分模块合成输出,或者直接输出;

6.所述时间调制模块由多组开关和0/π移相器组成,通过改变开关状态控制功分模块的接入情况,与功分模块直接连接的0/π移相器后的开关导通、未与混合式功率分配器连接的0/π移相器后的开关关断时,功分模块接入链路,信号通过功分模块及与其直接连接的0/π移相器进入链路或者从链路输出;与功分模块直接连接的0/π移相器后开关关断、未与

混合式功率分配器连接的0/π移相器后开关导通时,功分模块不接入链路,信号通过不与功分模块连接的0/π移相器进入链路或者从链路输出。

7.进一步的,所述功分模块由基于变压器的混合式功率分配器构成,变压器初级线圈中心抽头与次级线圈中心抽头相连,且通过电容接地;次级线圈的两端口连接时间调制模块的同相通道和正交通道,在两端口之间还串联电阻,用于起到隔离端口的作用。

8.进一步的,所述时间调制模块由第一至第八开关以及四组相位差为180

°

的0/π移相器构成,其中:

9.第一开关和第二开关分别位于第一移相器的π移相支路与0移相支路,第三开关和第四开关分别位于第二移相器的π移相支路与0移相支路,第五开关和第六开关分别位于第三移相器的π移相支路与0移相支路,第七开关和第八开关分别位于第四移相器的π移相支路与0移相支路;

10.第一移相器和第四移相器一端直接连接接收信号的输出端口或者发射信号的输入端口,第二移相器和第三移相器一端连接功分模块,第一移相器和第二移相器另一端通过开关连接正交合成模块的同相通道,第三移相器和第四移相器另一端通过开关连接正交合成模块的正交通道。

11.进一步的,所述第一至第八开关采用深n阱nmos晶体管。

12.进一步的,所述第一至第八开关的控制逻辑为:

13.第一开关在一个相对周期t

p

的第时刻开启至其余时刻处于关断状态;第二开关在一个相对周期t

p

的第时刻开启至其余时刻处于关断状态;第三开关在一个相对周期t

p

的第时刻开启至第时刻开启至其余时刻处于关断状态;第四开关在一个相对周期t

p

的第时刻开启至第时刻开启至其余时刻处于关断状态;第一开关在一个相对周期t

p

的第时刻开启至第时刻开启至其余时刻处于关断状态;第六开关在一个相对周期t

p

的第时刻开启至第时刻开启至其余时刻处于关断状态;第七开关在一个相对周期t

p

的第时刻开启至其余时刻处于关断状态;第八开关在一个相对周期t

p

的第时刻开启至其余时刻处于关断状态;t

p

为时间调制脉冲波形的周期。

14.进一步的,所述时间调制模块的时间调制脉冲时序满足以下关系式:

[0015][0016][0017]

[0018]

在上式中,τ'与τ”分别为导通状态和单路状态下的导通时间,与分别表示同相通路上双路状态的起始时刻,与分别表示正交通路上双路状态的起始时刻,与分别表示同相通路上单路状态的起始时刻,与分别表示正交通路上单路状态的起始时刻。

[0019]

进一步的,所述时间调制模块的移相功能通过调整脉冲的起始时间点来实现,若波束的指向角度为θ0,则其与脉冲起始时间点的关系为:则其与脉冲起始时间点的关系为:连续调整脉冲起始的时间,即实现时间调制模块在0-2π连续的相位变化。

[0020]

进一步的,所述正交合成模块由基于变压器的正交合成网络构成,初级线圈的端口1为合成端口,端口2为直通端口,次级线圈的端口3为耦合端口,另外一端接地,端口2、端口3分别通过第一并联电容和第二并联电容接地,用以实现端口2、端口3的90

°

相位差,形成同相/正交通路,以完成正交的时间调制。

[0021]

进一步的,所述放大器模块由功率放大器、低噪声放大器以及单刀双掷开关构成,其中功率放大器用于对发射信号进行放大;低噪声放大器用于对天线接收的信号进行放大;单刀双掷开关用于根据信号发射或者接收的场景选择功率放大器或低噪声放大器工作。

[0022]

一种时间调制相控阵系统,包括n个所述的时间调制相控阵馈电网络单元,以及1-n功分器、fpga控制电路或者硅基逻辑电路、n个天线阵元,且集成于单片硅基芯片当中,其中:

[0023]

n个时间调制相控阵馈电网络单元用于对天线阵元馈电,实现信号的发射与接收,以及移相的功能;1-n功分器用于对n个馈电网络单元进行功率分配/合成;fpga控制电路或者硅基逻辑电路发出周期性通断信号,用于改变芯片内开关的工作状态,以实现时间调制相控阵系统的相位加权;n个天线阵元用于对射频信号进行接收或者发射。

[0024]

本发明与现有技术相比,其显著优点为:1)简化了时间调制相控阵馈电网络的结构,使得每一个信号通路上的开关数量减少到一个,由此减小了开关的插入损耗对系统带来的效率和增益的影响;2)引入基于变压器的混合功分器以及基于变压器的正交合成网络,大大减小了功分模块与正交合成模块的面积,节省版图面积,有利于集成化设计;3)集成设计的芯片可以大大缩小时间调制射频系统的体积,大大提升了系统的集成度。

附图说明

[0025]

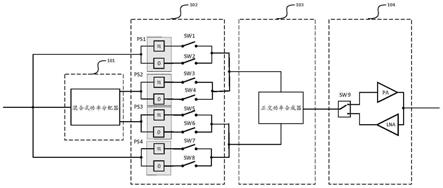

图1是本发明硅基时间调制相控阵馈电网络单元的拓扑结构图;

[0026]

图2是本发明混合式功率分配器的等效电路图与版图;

[0027]

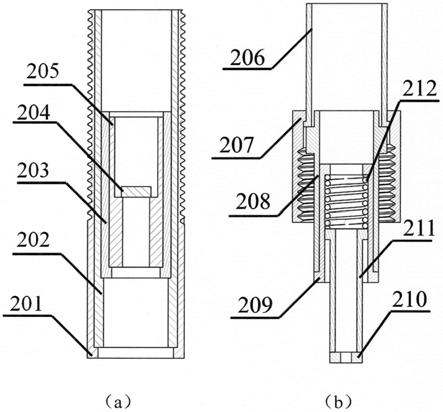

图3是本发明硅基开关的结构示意图;

[0028]

图4是本发明正交合成网络的等效电路图与版图;

[0029]

图5为本发明开关控制信号的控制逻辑图;

[0030]

图6是本发明时间调制脉冲波形图,其中(a)同相通道的时间调制脉冲波形图;(b)是正交通道的时间调制脉冲波形图;(c)是总电路的时间调制脉冲波形图。

[0031]

图7是本发明时间调制相控阵系统的拓扑结构图;

[0032]

图8是本发明时间调制相控阵系统的输出信号频谱归一化分布图。

具体实施方式

[0033]

为了使本技术的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本技术进行进一步详细说明。应当理解,此处描述的具体实施例仅用以解释本技术,并不用于限定本技术。

[0034]

图1是硅基时间调制相控阵馈电网络芯片拓扑结构。硅基时间调制相控阵馈电网络单元从左至右包含功分模块101、时间调制模块102、正交合成模块103、放大器模块104。功分模块101用于与时间调制模块102实现可重构功分功能;时间调制模块102用于施加脉冲调制函数,以实现低边带电平的波形,同时实现高精度的移相;正交合成模块103用于形成同相/正交通路,以实现正交的时间调制;放大器模块104由功率放大器与低噪声放大器组成,用于对发射或者接收的射频信号进行放大,以实现系统对发射信号与接收信号的功率要求;所有模块均集成于单一硅基时间调制相控阵馈电网络芯片当中,且各个模块之间均进行良好匹配。

[0035]

信号发射过程中,发射信号经功分模块进入时间调制模块,或者直接进入时间调制模块,在0/π移相器中完成信号移相后,由正交合成模块对移相后的信号进行同相/正交变换和功率合成,再由放大器模块进行信号放大输出;信号接收过程中,射频信号经放大器模块放大后,由正交合成模块进行功分和同相/正交变换,再进入时间调制模块,由0/π移相器进行信号移相,移相后的信号经功分模块合成输出,或者直接输出。请参见101,为功分模块,其基本结构为基于变压器的混合式功率分配器。参见102,为时间调制模块,其由开关sw1-sw8,以及四组相位差为180

°

的0/π移相器ps1-ps4构成。其中sw1、sw2分别位于ps1中的π移相支路与0移相支路,sw3、sw4分别位于ps2中的π移相支路与0移相支路,sw5、sw6分别位于ps3中的π移相支路与0移相支路,sw7、sw8分别位于ps4中的π移相支路与0移相支路;每组移相器对应的两个开关不会同时导通。开关sw1或sw2导通、其余开关关断的时候,功分模块不接入链路中,信号不被功分,直接进入时间调制模块;开关sw7或sw8导通、其余开关关断的时候,功分模块不接入链路中,信号不被功分,直接进入时间调制模块;开关sw3或sw4或sw5或sw6导通、开关sw1、sw2、sw7、sw8关断时,功分模块接入链路中;第一移相器和第四移相器ps1、ps4一端直接连接接收信号的输出端口或者发射信号的输入端口,第二移相器和第三移相器ps2、ps3一端连接功分模块,第一移相器和第二移相器ps1、ps2另一端通过开关连接正交合成模块的同相通道,第三移相器和第四移相器ps3、ps4另一端通过开关连接正交合成模块的正交通道。

[0036]

参见103,为正交合成模块,其基本结构为基于变压器的正交合成网络;基于变压器的正交合成网络可以在仅占用一个变压器版图面积的前提下实现低损耗、宽带宽的正交生成网络。参见104,为放大器模块,其由功率放大器pa、低噪声放大器lna以及单刀双掷开关sw9构成;其中功率放大器pa作用是对发射信号进行放大;低噪声放大器lna作用为对天线接收的信号进行放大;开关sw9的作用是根据信号发射或者接收的场景选择功率放大器或低噪声放大器工作。

[0037]

图2是混合式功率分配器的等效电路图与版图。变压器tf1初级线圈t1中心抽头与

次级线圈t2中心抽头相连,且通过电容c1接地;t1一端连接芯片发射链路输入信号/接收链路输出信号,另外一端接地;t2两端中间串联阻抗为2

×

z0的电阻,z0为电路的特征阻抗,用于起到隔离2/3端口的作用;t2两端分别与同步通道i与正交通道q的时间调制模块部分相连。

[0038]

图3是硅基开关结构,开关采用深n阱(dnw)nmos晶体管设计,深n阱结构管将p-well体端隔离,以减小电容耦合和信号泄露,同时dnw接高电平,形成一对反接pn结,由此产生屏蔽公共衬底耦合产生的噪声干扰和寄生效应带来的相位延迟,使开关具有良好的隔离度;体端端接r

sub

,r

sub

取值为10kω大电阻,其将源、漏与衬底寄生电容悬浮隔离,由此减小对地信号的泄露,并减小信号在寄生电容电感上的摆幅,进而达到减小插入损耗和提高线性度的目的;外部控制信号施加在dnwnmos的栅极上,当控制信号v

ctrl

大于晶体管开启电压v

th

时,开关导通;控制信号v

ctrl

小于晶体管开启电压v

th

时,开关关断。

[0039]

图4是正交合成网络的等效电路图与版图,初级线圈上的端口1为合成端口,端口2为直通端口;次级线圈一端为端口3,为耦合端口,另外一端接地。端口2、端口3分别并联一个电容到地,用以实现端口2、端口3相位差为90

°

,用以形成同相/正交通路,以实现正交的时间调制相控阵系统。

[0040]

图5为开关控制信号的控制逻辑。当归一化电平为1时,开关导通;归一化电平为0时,开关关断;

[0041]

所述开关的控制逻辑为:开关sw1在一个相对周期t

p

的第时刻开启至其余时刻处于关断状态;开关sw2在一个相对周期t

p

的第时刻开启至其余时刻处于关断状态;开关sw3在一个相对周期t

p

的第时刻开启至第时刻开启至其余时刻处于关断状态;sw4在一个相对周期t

p

的第时刻开启至第时刻开启至其余时刻处于关断状态;sw5在一个相对周期t

p

的第时刻开启至第时刻开启至其余时刻处于关断状态;sw6在一个相对周期t

p

的第时刻开启至第时刻开启至其余时刻处于关断状态;开关sw7在一个相对周期t

p

的第时刻开启至其余时刻处于关断状态;开关sw8在一个相对周期t

p

的第时刻开启至其余时刻处于关断状态;t

p

为时间调制脉冲波形的周期。其完整控制信号的控制逻辑如图6所示,通过对开关施加如图6所示的周期脉冲信号,即可实现图6所示的时间调制脉冲波形图;

[0042]

图6是时间调制脉冲波形,(a)为同相通道上的时间调制脉冲波形;(b)为正交通道上的时间调制脉冲波形;(c)为总电路上的时间调制脉冲波形;其中脉冲调制波形是通过fpga控制电路产生周期性的开关控制信号,经过驱动电路施加到时间调制馈电网络单元中的开关上产生的;请参见图7,图中所示的脉冲调制函数时序满足以下关系式:

[0043]

[0044][0045][0046]

在上式中,τ'与τ”分别为导通状态和单路状态下的导通时间,与分别表示同相通路上双路状态的起始时刻,与分别表示正交通路上双路状态的起始时刻,与分别表示同相通路上单路状态的起始时刻,与分别表示正交通路上单路状态的起始时刻,t

p

为时间调制脉冲波形的周期。

[0047]

在满足上述公式时,本实施例中的时间调制射频系统可以输出 1次边带信号,且无混叠信号带宽为8f

p

。式中,f

p

为时间调制脉冲波形的频率。

[0048]

通过调整脉冲的起始时间点即可实现时间调制电路在0-2π自由的相位变化,若波束的指向角度为θ0,则脉冲起始的时间点为:

[0049][0050]

图7是时间调制相控阵系统的拓扑结构。本实例中,时间调制相控阵系统由4个时间调制相控阵馈电网络单元、1-4功分器、fpga控制电路或者硅基逻辑电路、4个天线阵元,且集成于单片硅基芯片当中;

[0051]

4个时间调制相控阵馈电网络单元801用于对天线阵元馈电,以使系统实现信号的发射与接收,以及移相的功能;1-4功分器802用以对4个馈电网络单元进行功率分配/合成;fpga控制电路或者硅基逻辑电路803发出周期性通断信号,用以周期性改变芯片内开关的工作状态,以实现时间调制相控阵系统的相位加权;n个天线阵元804用于对射频信号进行接收或者发射;

[0052]

图8是时间调制射频系统的输出信号频谱归一化分布的示例图。可以看出,时间调制射频系统的输出信号频谱最大无用边带为 7次边带,最大无用边带电平低于-16.5db。

[0053]

以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

[0054]

以上所述实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术专利的保护范围应以所附权利要求为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。