1.本发明属于无线通信技术领域,涉及射频接收链路中的核心模块:中频放大器,具体提供一种带体漏交叉耦合技术的高增益中频放大器。

背景技术:

2.中频放大器作为射频接收链路中的关键模块,需要将下变频得到的中频信号的电压幅度进行放大;在射频接收链路中,中频放大器的增益较高,不仅可以压制后级的噪声,控制整体链路的噪声系数,还可以在输入信号较小的情况下仍然可以驱动链路后面的adc等模块,提高数模链路整体性能。近年来,无线通信技术的高速发展和应用场景的扩大,人们对信息量的要求越来越高,因此工作频率也越来越高;在新技术背景下,设计出更高增益的中频放大器,成为了当前研究领域的焦点。

3.目前已有很多方法被应用于提高放大器的增益,其中,共源共栅电路结构能够有效地提高输出阻抗,从而提高放大器的增益,其电路原理图如图1所示;其中,晶体管m1、m2构成共源极的差分输入对,栅极输入差分信号、源极接地、漏极分别连接m3和m4两个共栅极接法的晶体管,m3和m4的栅极接直流偏压、漏极连接负载和输出接口,load1和load2可以是有源负载、电阻负载等多种形式,输出端口的c

l1

和c

l2

为需要驱动的负载电容;该结构提升增益的方式通过如图2所示的小信号关系进行分析,具体如下:

4.由于差分放大器的对称性,取图1左半边的电路进行小信号分析,其中,g

m1

和g

m3

分别为晶体管m1和m3的跨导,r

o1

和r

o3

分别为晶体管m1和m3由沟道长度调制效应引起的小信号输出电阻;对图2中的电路进行小信号分析可知,cascode电路结构的小信号输出电阻在m3管的影响下,由共源管的r

o1

||r

load1

变为了:

5.r

out

=(g

m3ro3ro1

r

o1

r

o3

)||r

load1

≈(g

m3ro3ro1

)||r

load1

6.结合输出的负载电容,cascode结构的小信号电压增益为:

7.av=g

m1

(r

out

||c

l1

)=g

m1

[(g

m3ro3ro1

)||r

load1

||c

l1

]

[0008]

相比于传统共源极放大器的电压增益av=g

m1

(r

o1

||r

load1

||c

l1

),cascode结构将其中的r

o1

部分放大了g

m3ro3

倍,从而提高了增益。

[0009]

上述共源共栅(cascode)放大器虽然能够提升小信号增益,但也存在如下问题:

[0010]

1)cascode放大器串联了两个mos管,使输出电压摆幅减小;对于传统的nmos共源极放大器,其最低输出电压可以达到一倍的vov(过驱动电压,大小等于mos管栅源电压差减去阈值电压),但添加了共栅管之后,最低输出电压提高到2vov,明显减小了输出电压的动态范围,容易引起失真;因此,cascode结构牺牲了线性度不利于大摆幅的输出;

[0011]

2)cascode放大器无法有效地提高高频增益;中频放大器需要驱动较大的负载电容,而在新的通感技术应用中,往往又需要中频放大器处理频率在几mhz乃至几十mhz的中频信号,mhz级别的信号通常已经超过了放大器的主极点,随着频率的增加,电压增益急剧下降;即使cascode放大器能够通过提高输出阻抗提高输出增益,但是这种提升主要是针对低频信号,输出节点的rc时间常数也等比例提高了,导致电路的主极点降低,放大器的高频

信号增益未得到改善;另外,对于cascode结构的放大器,想要提高频率在mhz级别的信号,通常只能增加输入管的跨导gm,通过提高单位增益带宽的方式提高高频增益,但这种措施是以提高电流功耗为代价的,会导致放大器的直流功耗大幅增加。

[0012]

因此,如何实现放大器在mhz级别的中频频率下仍然保持较高的增益,成为当前中频放大器设计的主要难点。

技术实现要素:

[0013]

本发明的目的在于针对现有中频放大器高频增益有待提高的问题,提供一种带体漏交叉耦合技术的高增益中频放大器;本发明提出的新型结构采用了体漏交叉耦合技术,在不牺牲输出电压摆幅和直流功耗的前提下,有效提高中频放大器处理mhz级别信号时的电压增益,有效地抑制放大器增益的高频衰减。

[0014]

为实现上述目的,本发明采用的技术方案为:

[0015]

一种带体漏交叉耦合技术的高增益中频放大器,其特征在于,包括:共源极差分放大器、耦合电容c1与c2、及偏置电阻r1与r2,其中,所述共源极差分放大器包括:差分mos管对m1与m2,所述耦合电容c1一端连接mos管m1的体电极、另一端连接mos管m2的漏极,所述耦合电容c2一端连接mos管m2的体电极、另一端连接mos管m1的漏极,所述偏置电阻r1一端连接mos管m1的体电极、另一端接地,所述偏置电阻r2一端连接mos管m2的体电极、另一端接地。

[0016]

进一步的,所述耦合电容c1和c2的容值相同,取值为0.1c

l

~c

l

、c

l

为共源极差分放大器中负载电容的容值。

[0017]

进一步的,所述偏置电阻r1和r2的阻值相同,取值为千欧姆量级。

[0018]

进一步的,所述共源极差分放大器还包括:负载load1与load2、负载电容c

l1

与c

l2

,其中,mos管m1的栅极接正极输入端、源极接地、漏极接正极输出端,mos管m2的栅极接负极输入端、源极接地、漏极接负极输出端;负载load1串联在mos管m1的漏极与电源vdd之间,负载load2串联在mos管m2的漏极与电源vdd之间;负载电容c

l1

一端接正极输出端、另一端接地,负载电容c

l2

一端接负极输出端、另一端接地。

[0019]

更进一步的,所述mos管m1与m2尺寸相同。

[0020]

更进一步的,负载电容c

l1

与c

l2

的容值相同,均为c

l

、取值为皮法量级。

[0021]

本发明的有益效果在于:

[0022]

本发明提供一种带体漏交叉耦合技术的高增益中频放大器,由两部分组成:其一为由mos管m1与m2、负载load1与load2、负载电容c

l1

与c

l2

构成的共源极差分放大器,其二为由耦合电容c1与c2、偏置电阻r1与r2组成的体漏交叉耦合结构;本发明在传统的共源极放大器结构基础上,通过引入体漏交叉耦合技术,有效地提高了放大器的高频增益,减缓了负载大电容造成的增益随频率降低难题;并且,在提高高频增益的同时无需牺牲输出电压摆幅和功耗。更为具体的讲:

[0023]

1、本发明采用了体漏交叉耦合技术改进放大器,将差分对一侧mos管的漏极通过耦合电容(c1与c2)连接到另一侧mos管的体电极,同时再通过偏置电阻(r1与r2)为体电极提供静态偏置,有效地提高了放大器的高频信号的电压增益,特别是mhz级别信号的增益;

[0024]

2、本发明不需要添加额外的共栅晶体管,不会牺牲输出电压的摆幅;

[0025]

3、本发明仅在传统共源极放大器的基础上添加无源器件,不会增加功耗;

[0026]

4、本发明在以nmos或pmos作为差分对的放大器中都适用,在有源负载和无源负载的情况下也都适用。

附图说明

[0027]

图1为现有共源共栅放大器的电路原理图。

[0028]

图2为图1所示共源共栅放大器的小信号原理图。

[0029]

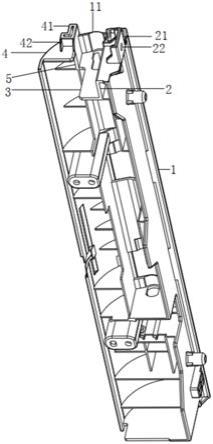

图3为本发明中带体漏交叉耦合技术的高增益中频放大器的电路原理图。

[0030]

图4为cmos工艺下带dnw的nmos剖面图。

[0031]

图5为本发明实施例与具有相同晶体管和负载的传统共源极放大器的电压增益对比图。

具体实施方式

[0032]

下面结合附图和实施例对本发明做进一步详细说明。

[0033]

本实施例提出一种带体漏交叉耦合技术的高增益中频放大器,在传统的共源极放大器的基础上引入体漏交叉耦合电容,将差分对一侧mos管的漏极通过电容连接到另一侧的体电极,同时再通过电阻为体电极提供静态偏置。

[0034]

本实施例中以nmos作输入差分对为例,其电路原理图如图3所示;具体包括:mos管m1与m2、负载load1与load2、负载电容c

l1

与c

l2

、以及耦合电容c1与c2、偏置电阻r1与r2,其中,mos管m1的栅极接正极的输入信号v

in

、源极接地、漏极接正极输出端;mos管m2的栅极接负极的输入信号v

in-、源极接地、漏极接负极输出端,根据差分放大器的对称性,mos管m1与m2尺寸相同;load1和load2为放大器的负载,load1串联在mos管m1的漏极与电源vdd之间,load2串联在mos管m2的漏极与电源vdd之间;c

l1

和c

l2

分别为正极输出端和负极输出端需要驱动的负载大电容,一端连接输出端、另一端接地,c

l1

和c

l2

的容值相同、通常为皮法量级;耦合电容c1一端连接mos管m1的体电极、另一端连接mos管m2的漏极,耦合电容c2一端连接mos管m2的体电极、另一端连接mos管m1的漏极,耦合电容c1和c2的容值相同、根据设计需要可以取值为0.1c

l

~c

l

,c

l

为负载电容c

l1

与c

l2

的容值;偏置电阻r1一端连接mos管m1的体电极、另一端接地,偏置电阻r2一端连接mos管m2的体电极、另一端接地,偏置电阻r1和r2的阻值相同,需要达到千欧姆量级。

[0035]

从工作原理上讲:

[0036]

上述带体漏交叉耦合技术的高增益中频放大器主要由两部分组成:其一为由mos管m1与m2、负载load1与load2、负载电容c

l1

与c

l2

构成的共源极差分放大器,其二为由耦合电容c1与c2、偏置电阻r1与r2组成的体漏交叉耦合结构。

[0037]

(1)共源极差分放大器

[0038]

在模拟电路中,共源极放大器有着广泛的应用,是非常常见的放大单元;

[0039]

如图3中的m1和m2,栅极接输入的电压信号,源极接地,漏极连接负载并输出电压信号,两个mos管偏置在饱和区,根据mos管的饱和区的工作特性可以得到其i-v关系为:

[0040]

[0041]

其中,μn为nmos管的载流子迁移率,c

ox

为单位面积的栅氧化层电容,w为mos管的沟道宽度,l为mos管的沟道长度,v

gs

为mos管栅极与源极之间的电压差,v

th

为mos管的阈值电压;

[0042]

因为mos管的源极接地所以v

gs

=v

in

,对输入电压进行求导可以得到mos管的跨导:

[0043][0044]

mos管的跨导表征了输入电压信号转化为输出电流的能力,输出电流在负载和mos管的小信号电阻上形成压降,转化为电压信号输出;图3中的load1和load2可以是有源负载、电阻负载等多种形式。

[0045]

(2)体漏交叉耦合结构

[0046]

如图3中的c1、c2为交叉耦合电容,一端连接一侧mos管的漏极输出端、另一端连接差分另一侧mos管的体电极,两个电容成交叉状,将一侧mos管放大过的信号耦合到另一侧mos管;电阻r1、r2为两个mos管的体电极提供偏置,这两个电阻的阻值要足够大,减少交流信号馈通到地造成的损耗;

[0047]

现今,许多p型衬底的cmos工艺都引入了dnw技术,使得nmos和pmos都可以做在单独的阱里,这使得mos管无需共用统一的体电位,而可以在每个mos管的体电极单独引入偏置和信号,这为体漏交叉耦合技术的实现提供了可能性;如图4所示为cmos工艺下带dnw的nmos剖面图,内部的p阱由体电极引出;关断状态的mos管无法导电,只有当mos管的v

gs

超过到阈值电压v

th

时,栅极氧化层下面的p型半导体反型,产生n型的沟道,连接了源极和漏极,才能有电流流过;v

th

表达式为:

[0048][0049]

其中,φ

ms

为多晶硅栅和硅衬底的功函数之差的电压值,φf为p阱内半导体的平带电压,以上两者都取决于具体的工艺掺杂情况,qd为耗尽区的电荷;

[0050]

假设v

gs

为0v,当体电极的电压vb变得更正时,会有更少的空穴被吸引到体电极,耗尽层变得更窄,沟道开启需要镜像的耗尽区电荷qd变得更少,因此v

th

减小;而当体电极的电压vb变得更负时,会有更多的空穴被吸引到体电极,耗尽层变得更宽,沟道开启需要镜像的耗尽区电荷qd变得更多,因此v

th

增大;

[0051]

对于图3中本发明提出的电路结构,当差分交流信号的正值信号输入m1,负值信号输入m2时,由于放大器的反相作用,m2的漏极为幅度更大的正值信号,这一信号通过电容c1馈入m1的体电极,vb升高,v

th

因而下降,(v

gs-v

th

)等效变得更大,同理m2的(v

gs-v

th

)等效变得更小;因此,体漏交叉耦合技术等效提高了输入交流信号的幅度,得到更大幅度的输出信号;由于该结构是基于电容进行耦合的,所以频率越高时耦合作用越强,因此能够提高放大器的高频增益,缓解负载大电容带来的增益急剧下降。

[0052]

如图5所示为本发明与具有相同晶体管和负载的传统共源极放大器的电压增益对比图,横轴是频率、纵轴是db表示的电压增益;其中,虚线为基础共源极放大器的电压增益,在8mhz以后开始明显下降;实线为添加了体漏交叉耦合技术后的电压增益,在3mhz后开始有明显的上升,在20mhz的频率下实线比虚线高出了4.94db,体漏交叉耦合技术在很宽的频带内减缓了增益随频率的下降,直到100mhz,实线依然高于虚线;由此可见,本发明能够提

高放大器的高频增益,缓解负载大电容带来的增益急剧下降。

[0053]

以上所述,仅为本发明的具体实施方式,本说明书中所公开的任一特征,除非特别叙述,均可被其他等效或具有类似目的的替代特征加以替换;所公开的所有特征、或所有方法或过程中的步骤,除了互相排斥的特征和/或步骤以外,均可以任何方式组合。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。