技术特征:

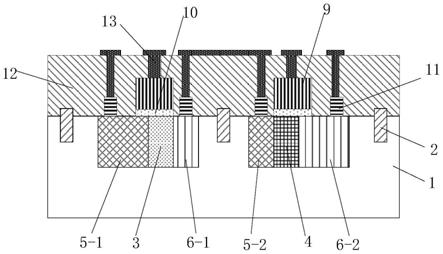

1.一种基于沟道掺杂调控的隧穿晶体管的三态反相器的制备方法,其特征在于,包括:步骤1:选择衬底(1);步骤2:利用浅沟槽隔离方法在所述衬底(1)的隔离区刻蚀隔离槽(2),隔离出ntfet与ptfet的有源区;步骤3:在所述衬底(1)上利用光刻胶进行掩蔽实现离子注入,形成ntfet的沟道区(3)以及ptfet的沟道区(4);步骤4:在所述衬底紧挨沟道区利用光刻胶进行掩蔽,实现离子注入,以形成ntfet的漏区(5-1)与ptfet的源区(5-2);步骤5:在所述衬底紧挨ntfet的漏区(5-1)以及紧挨ptfet的源区(5-2)利用光刻胶进行掩蔽,实现离子注入,以形成ntfet的源区(6-1)与ptfet的漏区(6-2);步骤6:使用快速退火工艺对步骤5所形成的结构进行退后处理,以激活杂质离子并修复离子注入引起的晶格损伤;步骤7:通过原子层淀积技术ald,在退火处理后所形成结构上沉积high-k栅氧化层介质形成栅介质层(7),以提高tfet的栅控能力;步骤8:利用磁控溅射在所述栅介质层(7)上形成tin栅金属层(8),并用光刻胶掩蔽所述tin栅金属层(8);步骤9:利用湿法腐蚀在tin栅金属层(8)上进行腐蚀,并剥离光刻胶,形成栅氧图形(9);步骤10:在所述栅氧图形(9)上,利用干法刻蚀形成栅氧形状(10)并漏出源漏接触电极区域;步骤11:以电子束蒸发技术在所述源漏接触电极区域形成源漏接触金属电极(11);步骤12:剥离光刻胶形成源漏电极(11),并进行退火以形成欧姆接触;步骤13:使用化学气相淀积pecvd技术,在退火后所形成的结构上淀积sio2形成钝化保护层(12),并在钝化保护层(12)上开接触孔;步骤14:在所述接触孔位置淀积互联金属,并反刻形成连接ptfet与ntfet的互联线(13),完成基于沟道掺杂调控的隧穿晶体管的三态反相器的制备。2.如权利要求1所述的制备方法,其特征在于,步骤1中所述衬底(1)为2寸单抛n100本征si衬底,厚度为500

±

25μm;步骤2中利用浅沟槽隔离方法在隔离区刻蚀深度为300

±

50nm,侧壁角度为90

±5°

的隔离沟槽,并填充sio2作为隔离介质。3.如权利要求1所述的制备方法,其特征在于,步骤3中实现离子注入形成ntfet的沟道区(3)的掺杂剂为硼,剂量为2e

14

~5e

14

cm-2

,注入能量为4~10kev;实现离子注入形成ptfet的沟道区(4)的掺杂剂为砷,剂量为2e

14

~5e

14

cm-2

,注入能量为4~10kev。4.如权利要求1所述的制备方法,其特征在于,步骤4中实现离子注入的掺杂剂为硼,剂量为2e

15

~3e

15

cm-2

,注入能量为8~12kev;步骤6中所述快速热退火的退火温度为950~1050℃,时长为5-10s。5.如权利要求1所述的制备方法,其特征在于,步骤7包括:通过原子层淀积技术ald形成厚度为3~5nm的high-k栅氧化层作为栅介质层(7);步骤9包括:通过磁控溅射的方法在所述栅介质层(7)上形成tin栅金属层(8),并剥离光刻胶形成栅电极,栅电极厚度100~150nm。

6.如权利要求1所述的制备方法,其特征在于,所述步骤11包括:通过电子束蒸发技术在源漏接触电极区域蒸发20~30nm ni金属,30~40nm pt金属,100~120nm au金属。7.如权利要求1所述的制备方法,其特征在于,所述步骤12中通过快速热退火在si表面形成镍硅合金,形成良好的欧姆接触,快速热退火的退火温度为600~650℃,时长为30s。8.如权利要求1所述的制备方法,其特征在于,所述步骤13包括:通过化学气相淀积pecvd,在步骤12已形成的器件上淀积150~200nm的sio2,并刻蚀钝化层形成接触孔。9.如权利要求1所述的制备方法,其特征在于,所述步骤14包括:在接触孔位置上淀积200~300nm互联金属al,通过反刻al形成互联线(13),将ptfet与ntfet的漏极连接形成反相器的输出端vout,ptfet与ntfet栅电极相连接形成反相器的输入端vin,ptfet的源端接高电平vdd,ntfet的源端接低电平gnd。10.一种基于沟道掺杂调控的隧穿晶体管的三态反相器,其特征在于,使用权利要求1至9任一项所述的基于沟道掺杂调控的隧穿晶体管的三态反相器的制备方法制备而成。

技术总结

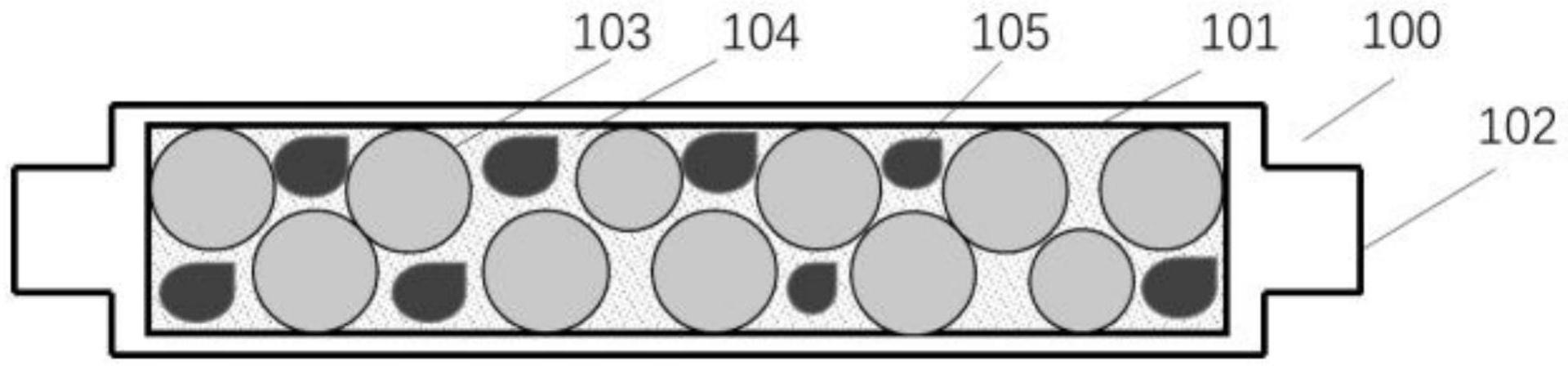

本发明提供的一种基于沟道掺杂调控的隧穿晶体管的三态反相器的制备方法以及制备出的反相器,在隧穿机理上采用线隧穿与面隧穿结合的方式制备新型三态CTFET;本发明栅极采用Overlap结构,使得三态CTFET相比于传统的CFET结构可以同时获得点隧穿和面隧穿电流,既能在更小的栅压下得到更大的电流和更低的亚阈值摆幅,也能由于隧穿发生的栅压不同,获得较为稳定的三态特性。同时本发明的反相器随着外加偏压VDD的改变可以在一定程度上实现两态与三态间的转化。由于所涉及的NTFET与PTFET均采用本征Si衬底,均为平面结构,与传统Si-TFET工艺流程大致相同,有利于制备与集成,同时与现有CMOS工艺兼容。CMOS工艺兼容。CMOS工艺兼容。

技术研发人员:吕红亮 赵孟青 朱翊 吕智军 孙佳乐 张玉明

受保护的技术使用者:西安电子科技大学

技术研发日:2022.01.05

技术公布日:2022/5/25

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。