技术特征:

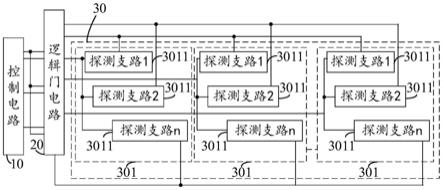

1.一种收发一体测距电路,其特征在于,所述收发一体测距电路包括:控制电路,具有时序信号输出端、n个控制信号输出端以及m个反馈信号接收端,用于输出时序信号以及n个控制信号;逻辑门电路,具有时序信号输入端、n个控制信号输入端以及n个驱动信号输出端,所述逻辑门电路的时序信号输入端与所述控制电路的时序信号输出端连接,n个所述逻辑门电路的控制信号输入端一对一连接至n个所述控制电路的控制信号输出端;并用于根据所述时序信号以及n个所述控制信号输出驱动信号;探测模块,具有n个驱动信号输入端以及m个探测信号输出端,n个所述探测模块的驱动信号输入端一对一连接至n个所述逻辑门电路的驱动信号输出端,m个所述探测模块的探测信号输出端一对一连接至m个所述控制电路的反馈信号接收端;所述探测模块包括n组探测电路;每一所述探测电路均包括m个探测支路;对于每一所述探测电路,m个所述探测支路的驱动信号输出端互相连接以构成所述探测模块的一驱动信号输入端;n组所述探测电路的第z探测支路的探测信号输出端互相连接以构成所述探测模块的一探测信号输出端;并用于在接收到所述驱动信号进行探测并获取与所述探测支路数量对应的探测信号;连接至同一反馈信号接收端的多个所述探测支路的探测信号叠加合并为一反馈信号;所述控制电路,还用于接收m个所述反馈信号,并根据m个所述反馈信号确定n*m个所述探测支路中每一所述探测支路的探测结果。2.如权利要求1所述的收发一体测距电路,其特征在于,n个所述控制信号为共时基pwm信号。3.如权利要求1所述的收发一体测距电路,其特征在于,所述控制电路为arm处理器。4.如权利要求1所述的收发一体测距电路,其特征在于,每一所述探测支路的探测频率不同。5.如权利要求1所述的收发一体测距电路,其特征在于,所述收发一体测距电路还包括m个放大电路,m个所述控制电路的反馈信号接收端与m个所述探测模块的探测信号输出端之间形成m个反馈回路,每一所述放大电路均单独设置于一所述反馈回路中以将对应的所述探测模块的探测信号输出端输出的反馈信号放大。6.如权利要求1所述的收发一体测距电路,其特征在于,所述逻辑门电路包括m个与门,每一所述与门的第一输入端与所述控制电路的时序信号输出端连接,m个所述控制电路的反馈信号接收端一对一连接至m个所述与门的第二输入端。7.一种收发一体测距电路,其特征在于,所述收发一体测距电路包括:控制电路,具有时序信号输出端、第一控制信号输出端、第二控制信号输出端、第三控制信号输出端、第一反馈信号接收端以及第二反馈信号接收端,并用于输出时序信号以及第一控制信号、第二控制信号以及第三控制信号;逻辑门电路,具有时序信号输入端、第一控制信号输入端、第二控制信号输入端、第三控制信号输入端、第一驱动信号输出端、第二驱动信号输出端以及第三驱动信号输出端,所述逻辑门电路的时序信号输入端与所述控制电路的时序信号输出端连接,所述逻辑门电路的第一控制信号输入端与所述控制电路的第一控制信号输出端连接,所述逻辑门电路的第二控制信号输入端与所述控制电路的第二控制信号输出端连接,所述逻辑门电路的第三控

制信号输入端与所述控制电路的第三控制信号输出端连接;并用于将所述时序信号分别与所述第一控制信号、所述第二控制信号以及所述第三控制信号进行逻辑运算以获得第一驱动信号、第二驱动信号以及第三驱动信号;探测模块,具有第一驱动信号输入端、第二驱动信号输入端、第三驱动信号输入端、第一探测信号输出端以及第二探测信号输出端,所述探测模块的第一驱动信号输入端与所述逻辑门电路的第一驱动信号输出端连接,所述探测模块的第二驱动信号输入端与所述逻辑门电路的第二驱动信号输出端连接,所述探测模块的第三驱动信号输入端与所述逻辑门电路的第三驱动信号输出端连接;所述探测模块的第一探测信号输出端与所述控制电路的第一反馈信号接收端连接,所述探测模块的第二探测信号输出端与所述控制电路的第二反馈信号接收端连接;所述探测模块包括第一探测电路、第二探测电路以及第三探测电路;每一所述探测电路均包括第一探测支路以及第二探测支路;所述第一探测电路的第一探测支路的驱动信号输出端与所述第一探测电路的第二探测支路的驱动信号输出端连接以构成所述探测模块的第一驱动信号输入端,所述第二探测电路的第一探测支路的驱动信号输出端与所述第二探测电路的第二探测支路的驱动信号输出端连接以构成所述探测模块的第二驱动信号输入端,所述第三探测电路的第一探测支路的驱动信号输出端与所述第三探测电路的第二探测支路的驱动信号输出端连接以构成所述探测模块的第三驱动信号输入端;所述第一探测电路的第一探测支路的探测信号输出端、所述第二探测电路的第一探测支路的探测信号输出端以及所述第三探测电路的第一探测支路的探测信号输出端互相连接以构成所述探测模块的第一探测信号输出端,所述第一探测电路的第二探测支路的探测信号输出端、所述第二探测电路的第二探测支路的探测信号输出端以及所述第三探测电路的第二探测支路的探测信号输出端互相连接以构成所述探测模块的第二探测信号输出端;并用于在接收到所述第一驱动信号、所述第二驱动信号以及所述第三驱动信号进行探测并获取与所述探测支路数量对应的第一探测信号、第二探测信号、第三探测信号、第四探测信号、第五探测信号以及第六探测信号;连接至同一反馈信号接收端的多个所述探测支路的探测信号叠加合并为一反馈信号;所述第一探测信号、所述第二探测信号以及所述第三探测信号叠加合并为第一反馈信号,所述第四探测信号、所述第五探测信号以及所述第六探测信号叠加合并为第二反馈信号。所述控制电路,还用于接收所述第一反馈信号以及所述第二反馈信号,并根据所述第一反馈信号以及所述第二反馈信号确定所述第一探测电路的第一探测支路、第一探测电路的第二探测支路、第二探测电路的第一探测支路、第二探测电路的第二探测支路、第三探测电路的第一探测支路、第三探测电路的第二探测支路的探测结果。8.一种电子设备,其特征在于,所述电子设备包括如权利要求1-5任一项所述的收发一体测距电路。9.如权利要求1所述的电子设备,其特征在于,所述电子设备还包括壳体,所述壳体具有相对设置的第一安装面以及第二安装面,每一对所述测试支路分设于所述第一安装面以及所述第二安装面。10.如权利要求1所述的电子设备,其特征在于,所述电子设备还包括壳体,所述具有相

对设置的第三安装面以及第四安装面,所述第三安装面与所述第一安装面相交设置,每一对所述测试支路分设于所述第一安装面、所述第二安装面、第三安装面以及第四安装面。

技术总结

本发明公开了一种收发一体测距电路以及电子设备,收发一体测距电路包括控制电路、逻辑门电路以及探测模块,逻辑门电路的时序信号输入端与控制电路的时序信号输出端连接,N个逻辑门电路的控制信号输入端一对一连接至N个控制电路的控制信号输出端。探测模块具有N个驱动信号输入端以及M个探测信号输出端,N个探测模块的驱动信号输入端一对一连接至N个逻辑门电路的驱动信号输出端,M个探测模块的探测信号输出端一对一连接至M个控制电路的反馈信号接收端。本发明解决了多个超声波探头的电路方案连线较为复杂的技术问题。方案连线较为复杂的技术问题。方案连线较为复杂的技术问题。

技术研发人员:徐小明 曹福新

受保护的技术使用者:深圳市灵星雨科技开发有限公司

技术研发日:2022.01.13

技术公布日:2022/5/30

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。