一种基于dds技术的可调脉冲成型方法

技术领域

1.本发明属于光通信技术领域,更为具体地讲,涉及一种基于dds技术的可调脉冲成型方法。

背景技术:

2.现代通信系统对通信信道的信噪比要求越来越高,低带宽占用和高速率的数字传输方式成为研究的主要方向。在数字化基带信号处理器中,脉冲成型技术对提高信道利用率、减小串扰有着非常重要的意义。

3.模拟电路在基带脉冲成型中采用模拟滤波器完成脉冲成型功能,这类电路可以根据传输信号的信道带宽要求,设计对应的有源或无源滤波器,实现基带信号的边沿成型。

4.数字方式进行基带脉冲边沿成型速度慢,但形状准确度较模拟方式相比有较大提升。开环控制的直接成型方法使用累加器对边沿控制字累加到需求值,反馈积分法将输出电平数字量作为反馈量送回控制器与要求电平进行比较,控制后级累加模块的工作和输出电平数字量。采用数字方电路进行波形合成的技术,对可控脉冲边沿成型技术具有指导意义。

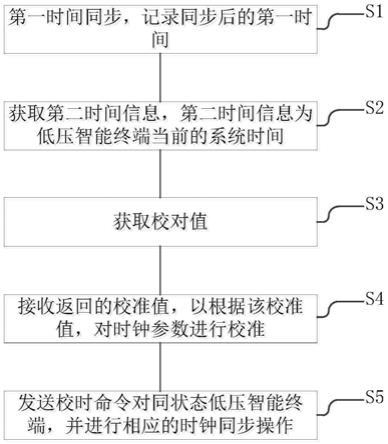

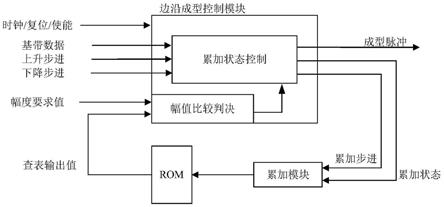

5.对于基带信号边沿要求不同,根据边沿形状可将成型过程划分为线性边沿成型和非线性边沿成型两类。针对不同边沿成型要求的信号特征,通过模拟电路或数字电路方案进行边沿成型控制成为研究的焦点。

6.模拟电路在基带脉冲成型中的主要应用场景是成型滤波器的电路设计,这类电路可以根据传输信号的信道要求,设计对应的有源或无源滤波器,形成基带信号的边沿成型。最常见的滤波电路可以通过rlc低通滤波电路实现,也可以使用有源滤波器的方案。

7.此外,使用阶跃恢复二极管和非线性传输线的改进型快速边沿成型方法,能够改善脉冲成型速度。但是由于模拟电路结构固定的特点,这类成型方法不具有可调性,仅适用于对称边沿的脉冲成型,成型形状单一,成型模块尺寸大。使用数字方式进行基带脉冲边沿成型形状准确度和灵活性较模拟方式相比有较大提升。基带脉冲信号的边沿要求为线性边沿时,主要分为开环直接成型和闭环反馈积分两类方法。开环控制的直接成型方法使用累加器对边沿控制字累加,直至达到累加上限停止。反馈积分法基本结构图如图1所示,该方法将输出电平数字量作为反馈量送回控制器,控制器中将反馈与要求电平进行比较,从而控制后级累加模块的工作。为能实现全数字方式的可调脉冲信号成型,结合闭环积分与波形合成技术。目前波形合成技术的终点在于如何控制产生波形的频率和宽度等定时特性上,忽略了脉冲边沿形状的可变控制。利用波形合成的动态特点和反馈积分的准确性特点,将为准确的可调脉冲边沿成型带来指导意义。

技术实现要素:

8.本发明的目的在于克服现有技术的不足,提供一种基于dds技术的可调脉冲成型方法,通过直接数字合成(direct digital synthesis,dds)的反馈查表方法实现脉冲成

型。

9.为实现上述发明目的,本发明一种基于dds技术的可调脉冲成型方法,其特征在于,包括以下步骤:

10.(1)、模块初始化;

11.(1.1)、初始化边沿成型控制模块的接口信号,包括使能信号、复位信号和时钟信号;

12.(1.2)、设置成型脉冲的目标幅度a、目标上升沿控制字δa

p

、目标下降沿控制字δad、目标边沿形状控制字s;

13.(2)、将使能信号置于高电平,触发边沿成型控制模块开始工作;

14.(3)、基带信号成型判决;

15.将外部的基带信号输入至边沿成型控制模,再利用时钟信号对基带信号采样,得到采样值;

16.利用采样值控制二选一多路选择器mux2-1,进而控制边沿成型控制模当前的成型模式;其中,当采样值为高电平,即逻辑1时,启动上升沿成型模式,进入步骤(4);当采样值为低电平,即逻辑0时,启动下降沿成型模式,进入步骤(5);

17.(4)、边沿成型控制模块启动上升沿成型;

18.(4.1)、上升沿累加器以目标边沿形状控制字s作为开始进行循环累加,累加步进为δa

p

,将累加结果作为查找地址addr

t

送入边沿形状存储区;循环累加的表达式如式(1)所示,式中addr0表示查表首地址;

[0019][0020]

(4.2)、将每一轮循环得到累加值addr

t

利用两级dff进行两拍时钟寄存;

[0021]

(4.3)、根据目标边沿形状控制字s使能边沿形状存储区存储有对应数据的rom的读使能,并按照查找地址addr

t

在边沿形状存储区查找对应的rom数据a

t

;

[0022][0023]

其中,s为目标边沿形状控制字,f(*)为存储边沿形状函数的采样值;

[0024]

(4.4)、将a

t

反馈给幅度比较器进行比较,如果a

t

小于目标幅度a与一个上升沿步进函数值f(δa

p

)之差时,则保持上升沿累加器工作状态,同时边沿成型控制模块输出a

t

作为t时刻的边沿形状否则,释放累加器停止使能信号,保持两拍时钟前输出累加值addr

t-2

作为查找地址,同时输出目标幅度a作为边沿成型控制模块输出电平值此时脉冲上升沿成型任务完成;

[0025]

其中,输出电平的表达式为:

[0026][0027]

(5)、边沿成型控制模块启动下降沿成型;

[0028]

(5.1)、下降沿减法器以目标边沿形状控制字s作为开始进行循环递减,递减步进

为δad,将递减结果作为查找地址addr

t

送入边沿形状存储区;

[0029]

其中,循环递减的表达式如式(4)所示,式中addr0表示查表首地址,addrh表示形状在高电平时的地址值;

[0030][0031]

(5.2)、将每一轮循环得到递减值addr

t

利用两级dff进行两拍时钟寄存;

[0032]

(5.3)、根据目标边沿形状控制字s使能边沿形状存储区存储有对应数据的rom的读使能,并按照查找地址addr

t

在边沿形状存储区查找对应的rom数据a

t

;

[0033][0034]

(5.4)、将a

t

反馈给幅度比较器进行比较,如果a

t

大于一个下降沿步进函数值f(δad)时,则保持下降沿减法器工作状态,同时边沿成型控制模块输出a

t

作为t时刻的边沿形状否则,释放减法器停止使能信号,输出addr0=0作为查找地址,同时输出0作为模块输出电平值此时脉冲下降沿成型任务完成;

[0035]

其中,输出电平的表达式为:

[0036][0037]

本发明的发明目的是这样实现的:

[0038]

本发明一种基于dds技术的可调脉冲成型方法,将脉冲边沿的形状与脉冲本身看作一个整体,边沿形状数据加载在rom的存储器中,将累加器输出的累加量变为对rom输入的读地址,从而构成基于dds的反馈查表法,由于rom中存放的数据预先生成,成型模块最终所产生的脉冲形状只与数据波形有关,因此采用dds的反馈查表法能够通用实现任意边沿脉冲的成型。

[0039]

同时,本发明一种基于dds技术的可调脉冲成型方法还具有以下有益效果:

[0040]

(1)、常规的反馈积分结构对非线性边沿的成型相对困难,结合dds产生任意波形的思想,在反馈积分法的结构中增加rom存储器模块,可以实现多种可调节的脉冲边沿成型;

[0041]

(2)、将脉冲边沿的形状与脉冲本身看作一个整体,可以认为脉冲成型是产生一种特定形状的波形,将边沿形状数据加载在存储器中,采用基于dds的查表方式能够有效减少逻辑设计复杂性,fpga片上用于运算的dsp资源占用也将降低;

[0042]

(3)、基于dds技术的反馈查表脉冲成型过程能够对任意函数型脉冲边沿进行成型,解决了非线性边沿成型问题,也避免了成型滤波器的复杂设计流程。通过比较,该方法占用资源相对较少,算法简单,效率高;

[0043]

(4)、在快速脉冲边沿成型要求场景下,本发明具有良好的应用价值,同时由于其能够基于fpga快速部署,对于缩短开发周期、降低成本具有重要意义;

[0044]

(5)、针对部分导航系统要求信号波形的任意性,将多组边沿数据进行存储,通过形状选择控制字进行边沿数据读取位置的确定,且根据脉冲边沿要求的准确度和任意性,

存储深度和数据位宽可灵活设置。

附图说明

[0045]

图1是传统的脉冲成型方法原理图;

[0046]

图2是本发明一种基于dds技术的可调脉冲成型方法原理图;

[0047]

图3是本发明一种基于dds技术的可调脉冲成型方法的另一种原理图;

[0048]

图4是单一形状边沿脉冲的成型结果图;

[0049]

图5是使用高斯型边沿成型函数成型结果图;

[0050]

图6是使用滚降升余弦型边沿成型函数成型结果图;

[0051]

图7是改变目标上升沿控制字或下降沿控制字的成型结果图;

[0052]

图8是改变目标幅度的成型结果图;

[0053]

图9是本发明方法与传统方法的资源占用对比图。

具体实施方式

[0054]

下面结合附图对本发明的具体实施方式进行描述,以便本领域的技术人员更好地理解本发明。需要特别提醒注意的是,在以下的描述中,当已知功能和设计的详细描述也许会淡化本发明的主要内容时,这些描述在这里将被忽略。

[0055]

实施例

[0056]

图2是本发明一种基于dds技术的可调脉冲成型方法原理图。

[0057]

常规的反馈积分结构对非线性边沿的成型相对困难,结合dds产生任意波形的思想,在反馈积分法的结构中增加rom存储器模块,可以实现多种可调节的脉冲边沿成型;在本实施例中,基于dds技术的可调脉冲成型主要针对单一形状边沿脉冲的成型和多形状边沿脉冲的成型,在rom中存入所需边沿函数数据,将累加器输出的累加量变为对rom输入的读地址,从而构成基于dds的反馈查表法。下面我们对两种成型方式进行详细说明,如图2所示,由于rom中存放的数据预先生成,成型模块最终所产生的脉冲形状只与数据波形有关,因此反馈查表法能够通用实现任意单一形状边沿脉冲的成型,具体包括以下步骤:

[0058]

s1、模块初始化;

[0059]

s1.1、初始化边沿成型控制模块的接口信号,包括使能信号、复位信号和时钟信号;

[0060]

s1.2、设置成型脉冲的目标幅度a=80、目标上升沿控制字δa

p

=25、目标下降沿控制字δad=25、目标边沿形状控制字s=0;

[0061]

s2、将使能信号置于高电平,触发边沿成型控制模块开始工作;

[0062]

s3、基带信号成型判决;

[0063]

将外部的基带信号输入至边沿成型控制模,再利用时钟信号对基带信号采样,得到采样值;

[0064]

利用采样值控制二选一多路选择器mux2-1,进而控制边沿成型控制模当前的成型模式;其中,当采样值为高电平,即逻辑1时,启动上升沿成型模式,进入步骤s4;当采样值为低电平,即逻辑0时,启动下降沿成型模式,进入步骤s5;

[0065]

s4、边沿成型控制模块启动上升沿成型;

[0066]

s4.1、上升沿累加器以目标边沿形状控制字s作为开始进行循环累加,累加步进为δa

p

,将累加结果作为查找地址addr

t

送入边沿形状存储区;循环累加的表达式如式(1)所示,式中addr0表示查表首地址;

[0067][0068]

s4.2、将每一轮循环得到累加值addr

t

利用两级dff进行两拍时钟寄存,用以消除rom模块本身特性带来的2拍时钟延迟;

[0069]

s4.3、根据目标边沿形状控制字s使能边沿形状存储区存储有对应数据的rom的读使能,并按照查找地址addr

t

在边沿形状存储区查找对应的rom数据a

t

;

[0070][0071]

其中,s为目标边沿形状控制字,f(*)为存储边沿形状函数的采样值,本例中为线性一次函数;

[0072]

s4.4、将a

t

反馈给幅度比较器进行比较,如果a

t

小于目标幅度a与一个上升沿步进函数值f(δa

p

)之差时,则保持上升沿累加器工作状态,同时边沿成型控制模块输出a

t

作为t时刻的边沿形状否则,释放累加器停止使能信号,保持两拍时钟前输出累加值addr

t-2

作为查找地址,同时输出目标幅度a作为边沿成型控制模块输出电平值此时脉冲上升沿成型任务完成;

[0073]

其中,输出电平的表达式为:

[0074][0075]

s5、边沿成型控制模块启动下降沿成型;

[0076]

s5.1、下降沿减法器以目标边沿形状控制字s作为开始进行循环递减,递减步进为δad,将递减结果作为查找地址addr

t

送入边沿形状存储区;

[0077]

其中,循环递减的表达式如式(4)所示,式中addr0表示查表首地址,addrh表示形状在高电平时的地址值;

[0078][0079]

s5.2、将每一轮循环得到递减值addr

t

利用两级dff进行两拍时钟寄存,用以消除rom模块本身特性带来的2拍时钟延迟;

[0080]

s5.3、根据目标边沿形状控制字s使能边沿形状存储区存储有对应数据的rom的读使能,并按照查找地址addr

t

在边沿形状存储区查找对应的rom数据a

t

;

[0081][0082]

s5.4、将a

t

反馈给幅度比较器进行比较,如果a

t

大于一个下降沿步进函数值f(δad)时,则保持下降沿减法器工作状态,同时边沿成型控制模块输出a

t

作为t时刻的边沿形状

否则,释放减法器停止使能信号,输出addr0=0作为查找地址,同时输出0作为模块输出电平值此时脉冲下降沿成型任务完成;

[0083]

其中,输出电平的表达式为:

[0084][0085]

完成上述流程,基本脉冲成型工作已经完成,成型结果如图4所示,图中clk为时钟信号;rstn为低电平有效复位信号;lvl_ctrl为目标幅度;p_d_n和p_d_p分别为边沿控制的下降沿步进和上升沿步进控制字;sig_in为基带数据信号;sig_out信号为成型脉冲。

[0086]

部分导航信号要求基带数据链的上升与下降边沿的形状不相同,不仅体现在边沿变化的快慢上,也体现在非线性边沿本身形状的不同上。针对这样的应用场景,仅使用一组边沿数据难以准确实现成型控制,即是能够实现,控制逻辑也非常复杂。为解决这一问题,可以将多组边沿数据进行存储,通过形状选择控制进行边沿数据读取位置的确定。这样的方案对存储单元的需求较高,通常根据脉冲边沿要求的准确度和任意性,具有更大的存储深度和数据位宽,对存储资源是一种挑战。因此,在单一形状边沿脉冲的成型过程的基础上进行延伸出了多形状边沿脉冲的成型过程,具体的成型流程如图3所示,我们可以在单一形状边沿脉冲的成型过程的基础上,分别改变不同的参数来实现,具体为:

[0087]

第一种方法:改变目标边沿形状控制字s,使能不同的rom模块的读使能信号,根据当前边沿成型的模式,查找对应rom表中的波形数据值,进行对应上升沿或下降沿的成型流程,从而实现多形状边脉冲的成型;在本实施例中,目标边沿形状控制字s为许可范围内0到3内的任意控制字,分别取s=1、s=2,当s=1时,系统使用高斯型边沿成型函数,s=2,系统使用滚降升余弦型边沿成型函数。控制效果如图5、图6所示,图中d_stp和r_stp分别为下降沿和上升沿步进控制字;tar_lvl为目标幅度;sig_data为基带数据信号;out_sig为成型脉冲输出信号;

[0088]

第二种方法:改变目标上升沿控制字δa

p

或下降沿控制字δad,根据δa

p

和δad在不同边沿成型模式时,调整的边沿累加器或减法器的式(1)和(4)的累加值,完成成型步骤s4和s5后,实现多形状边脉冲的成型;

[0089]

在本实施例中,分别取δa

p

=128和δad=64,以线性上升沿为例,设t

p

表示上升时间,y

max

=2000为输出脉冲要求的电平值,t=10ns为驱动时钟周期,调节过程表达式如式(7)所示,控制效果如图7所示

[0090][0091]

第三种方法:改变目标幅度a,按照步骤s3至s5描述过程后,实现多形状边脉冲的成型。设置目标幅度a=256,完成上述脉冲成型步骤,成型效果如图8所示。

[0092]

本发明在最终形成产品上,需要以数字逻辑rtl级电路形式实现,因此需要在完善的功能同时,平衡资源的占用率。最终本发明的实现平台为fpga芯片,因此将本发明方法与

传统方法的数字逻辑rtl级电路在相同fpga芯片进行功能测试和资源占用评估。通过对比验证,可以确定本发明在功能优势的同时,也具有较低的资源占用和面积优势。资源占用对比如图9所示。

[0093]

尽管上面对本发明说明性的具体实施方式进行了描述,以便于本技术领域的技术人员理解本发明,但应该清楚,本发明不限于具体实施方式的范围,对本技术领域的普通技术人员来讲,只要各种变化在所附的权利要求限定和确定的本发明的精神和范围内,这些变化是显而易见的,一切利用本发明构思的发明创造均在保护之列。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。