1.本发明涉及分布式存储领域,尤其涉及一种用于分布式内存加密装置和用于分布式内存解密装置。

背景技术:

2.随着云计算和大数据的不断发展,数据中心的cpu(中央处理器)、网络、内存等硬件资源消耗越来越大,各种各样的网络应用不断上云,国家对网络安全、数据隐私等问题越来越重视;公有云、混合云发展越来越好,如何保证客户敏感数据的安全显得尤为重要。内存加密技术一般是利用cpu的可信执行环境(trusted execution environment,简称tee)技术实现本地内存数据的加密,在服务器启动前设置bios选项,使能cpu的tee,开启以后该节点下所有对dimm内存数据的操作均会经过tee控制的加解密模块,数据在dimm内存中存储的是加密后的数据,数据被cpu读取后由tee控制的加解密模块解密后,交由cpu应用使用。intel的sgx(intel software guard extensions)技术是tee的一种实现,在sgx中用于执行代码的tee环境可以保证数据的机密性和完整性,只有特定用户和应用可以访问sgx中的代码和数据,tee环境包含cpu内专用的硬件逻辑以及专用的操作系统软件等,这种技术依赖于特定的cpu型号和专用的硬件平台已经完整的信任链。

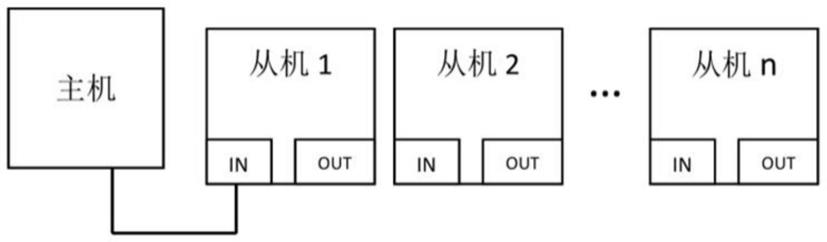

3.目前有两种基于fpga(field-programmable gate array,现场可编程门阵列)的数据加密卡方案:第一种方案需要专用的密码芯片对数据进行加密,请参照图1a所示,fpga主要负责在主机和密码芯片之间对于明文和密文的传输,fpga不对数据进行加密和解密的处理;还有一种基于fpga的数据加密方案请参照图1b所示,fpga内部实现了加解密功能,既可以对数据进行搬移,又进行明文和密文的处理,但依赖第三方提供密钥对来进行加解密服务。

4.现有技术存在以下缺陷:第一,使用tee技术的单节点内内存加密方案,需要特定的cpu型号才能支持,方案实现依赖底层硬件架构,软硬件耦合度大,更新升级麻烦,不同cpu厂商采用的tee技术接口形式不统一,技术框架不同,软件应用调用及平台移植开销大。第二,分布式内存加密过程中,数据加密完成后需要缓存,等待服务器的网卡将数据传输至其他节点,需要频繁拷贝内存数据,这不但增加了数据传输延时,还增加了系统能耗。第三,无论是单节点内采用tee技术的内存加解密,还是多节点分布式内存的加解密,传统的方案加解密的工作都是由cpu来执行的,这个过程中需要消耗大量的cpu资源来计算和内存资源来缓存。第四,传统加解密系统方案需要安全地存储密钥对,通常需要专门的存储资源来保存密钥对,有的缓存在内存中,这无疑增加了密钥对这种关键敏感信息的泄露风险,系统的可靠性无法得到保障。

技术实现要素:

5.有鉴于此,有必要针对以上技术问题,提供一种用于分布式内存加密装置和用于分布式内存解密装置。

6.根据本发明的第一方面,提供了一种用于分布式内存加密装置,在各个存储节点分别设置fpga芯片,每一存储节点的fpga芯片包括:

7.第一接口和第二接口,所述第一接口用于fpga芯片与本地存储节点通信,所述第二接口用于fpga芯片与其他存储节点通信;

8.dma引擎,所述dma引擎用于通过所述第一接口从本地存储节点的主机获取应用数据;

9.puf密钥生成模块,所述puf密钥生成模块用于通过所述第一接口从本地存储节点的主机获取puf电路输入激励并基于所述puf电路输入激励生成密钥;

10.加解密算法引擎,所述加解密算法引擎用于基于所述密钥对所述应用数据进行加密以生成加密数据;

11.收发包处理引擎,所述收发包处理引擎用于通过第一接口从本地存储节点的主机获取包头控制信息,并基于所述包头控制信息为所述加密数据添加信息头后通过所述第二接口发送给其他存储节点进行存储。

12.在一些实施例中,所述加密算法引擎为多个,不同的加密算法引擎对应不同的加密算法;

13.本地存储节点的主机通过所述第一接口向多个所述加密算法引擎发送算法选择信息以使被选中的加密算法引擎生效。

14.在一些实施例中,还包括fpga内存子系统;

15.所述fpga内存子系统用于缓存收发包处理引擎待处理的加密数据。

16.在一些实施例中,所述puf密钥生成模块包括puf电路模块和ecc编码模块;

17.所述puf电路模块用于基于所述puf电路输入激励生成响应数据;

18.所述ecc编码模块用于对所述ecc编码模块进行纠错以生成密钥。

19.在一些实施例中,所述第一接口为cxl接口或pcie接口,所述第二接口为mac网口。

20.根据本发明的第二方面,提供了一种用于分布式内存解密装置,在各个存储节点分别设置fpga芯片,每一存储节点的fpga芯片包括:

21.第一接口和第二接口,所述第一接口用于fpga芯片与本地存储节点通信,所述第二接口用于fpga芯片与其他存储节点通信;

22.收发包处理引擎,所述收发包处理引擎用于从其他存储节点接收数据包,并解析数据包的信息头以获取数据存储地址和数据包类型;

23.加解密算法引擎,所述加解密算法引擎用于基于所述数据包类型确定是否对所述数据包进行解密;

24.puf密钥生成模块,所述puf密钥生成模块用于在所述加解密算法引擎需要解密时通过所述第一接口从本地存储节点的主机获取puf电路输入激励,并基于所述puf电路输入激励生成密钥发送给所述加解密算法引擎以使所述加解密算法引擎基于密钥对所述数据包进行解密生成解密数据;

25.dma引擎,所述dma引擎用于从所述加解密算法引擎获取解密数据,并将所述解密数据通过所述第一接口发送给本地存储节点的主机以使本地存储节点的主机基于所述数据存储地址对所述解密数据进行存储。

26.在一些实施例中,所述加密算法引擎为多个,不同的加密算法引擎对应不同的加

密算法;

27.本地存储节点的主机通过所述第一接口向多个所述加密算法引擎发送算法选择信息以使被选中的加密算法引擎生效。

28.在一些实施例中,还包括fpga内存子系统;

29.所述fpga内存子系统用于缓存收发包处理引擎待处理的数据包。

30.在一些实施例中,所述puf密钥生成模块包括puf电路模块和ecc编码模块;

31.所述puf电路模块用于基于所述puf电路输入激励生成响应数据;

32.所述ecc编码模块用于对所述ecc编码模块进行纠错以生成密钥。

33.在一些实施例中,所述第一接口为cxl接口或pcie接口,所述第二接口为mac网口。

34.上述一种用于分布式内存加密装置,通过在传统服务器上增加一张基于fpga的数据处理板卡来对共享内存数据加解密,利用fpga内部硬件资源实现puf电路并生成随机数作为密钥,密钥无需存储管理,为云计算中分布式应用中数据的加解密提出了新思路。

35.此外,本发明提供的一种用于分布式内存解密装置,同样能实现上述技术效果,这里不再赘述。

附图说明

36.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的实施例。

37.图1a为一种传统基于fpga的分布式内存解密方案;

38.图1b为另一种传统基于fpga的分布式内存解密方案;

39.图2为本发明一个实施例提供的一种分布式内存加密装置的结构示意图。

40.图3a为本发明另一个实施例提供的puf密钥生成模块的功能框图;

41.图3b为本发明另一个实施例提供的基于ro的puf电路结构示意图;

42.图4为本发明又一个实施例提供的基于fpga的跨机架伺服器(rack)共享内存网络拓扑示意图。

43.【附图标记说明】

44.10:第一接口;

45.20:第二接口;

46.30:dma引擎;

47.40:puf密钥生成模块;21:puf电路模块;22:ecc编码模块;

48.50:加解密算法引擎;

49.60:收发包处理引擎;

50.70:fpga内存子系统。

具体实施方式

51.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明实施例进一步详细说明。

52.需要说明的是,本发明实施例中所有使用“第一”和“第二”的表述均是为了区分两个相同名称非相同的实体或者非相同的参量,可见“第一”“第二”仅为了表述的方便,不应理解为对本发明实施例的限定,后续实施例对此不再一一说明。

53.在一个实施例中,请参照图2所示,本发明提供了一种用于分布式内存加密装置,在各个存储节点分别设置fpga芯片,每一存储节点的fpga芯片包括:

54.第一接口10和第二接口20,所述第一接口10用于fpga芯片与本地存储节点通信,所述第二接口20用于fpga芯片与其他存储节点通信;

55.dma引擎30,所述dma引擎30用于通过所述第一接口10从本地存储节点的主机获取应用数据;

56.puf密钥生成模块40,所述puf密钥生成模块40用于通过所述第一接口10从本地存储节点的主机获取puf电路输入激励并基于所述puf电路输入激励生成密钥;其中,physical unclonable function物理不可克隆函数,简称puf。

57.加解密算法引擎50,所述加解密算法引擎50用于基于所述密钥对所述应用数据进行加密以生成加密数据;

58.收发包处理引擎60,所述收发包处理引擎60用于通过第一接口10从本地存储节点的主机获取包头控制信息,并基于所述包头控制信息为所述加密数据添加信息头后通过所述第二接口20发送给其他存储节点进行存储。

59.上述一种用于分布式内存加密装置,通过在传统服务器上增加一张基于fpga的数据处理板卡来对共享内存数据加解密,利用fpga内部硬件资源实现puf电路并生成随机数作为密钥,密钥无需存储管理,为云计算中分布式应用中数据的加解密提出了新思路。

60.在一些实施例中,所述加密算法引擎为多个,不同的加密算法引擎对应不同的加密算法;

61.本地存储节点的主机通过所述第一接口10向多个所述加密算法引擎发送算法选择信息以使被选中的加密算法引擎生效。

62.在一些实施例中,装置还包括fpga内存子系统70;

63.所述fpga内存子系统70用于缓存收发包处理引擎60待处理的加密数据。

64.在一些实施例中,请结合图3a所示,所述puf密钥生成模块40包括puf电路模块41和ecc编码模块42;

65.所述puf电路模块41用于基于所述puf电路输入激励生成响应数据;

66.所述ecc编码模块42用于对所述ecc编码模块42进行纠错以生成密钥。

67.在本实施例中,puf电路通常是利用芯片制造过程中不可控的工艺偏差导致的晶体管电学特性差异而设计的一种电路。ro puf电路是硅puf电路的一种,如图3b所示,其基本单元是相同数量的奇数个反相器和作为开关作用的与门构成的振荡环,通过比较约束在芯片不同位置的振荡环之间的频率差异得出一比特位的输出;通过比较多组振荡环的频率差,可以得到多位输出作为真随机序列,可以应用于芯片id的生成、加解密和ip核的保护等方面。

68.在一些实施例中,所述第一接口10为cxl接口或pcie接口,所述第二接口20为mac网口。

69.在又一个实施例中,本发明还提供了一种用于分布式内存解密装置,用于分布式

内存加密装置不同的是解密装置用于对接收到的数据包进行解密,fpga内结构与用于分布式内存解密装置结构相同,二者区别在于fpga内部各个模块之间协作,请继续参照图2所示,在各个存储节点分别设置fpga芯片,每一存储节点的fpga芯片包括:

70.第一接口10和第二接口20,所述第一接口10用于fpga芯片与本地存储节点通信,所述第二接口20用于fpga芯片与其他存储节点通信;

71.收发包处理引擎60,所述收发包处理引擎60用于从其他存储节点接收数据包,并解析数据包的信息头以获取数据存储地址和数据包类型;

72.加解密算法引擎50,所述加解密算法引擎50用于基于所述数据包类型确定是否对所述数据包进行解密;

73.puf密钥生成模块40,所述puf密钥生成模块40用于在所述加解密算法引擎50需要解密时通过所述第一接口10从本地存储节点的主机获取puf电路输入激励,并基于所述puf电路输入激励生成密钥发送给所述加解密算法引擎50以使所述加解密算法引擎50基于密钥对所述数据包进行解密生成解密数据;

74.dma引擎30,所述dma引擎30用于从所述加解密算法引擎50获取解密数据,并将所述解密数据通过所述第一接口10发送给本地存储节点的主机以使本地存储节点的主机基于所述数据存储地址对所述解密数据进行存储。

75.上述一种用于分布式内存解密装置,通过在传统服务器上增加一张基于fpga的数据处理板卡来对共享内存数据加解密,利用fpga内部硬件资源实现puf电路并生成随机数作为密钥,密钥无需存储管理,为云计算中分布式应用中数据的加解密提出了新思路。

76.在一些实施例中,所述加密算法引擎为多个,不同的加密算法引擎对应不同的加密算法;

77.本地存储节点的主机通过所述第一接口10向多个所述加密算法引擎发送算法选择信息以使被选中的加密算法引擎生效。

78.在一些实施例中,装置还包括fpga内存子系统70;

79.所述fpga内存子系统70用于缓存收发包处理引擎60待处理的数据包。

80.在一些实施例中,所述puf密钥生成模块40包括puf电路模块41和ecc编码模块42;

81.所述puf电路模块41用于基于所述puf电路输入激励生成响应数据;

82.所述ecc编码模块42用于对所述ecc编码模块42进行纠错以生成密钥。

83.在一些实施例中,所述第一接口10为cxl接口或pcie接口,所述第二接口20为mac网口。

84.在又一个实施例中,为了便于理解本发明的技术方案,请结合图4所示,本实施例提供了基于fpga的跨机架伺服器(rack)共享内存网络拓扑,具体以两个存储节点为例即本地存储节点和远端存储节点,本地存储节点和远端存储节点的fpga均采用相同的结构,下面以本地存储节点和远端存储节点之间的交互过程为例详细说上述用于分布式内存加密装置和用于分布式内存解密装置的工作过程:

85.1、在本地存储节点和远端存储节点fpga内设计puf密钥生成模块,包括puf电路模块和ecc编码模块;

86.2、本地存储节点上,本地应用数据需要加密时首先主机通过pcie通道配置puf密钥生成模块的puf电路输入激励,以得到该应用数据加密时所需的密钥;同时配置加解密算

法引擎选择算法和密钥和收发包处理模块内的包头信息;

87.3、然后通过pcie通道将数据由主机发送给fpga处理板,在fpga内部由dma引擎将主机上待处理数据读出;

88.4、加密算法引擎在得到密钥配置信息和dma引擎内缓存非空信息后,启动加密引擎,使用puf密钥生成模块产生的密钥对dma引擎发出的缓存数据进行加密;puf密钥生成模块仅对加解密算法引擎开放其密钥输出接口,fpga内部其他逻辑无法访问该端口,从而保证密钥的安全性。

89.5、加解密算法引擎可以部署多个以支持多个应用使用不同算法和密钥进行加解密处理,图中示例一种加解密算法处理。

90.6、数据经过加解密引擎加密处理后,通过收发包处理引擎,添加包含数据存储在远端节点位置地址和数据包类型标志(写内存数据请求包、读内存数据请求包和都内存数据响应包)的信息头,发送到400g mac模块。收发包引擎内支持建立多个收发队列对连接以同时支持多个加解密引擎的待发送数据,虽然图4仅示出一个收发包处理引擎队列,但是在具体实施过程中用户或客户可根据需求设定收发包处理引擎的数量,例如可以与加密算法引擎一一对应。

91.7、为保证数据安全存储在远端节点内存上,需保持应用数据加密状态传输与存储,远端存储节点收到加密后的应用内存数据后,通过收发包处理引擎解析数据包包头,获取数据存储地址、包类型(如写内存数据请求包);

92.8、远端存储节点上,fpga内加解密引擎判断收到的包为“写内存数据请求包”时,启动加解密算法引擎内部的bypass设置,不对接收到的数据进行解密处理,直接传送到dma引擎,再经过pcie通道存储在该节点对应内存地址上。

93.9、对远端存储节点内存进行读内存数据请求时,操作相反,远端存储节点主机收到“读内存数据请求包”后,由收发包处理引擎配置加解密算法引擎bypass设置,对即将读取待发送的内存数据进行bypass不解密处理;

94.10、然后启动dma引擎读取数据,给收发包处理引擎打包发送给请求节点;

95.11、请求节点收到“读内存数据响应包”后,使用相应算法和密钥对加密数据进行解密处理,解密完成后交给dma引擎写入到节点主机内存中。

96.结合上述实施例可以看出本发明的方案至少具备以下有益技术效果:(1)使用puf密钥生成模块产生真随机序列作为密钥对,用于对待发数据的加密和待收数据的解密,密钥对无需专门存储或缓存在外部存储设备上,提高了密钥及系统整体的安全可靠性;(2)由于puf电路的特性,不同fpga上实现的puf密钥生成模块,即使输入激励相同,得到的密钥也完全随机且不同;(3)将加解密任务由cpu卸载到基于fpga的数据处理板上,提高加解密的处理速度,降低cpu的负载率;(4)加解密算法引擎支持数据bypass功能,兼容传统使用cpu对内存数据进行加解密的方式,提高了数据处理的灵活性;(5)加解密算法引擎和收发包处理引擎支持多队列操作,以支持上层多个应用的使用不同加解密算法和密钥的场景;(6)puf密钥生成模块支持高可靠的自纠错编码,保证密钥对数据的完整性和可靠性;(7)fpga与主机之间采用pcie gen5标准,支持cxl总线协议,fpga与cpu之间具有cache一致性的特点。

97.以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例

中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

98.以上所述实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术专利的保护范围应以所附权利要求为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。