1.本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构的形成方法。

背景技术:

2.随着半导体集成电路(integrated circuit,ic)产业的快速成长,半导体技术在摩尔定律的驱动下持续地朝更小的工艺节点迈进,使得集成电路朝着体积更小、电路精密度更高、电路复杂度更高的方向发展。

3.在集成电路发展过程中,通常随着功能密度(即每一芯片的内连线结构的数量)逐渐增加的同时,几何尺寸(即利用工艺步骤可以产生的最小元件尺寸)也逐渐减小,这相应增加了集成电路制造的难度和复杂度。

4.目前,在技术节点不断缩小的情况下,如何提高形成于晶圆上的目标图形与设计图形的匹配度成为了一种挑战。

技术实现要素:

5.本发明实施例解决的问题是提供一种半导体结构的形成方法,有利于提高目标图形的图形精度、以及目标图形与设计图形的匹配度。

6.为解决上述问题,本发明实施例提供一种半导体结构的形成方法,包括:提供基底,包括用于形成目标图形的目标层;在所述基底上形成核心层,所述核心层包括用于形成抗刻蚀层的抗刻蚀区和用于形成牺牲层的牺牲区;对所述牺牲区的核心层进行离子掺杂,适于使所述牺牲区的核心层与抗刻蚀区的核心层的被刻蚀速率不同,位于所述牺牲区掺杂有离子的核心层用于作为牺牲层,位于所述抗刻蚀区未掺杂有离子的核心层用于作为抗刻蚀层;形成贯穿位于相邻所述牺牲区之间的核心层的沟槽,所述沟槽的侧壁暴露出位于所述牺牲区的核心层;在所述沟槽的侧壁上形成侧墙,位于所述沟槽侧壁的侧墙围成第一凹槽;在进行离子掺杂、以及形成所述第一凹槽之后,采用刻蚀工艺,去除所述牺牲层,在所述抗刻蚀层中形成贯穿抗刻蚀层的第二凹槽;其中,所述刻蚀工艺对所述牺牲层的刻蚀速率大于对所述抗刻蚀层的刻蚀速率;以所述抗刻蚀层和侧墙为掩膜,刻蚀所述第一凹槽和第二凹槽底部的所述目标层,形成目标图形。

7.可选的,在形成所述核心层之后,且在形成所述沟槽之前,对所述牺牲区的核心层进行离子掺杂;或者,在形成所述沟槽之后,且在形成所述侧墙之前,对所述牺牲区的核心层进行离子掺杂;或者,在形成所述侧墙之后,且在形成所述第二凹槽之前,对所述牺牲区的核心层进行离子掺杂。

8.可选的,对所述牺牲区的核心层进行离子掺杂的离子包括硼离子、磷离子、砷离子或氩离子。

9.可选的,对所述牺牲区的核心层进行离子掺杂的步骤中,所述牺牲区的核心层中的离子掺杂浓度为1.0e15原子每立方厘米至1.0e20原子每立方厘米。

10.可选的,采用离子注入工艺,对所述牺牲区的核心层进行离子掺杂。

11.可选的,所述离子注入工艺的参数包括:注入能量为1kev至100kev,注入方向与基底表面法线的夹角为0

°

至5

°

。

12.可选的,采用湿法刻蚀工艺,去除所述牺牲层。

13.可选的,所述湿法刻蚀工艺采用的刻蚀溶液包括氢氟酸、硝酸和醋酸的混合溶液。

14.可选的,所述湿法刻蚀工艺所采用的氢氟酸、硝酸和醋酸的混合溶液中,所述硝酸和氢氟酸之间的分子比率至少为2,所述硝酸的摩尔百分比至少为14%。

15.可选的,所述湿法刻蚀工艺所采用的氢氟酸、硝酸和醋酸的混合溶液中,氢氟酸的摩尔百分比为0.2%至6%,硝酸的摩尔百分比为14%至28%,醋酸的摩尔百分比为66%至86%。

16.可选的,所述湿法刻蚀工艺所采用的氢氟酸、硝酸和醋酸的混合溶液中,氢氟酸和醋酸的体积比例为1:8至1:100,氢氟酸和硝酸的体积比例为1:3至1:50。

17.可选的,形成所述核心层的步骤中,所述核心层的材料包括无定形硅、氮化硅、无定形锗、氧化硅、氮氧化硅、氮化碳、多晶硅、碳化硅、碳氮化硅或碳氮氧化硅。

18.可选的,对所述牺牲区的核心层进行离子掺杂的步骤包括:形成覆盖所述抗刻蚀区的遮挡层,所述遮挡层暴露出所述牺牲区;以所述遮挡层为掩膜,对所述核心层进行所述离子掺杂。

19.可选的,所述目标层为介电层;以所述抗刻蚀层和侧墙为掩膜,刻蚀所述第一凹槽和第二凹槽底部的所述介电层,形成互连槽;所述半导体结构的形成方法还包括:在形成所述互连槽之后,在所述互连槽中形成金属线。

20.与现有技术相比,本发明实施例的技术方案具有以下优点:

21.本发明实施例提供的半导体结构的形成方法中,对所述牺牲区的核心层进行离子掺杂,适于使所述牺牲区的核心层与抗刻蚀区的核心层的被刻蚀速率不同,从而通过对核心层进行离子掺杂的方式,形成位于牺牲区的牺牲层和位于抗刻蚀区的抗刻蚀层,不仅有利于简化工序,而且通过离子掺杂的方式使牺牲层与抗刻蚀层的被刻蚀速率不同,在采用刻蚀工艺去除牺牲层的步骤中,所述刻蚀工艺对所述牺牲层的刻蚀速率大于对所述抗刻蚀层的刻蚀速率,有利于降低去除牺牲层的难度、提高对去除牺牲层的工艺控制性,第二凹槽的图形精度也得到了提高,还使得抗刻蚀层能够在去除牺牲层的步骤中被保留,相应保障抗刻蚀层作为图形化目标层的掩膜的作用,在刻蚀第一凹槽和第二凹槽底部的目标层以形成目标图形的步骤中,有利于获得较高的图形传递精度和较好的图形化效果,进而提高了目标图形的图形精度、以及提高目标图形与设计图形的匹配度。

附图说明

22.图1至图24是本发明半导体结构的形成方法一实施例中各步骤对应的结构示意图。

具体实施方式

23.由背景技术可知,如何提高形成于晶圆上的目标图形与设计图形的匹配度成为了一种挑战。

24.为了解决所述技术问题,本发明实施例提供一种半导体结构的形成方法,包括:提

供基底,包括用于形成目标图形的目标层;在所述基底上形成核心层,所述核心层包括用于形成抗刻蚀层的抗刻蚀区和用于形成牺牲层的牺牲区;对所述牺牲区的核心层进行离子掺杂,适于使所述牺牲区的核心层与抗刻蚀区的核心层的被刻蚀速率不同,位于所述牺牲区掺杂有离子的核心层用于作为牺牲层,位于所述抗刻蚀区未掺杂有离子的核心层用于作为抗刻蚀层;形成贯穿位于相邻所述牺牲区之间的核心层的沟槽,所述沟槽的侧壁暴露出位于所述牺牲区的核心层;在所述沟槽的侧壁上形成侧墙,位于所述沟槽侧壁的侧墙围成第一凹槽;在进行离子掺杂、以及形成所述第一凹槽之后,采用刻蚀工艺,去除所述牺牲层,在所述抗刻蚀层中形成贯穿抗刻蚀层的第二凹槽;其中,所述刻蚀工艺对所述牺牲层的刻蚀速率大于对所述抗刻蚀层的刻蚀速率;以所述抗刻蚀层和侧墙为掩膜,刻蚀所述第一凹槽和第二凹槽底部的所述目标层,形成目标图形。

25.本发明实施例提供的半导体结构的形成方法中,对所述牺牲区的核心层进行离子掺杂,适于使所述牺牲区的核心层与抗刻蚀区的核心层的被刻蚀速率不同,从而通过对核心层进行离子掺杂的方式,形成位于牺牲区的牺牲层和位于抗刻蚀区的抗刻蚀层,不仅有利于简化工序,而且通过离子掺杂的方式使牺牲层与抗刻蚀层的被刻蚀速率不同,在采用刻蚀工艺去除牺牲层的步骤中,所述刻蚀工艺对所述牺牲层的刻蚀速率大于对所述抗刻蚀层的刻蚀速率,有利于降低去除牺牲层的难度、提高对去除牺牲层的工艺控制性,第二凹槽的图形精度也得到了提高,还使得抗刻蚀层能够在去除牺牲层的步骤中被保留,相应保障抗刻蚀层作为图形化目标层的掩膜的作用,在刻蚀第一凹槽和第二凹槽底部的目标层以形成目标图形的步骤中,有利于获得较高的图形传递精度和较好的图形化效果,进而提高了目标图形的图形精度、以及提高目标图形与设计图形的匹配度。

26.为使本发明实施例的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

27.图1至图24是本发明半导体结构的形成方法一实施例中各步骤对应的结构示意图。

28.参考图1,提供基底(未标示),包括用于形成目标图形的目标层100。

29.所述基底用于为后续工艺制程提供平台。

30.所述目标层100为待进行图形化以形成目标图形的膜层。

31.其中,目标图形可以为栅极结构、后段制程中的互连槽、鳍式场效应晶体管(finfet)中的鳍部、全包围栅极(gaa)晶体管或叉型栅极晶体管(forksheet)中的沟道叠层、硬掩膜(hard mask,hm)层等图形。

32.本实施例中,目标层100为介电层。后续图形化介电层,在介电层中形成多个互连槽,之后在互连槽中形成金属线,介电层用于实现相邻金属线之间的电隔离。相应地,所述目标图形为互连槽。介电层相应为金属层间介质(inter metal dielectric,imd)层。介电层的材料为低k介质材料、超低k介质材料、氧化硅、氮化硅或氮氧化硅等。

33.本实施例中,基底中可以形成有晶体管、电容器等半导体器件,基底中还可以形成有电阻结构、导电结构等功能结构。

34.本实施例中,基底还包括位于所述目标层100上的硬掩膜材料层110、以及位于硬掩膜材料层110上的刻蚀停止层120。

35.所述硬掩膜材料层110用于经后续图形化工艺后,形成硬掩膜层。具体地,后续形

成第一凹槽和第二凹槽后,能够先将第一凹槽和第二凹槽的图形传递到硬掩膜材料层110中形成硬掩膜层,再以硬掩膜层为掩膜刻蚀目标层100,即使后续抗刻蚀层和侧墙在图形化工艺的过程中被消耗,还能够继续以硬掩膜层为掩膜刻蚀所述目标层100,有利于提高图形化的工艺稳定性和工艺效果。

36.本实施例中,所述硬掩膜材料层110的材料为氮化硅。在其他实施例中,所述硬掩膜材料层的材料还可以为氧化硅、氮氧化硅、碳化硅、钛、氧化钛、氮化钛、钽、氧化钽、氮化钽、氮化硼、氮化铜、氮化铝或氮化钨等材料。

37.后续制程包括进行多次的刻蚀步骤,所述刻蚀停止层120用于在后续刻蚀工艺中,起到定义刻蚀停止位置的作用,从而有利于减小对所述目标层100的损耗、提高刻蚀工艺的深度一致性,进而提高后续图形化工艺的效果。

38.本实施例中,所述刻蚀停止层120的材料为氧化硅。在其他实施例中,所述刻蚀停止层的材料还可以为氮化硅、氧化铝、氮化钛、氮化钨或氮化铝等。

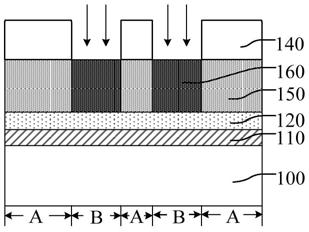

39.参考图2和图3,图2为俯视图,图3是图2沿yy割线的剖面图,在所述基底上形成核心层(mandrel)130,所述核心层130包括用于形成抗刻蚀层的抗刻蚀区a和用于形成牺牲层的牺牲区b。

40.后续对核心层130进行离子掺杂,形成所述抗刻蚀层和牺牲层。

41.具体地,本实施例中,所述牺牲区b的核心层130用于经后续离子掺杂,形成牺牲层,所述抗刻蚀区a的未掺杂有离子的剩余核心层130用于作为抗刻蚀层。

42.因此,所述抗刻蚀区a和所述牺牲区b的区域划分,依据后续抗刻蚀层和牺牲层的形成位置和图形而定。

43.本实施例中,所述核心层130中部分的区域用于作为所述牺牲区b,剩余的区域用于作为所述抗刻蚀区a。

44.本实施例中,所述牺牲区b的数量为多个,所述牺牲区b沿横向(如图2中x方向)所示,且沿纵向(如图2中y方向所示)间隔排列,所述横向与纵向相垂直。作为一种示例,图中示意出了两个所述牺牲区b。

45.所述核心层130的材料包括无定形硅、氮化硅、无定形锗、氧化硅、氮氧化硅、氮化碳、多晶硅、碳化硅、碳氮化硅或碳氮氧化硅。本实施例中,所述核心层130的材料为无定形硅。

46.本实施例中,采用沉积工艺(例如:化学气相沉积工艺),形成所述核心层130。

47.参考图4至图9,对所述牺牲区b的核心层130进行离子掺杂,适于使所述牺牲区b的核心层130与所述抗刻蚀区a的核心层130的被刻蚀速率不同,位于所述牺牲区b掺杂有离子的核心层130用于作为牺牲层160,位于所述抗刻蚀区a未掺杂有离子的核心层130用于作为抗刻蚀层150。

48.后续步骤还包括:形成贯穿位于相邻所述牺牲区b之间的核心层130的沟槽;在所述沟槽的侧壁上形成侧墙,位于所述沟槽侧壁的侧墙围成第一凹槽;去除所述牺牲层形成第二凹槽。

49.本实施例中,对所述牺牲区b的核心层130进行离子掺杂,适于使所述牺牲区b的核心层130与抗刻蚀区a的核心层130的被刻蚀速率不同,从而通过对核心层130进行离子掺杂的方式,形成所述牺牲层160和抗刻蚀层150,不仅有利于简化工序,而且通过离子掺杂的方

式使牺牲层160与抗刻蚀层150的被刻蚀速率不同,在后续采用刻蚀工艺去除牺牲层160的步骤中,所述刻蚀工艺对所述牺牲层160的刻蚀速率大于对所述抗刻蚀层150的刻蚀速率,有利于降低去除牺牲层160的难度、提高对去除牺牲层160的工艺控制性,第二凹槽的图形精度也得到了提高,还使得抗刻蚀层150能够在去除牺牲层160的步骤中被保留,相应保障所述抗刻蚀层150作为图形化目标层100的掩膜的作用,在刻蚀第一凹槽和第二凹槽底部的目标层100以形成目标图形的步骤中,有利于获得较高的图形传递精度和较好的图形化效果,进而提高了目标图形的图形精度、以及提高目标图形与设计图形的匹配度。

50.其中,本实施例中,使所述牺牲区b的核心层130与抗刻蚀区a的核心层130的被刻蚀速率不同指的是,在同一刻蚀工艺条件下,所述牺牲区b的核心层130与所述抗刻蚀区a的核心层130的被刻蚀速率不同。

51.本实施例中,所述牺牲区b的核心层130与抗刻蚀区a的核心层130的被刻蚀速率不同,从而后续易于通过选用特定的刻蚀工艺,使得刻蚀工艺对所述牺牲层160和抗刻蚀层150之间具有较高的刻蚀选择比,相应降低后续去除所述牺牲层160的难度、增大形成第二凹槽的工艺窗口。

52.作为一种示例,在形成所述核心层130之后,且在形成沟槽之前,对所述牺牲区b的核心层130进行离子掺杂。

53.在其他实施例中,还可以在形成所述沟槽之后,且在形成侧墙之前,对所述牺牲区的核心层进行离子掺杂;或者,在形成侧墙之后,且在形成第二凹槽之前,对所述牺牲区的核心层进行离子掺杂。

54.本实施例中,所述离子掺杂的掺杂深度为所述核心层130的整个厚度。

55.本实施例中,对所述牺牲区b的核心层130进行离子掺杂的离子包括硼离子、磷离子、砷离子或氩离子。作为一种示例,对所述牺牲区b的核心层130进行离子掺杂的离子为硼离子。

56.在所述核心层130中掺杂所述离子时,发明人发现,当所述核心层130中的离子掺杂浓度大于一掺杂浓度值时,在选用特定的刻蚀工艺时,所述刻蚀工艺对掺杂有离子的核心层130材料的刻蚀速率,远远大于对未掺杂有离子的所述核心层130材料的刻蚀速率,所述刻蚀工艺对未掺杂有离子的核心层130的刻蚀速率甚至接近停止,从而使得所述刻蚀工艺对所述牺牲层160和抗刻蚀层150具有较高的刻蚀选择比,进而保证后续去除所述牺牲层160的工艺难度低、工艺窗口大,所述抗刻蚀层150能够在去除所述牺牲层160的步骤中被保留。

57.具体地,本实施例中,所述核心层130的材料为无定形硅,在无定形硅中掺杂硼离子,能够改变无定形硅材料的被刻蚀速率,从而使得牺牲层160和抗刻蚀层150的被刻蚀速率不同。

58.为此,对所述牺牲区b的核心层130进行离子掺杂的步骤中,所述牺牲区b的核心层130中的离子掺杂浓度不宜过小,否则容易导致掺杂有离子的核心层130和未掺杂离子的所述核心层130的被刻蚀速率差异不明显,进而容易降低对后续去除所述牺牲层160的工艺窗口的增大效果。为此,本实施例中,所述牺牲区b的核心层130进行离子掺杂的步骤中,所述牺牲区b的核心层130中的离子掺杂浓度为1.0e15原子每立方厘米至1.0e20原子每立方厘米。

59.作为一种示例,所述牺牲层160中掺杂有硼离子,所述牺牲层160中的硼离子的掺杂浓度为1.0e19原子每立方厘米。

60.本实施例中,所述牺牲区b的数量为多个,因此,所述牺牲层160的数量也为多个。多个所述牺牲层160沿横向延伸,且沿纵向间隔排列。

61.本实施例中,对所述牺牲区b的核心层130进行离子掺杂的步骤包括:

62.如图4和图5所示,图4为俯视图,图5为图4沿yy割线的剖面图,形成覆盖所述抗刻蚀区a的遮挡层140,所述遮挡层140暴露出所述牺牲区b。

63.所述遮挡层140用于对第二区域的核心材料层130起到遮挡的作用。

64.本实施例中,所述遮挡层140的材料为旋涂碳(spin-on carbon,soc)。在其他实施例中,所述遮挡层的材料还可以为其他有机材料,例如:barc(bottom anti-reflective coating,底部抗反射涂层)材料、odl(organic dielectric layer,有机介电层)材料等。

65.作为一种示例,形成所述遮挡层140的步骤包括:在所述核心层130上形成初始遮挡层(图未示);在所述初始遮挡层上形成图形化层(图未示);以所述图形化层为掩膜,图形化所述初始遮挡层,形成所述遮挡层140。

66.本实施例中,形成所述初始遮挡层的工艺包括旋涂(spin-on)工艺。

67.本实施例中,所述图形化层的材料包括光刻胶,所述图形化层的形成工艺包括光刻胶涂布、曝光、显影等光刻工艺制程。

68.本实施例中,图形化所述初始遮挡层的工艺包括各向异性的干法刻蚀工艺。各向异性的干法刻蚀工艺有利于提高图形传递的精度。

69.如图6和图7所示,图6为俯视图,图7为图6沿yy割线的剖面图,以所述遮挡层140为掩膜,对所述核心层130进行所述离子掺杂。

70.本实施例中,所述遮挡层140暴露出所述牺牲区b,因此,对所述牺牲区b的核心层130进行离子掺杂。

71.本实施例中,采用离子注入工艺,对所述牺牲区b的核心层130进行离子掺杂。离子注入工艺简单、易操作,且易于通过调整注入方向和能量,使得掺杂深度满足工艺需求,同时也易于通过调整注入剂量,使得离子掺杂浓度满足工艺需求。

72.本实施例中,所述离子注入工艺的参数包括:注入能量为1kev至100kev,注入方向与基底表面法线的夹角为0

°

至5

°

。

73.所述离子注入工艺的注入能量不宜过小,也不宜过大。如果所述离子注入工艺的注入能量过小,容易导致离子注入深度不足,进而容易导致掺杂有离子的核心层130和未掺杂离子的核心层130的被刻蚀速率的差异不明显;如果所述离子注入工艺的注入能量过大,容易造成过大的注入损伤、产生副作用。为此,本实施例中,所述离子注入工艺的注入能量为1kev至100kev。

74.所述离子注入方向与基底表面法线的夹角不宜过大,否则容易增加将离子注入到所述抗刻蚀区a的核心层130中的风险。为此,本实施例中,所述离子注入工艺的注入方向与基底表面法线的夹角为0

°

至5

°

。

75.如图8和图9所示,图8为俯视图,图9是图8沿yy割线的剖面图,去除所述遮挡层140。

76.去除所述遮挡层140,从而暴露出所述抗刻蚀层150和牺牲层160的顶面,以便于后

续工艺制程的进行。

77.具体地,可选用灰化工艺和湿法去胶工艺中的一种或两种,去除所述遮挡层140。

78.参考图10至图15,形成贯穿位于相邻所述牺牲区b之间的核心层130的沟槽180,所述沟槽180的侧壁暴露出位于所述牺牲区b的核心层130。

79.所述沟槽180的侧壁用于为后续形成侧墙提供支撑作用,且所述沟槽180与后续的侧墙共同定义第一凹槽的形状和位置。具体地,后续在所述沟槽180的侧壁上形成侧墙,位于所述沟槽180侧壁的侧墙围成第一凹槽。

80.本实施例中,在形成所述沟槽180之前,对所述牺牲区b的核心层130进行离子掺杂,形成所述牺牲层160和抗刻蚀层150,因此,所述沟槽180贯穿位于相邻所述牺牲层160之间的抗刻蚀层150,所述沟槽180的侧壁暴露出所述牺牲层160。

81.作为一种示例,在实际工艺中,所述沟槽180还可以沿纵向贯穿部分宽度的所述牺牲区b的核心层130(即所述牺牲层160)。

82.本实施例中,所述沟槽180的数量也为多个,多个所述沟槽180沿横向延伸,且沿所述纵向与所述牺牲区b的核心层130间隔排列。

83.本实施例中,沿所述纵向,位于边缘位置的所述牺牲区b作为边缘牺牲区,所述沟槽180还位于所述边缘牺牲区远离相邻所述牺牲区b的一侧的核心层130中。

84.本实施例中,形成所述沟槽180的步骤包括:

85.如图10和图11所示,图10为俯视图,图11为图10沿yy割线的剖面图,在所述抗刻蚀层150和牺牲层160上形成掩膜层170,所述掩膜层170中形成有露出相邻所述牺牲层160之间的部分抗刻蚀层150的图形开口175。

86.所述掩膜层170用于作为刻蚀所述抗刻蚀层150以形成沟槽的掩膜。

87.具体地,所述掩膜层170形成于所述刻蚀停止层120上。

88.本实施例中,所述掩膜层170的材料为旋涂碳。关于所述掩膜层170的材料以及形成步骤可参考前述对遮挡层的相应描述,在此不再赘述。

89.本实施例中,所述掩膜层170还露出部分宽度的牺牲层160、以及与牺牲层160相邻的部分抗刻蚀层150。

90.如图12和图13所示,图12为俯视图,图13是图12沿yy割线的剖面图,以所述掩膜层170为掩膜,去除所述图形开口175底部的所述抗刻蚀层150,形成沟槽180。

91.本实施例中,采用各向异性的干法刻蚀工艺(例如:等离子体刻蚀工艺),去除所述图形开口175底部的所述抗刻蚀层150。等离子体刻蚀工艺的剖面控制性较好、刻蚀精度高,有利于提高所述沟槽180的图形精度和剖面形貌质量,而且还有利于提高刻蚀效率。

92.本实施例中,所述图形开口175还露出部分宽度的牺牲层160、以及与牺牲层160相邻的部分抗刻蚀层150,因此,去除所述图形开口175底部的所述抗刻蚀层150的过程中,还去除部分的所述牺牲层160以及与所述牺牲层160相邻的部分所述抗刻蚀层150。

93.相应地,所述沟槽180还形成在与所述牺牲层160相邻的所述抗刻蚀层150中。具体地,本实施例中,所述沟槽180的数量为多个,且多个所述沟槽180之间沿纵向间隔排布。

94.如图14和图15所示,图14为俯视图,图15是图14沿yy割线的剖面图,去除所述掩膜层170。

95.去除所述掩膜层170,以便于后续工艺制程的进行。具体地,去除所述掩膜层170的

工艺包括灰化工艺和湿法去胶工艺中的一种或两种。

96.结合参考图16,作为一种示例,所述半导体结构的形成方法还包括:在形成所述核心层130之后,在形成侧墙之前,形成沿纵向贯穿所述牺牲区b的核心层130的切割槽200,所述切割槽200沿横向分割所述牺牲区b的核心层130。

97.所述切割槽200沿横向分割所述牺牲区b的核心层130,从而在进行离子掺杂形成抗刻蚀层150和牺牲层160之后,所述切割槽200沿横向分割所述牺牲层160,之后在形成侧墙的步骤中,所述侧墙还能够填充于所述切割槽200内,位于所述切割槽200中的侧墙用于作为分割层,用于沿横向分割所述牺牲层160,进而在后续去除所述牺牲层160形成第二凹槽后,所述分割层沿横向分割所述第二凹槽,有利于使相邻的第二凹槽之间实现更小的距离。

98.作为一种示例,在形成所述沟槽180和进行离子掺杂之后,形成侧墙之前,形成所述切割槽200。相应地,所述切割槽200沿纵向贯穿所述牺牲层160,沿横向所述切割槽200分割所述牺牲层160。

99.在其他实施例中,还可以在形成核心层之后,进行离子掺杂之前,形成所述切割槽;或者,在进行离子掺杂之后,形成所述沟槽之前,形成所述切割槽。

100.参考图17至图18,图17为俯视图,图18为图17沿yy割线的剖面图,在所述沟槽180的侧壁上形成侧墙190,位于所述沟槽180侧壁的侧墙190围成第一凹槽210。

101.所述侧墙190用于作为后续刻蚀所述目标层100的部分掩膜。本实施例中,通过所述侧墙190和沟槽180共同定所述义第一凹槽210的图形,在形成所述沟槽180的过程中,所述沟槽180的尺寸相对较大,对沟槽180的尺寸精度要求低,有利于降低形成所述沟槽180的难度、增大工艺窗口。

102.后续步骤还包括:去除所述牺牲层160,形成第二凹槽。本实施例在形成第二凹槽之前,通过形成侧墙190,从而后续能够实现所述第一凹槽210和第二凹槽之间的隔离,并使得相邻所述第一凹槽210和第二凹槽的间距满足设计最小间隔;相应地,后续刻蚀所述第一凹槽210和第二凹槽底部的目标层100后,有利于使所述目标层100中形成的目标图形之间的间距满足最小设计间隔。

103.本实施例中,所述侧墙190还填充于所述切割槽200中,位于所述切割槽200中的侧墙190用于作为分割层,用于分割所述牺牲层160,相应后续去除所述牺牲层160形成第二凹槽后,所述分割层用于分割所述第二凹槽,有利于使得所述第二凹槽之间实现更小的距离。

104.所述侧墙190的材料可以为氧化钛、氮化钛、氧化硅、氮化硅或氧化铝。本实施例中,所述侧墙190的材料为氧化钛。氧化钛材料与无定型硅或氮化硅的刻蚀选择性比较高,所述侧墙190能够在后续去除牺牲层160的步骤中被保留,且所述侧墙190能够作为刻蚀目标层100的掩膜。

105.本实施例中,形成所述侧墙190的步骤包括:在所述沟槽180的侧壁和底部、以及所述抗刻蚀层150和牺牲层160顶面上形成侧墙材料层(图未示);去除位于所述沟槽180底部、以及所述抗刻蚀层150和牺牲层160顶面的侧墙材料层,位于所述沟槽180侧壁上的剩余侧墙材料层用于作为所述侧墙190。

106.本实施例中,采用原子层沉积工艺形成所述侧墙材料层。原子层沉积工艺的阶梯覆盖能力强,有利于提高所述侧墙材料层在所述沟槽180侧壁上的覆盖能力,而且通过选用

原子层沉积工艺,还有利于提高所述侧墙材料层的厚度均匀性,并利于精确控制所述侧墙190的厚度。

107.本实施例中,采用干法刻蚀工艺(例如:各向异性干法刻蚀工艺),去除位于所述沟槽180底部、以及抗刻蚀层150和牺牲层160顶面的侧墙材料层。各向异性干法刻蚀工艺具有各向异性刻蚀的特性,从而能够在无掩膜的情况下,将位于所述沟槽180底部、以及所述抗刻蚀层150和所述牺牲层160顶面的所述侧墙材料层去除,同时使得位于所述沟槽180侧壁上的所述侧墙材料层被保留。

108.作为一种示例,所述侧墙190的厚度为50埃米至300埃米,所述侧墙190的厚度较小,从而使得相邻的第一凹槽210和第二凹槽220之间实现较小的间隔。其中,所述侧墙190的厚度指的是:所述侧墙190沿垂直于所述沟槽180侧壁方向上的尺寸。

109.参考图19和图20,图19为俯视图,图20为图19沿yy割线的剖面图,在进行离子掺杂、以及形成第一凹槽210之后,采用刻蚀工艺,去除所述牺牲层160,在抗刻蚀层150中形成贯穿抗刻蚀层150的第二凹槽220;其中,所述刻蚀工艺对所述牺牲层160的刻蚀速率大于对所述抗刻蚀层150的刻蚀速率。

110.所述第二凹槽220和所述第一凹槽210共同定义目标图形的图形。在形成所述第二凹槽220和第一凹槽210后,所述侧墙190和剩余所述抗刻蚀层150用于作为图形化目标层100的掩膜。

111.本实施例中,所述第二凹槽220的数量为多个。所述第二凹槽220沿横向(如图19中x方向所示)延伸,沿纵向多个所述第二凹槽220沿纵向(如图19中y方向所示)与所述第一凹槽210间隔排列,且所述第二凹槽220与所述第一凹槽210之间由所述侧墙190相隔离,有利于使得所述第二凹槽220与第一凹槽210之间满足设计最小间隔。

112.本实施例中,对所述牺牲区b的核心层130进行离子掺杂,适于使所述牺牲区b的核心层130(即所述牺牲层160)与所述抗刻蚀区a的核心层130(即所述抗刻蚀层150)的被刻蚀速率不同,不仅有利于简化工序,而且通过离子掺杂的方式使所述牺牲层160与抗刻蚀层150的被刻蚀速率不同,相应地,在采用刻蚀工艺去除所述牺牲层160的步骤中,所述刻蚀工艺对所述牺牲层160的刻蚀速率大于对所述抗刻蚀层150的刻蚀速率,有利于降低去除牺牲层160的难度、提高对去除所述牺牲层160的工艺控制性,所述第二凹槽220的图形精度也得到了提高,还使得所述抗刻蚀层150能够在去除所述牺牲层160的步骤中被保留,相应保障所述抗刻蚀层150作为图形化所述目标层100的掩膜作用,在刻蚀所述第一凹槽210和第二凹槽220底部的所述目标层100以形成目标图形的步骤中,有利于获得较高的图形传递精度和较好的图形化效果,进而提高了目标图形的图形精度、以及提高目标图形与设计图形的匹配度。

113.此外,本实施例在形成所述沟槽180后,在所述沟槽180的侧壁形成侧墙190,使位于所述沟槽180侧壁的侧墙190围成所述第一凹槽210,之后去除牺牲层160形成所述第二凹槽220,本实施例通过分别在不同步骤中形成第一凹槽210和第二凹槽2200,有利于降低形成第一凹槽210和第二凹槽220的难度、增大工艺窗口(例如:改善光学临近效应),使得第一凹槽210和第二凹槽220的图形精度得到保障,相应的,后续刻蚀所述第一凹槽210和第二凹槽220底部的目标层100形成目标图形后,所述目标图形的图形精度也得到了提高。

114.本实施例中,去除所述牺牲层160形成第二凹槽220后,沿横向所述第二凹槽220被

所述分割层分割,有利于使得沿横向相邻所述第二凹槽220之间实现更小的距离,即所述第二凹槽220在头对头(head to head,hth)的位置处实现更小的线端(line end)距离,提高了目标图形的设计自由度。

115.本实施例中,采用湿法刻蚀工艺去除所述牺牲层160。具体地,本实施例中,所述牺牲层160中掺杂有离子,所述湿法刻蚀工艺对掺杂有离子的核心层130与未掺杂离子的核心层130的刻蚀速率不同,所述湿法刻蚀工艺对所述抗刻蚀层150和牺牲层160具有较大的刻蚀选择比,从而在去除所述牺牲层160的过程中,抗刻蚀层150能够被保留。

116.本实施例中,所述湿法刻蚀工艺采用的刻蚀溶液包括氢氟酸(hydrofluoric acid)、硝酸(nitric acid)和醋酸(acetic acid)的混合溶液,即hna溶液。和对未掺杂有离子的无定形硅的刻蚀速率相比,hna溶液对掺杂有所述离子的无定形硅的刻蚀速率更大,通过选用hna溶液,有利于提高湿法刻蚀工艺对掺杂有离子的无定形硅与未掺杂离子的无定形硅的刻蚀选择比,即提高所述牺牲层160和所述抗刻蚀层150的刻蚀选择比,从而显著降低去除所述牺牲层160的工艺难度、降低所述抗刻蚀层150受损的概率,进而显著提高所述第二凹槽220的图形精度和图形质量,还有利于提高所述第一凹槽210的图形完整度。

117.作为一种示例,所述湿法刻蚀工艺所采用的氢氟酸、硝酸和醋酸的混合溶液中,氢氟酸和醋酸的体积比例为1:8至1:100,氢氟酸和硝酸的体积比例为1:3至1:50。通过将氢氟酸、硝酸和醋酸的体积比例设置在上述范围,从而保证hna溶液能够显著提高对所述牺牲层160和所述抗刻蚀层150的刻蚀选择比,甚至对所述抗刻蚀层150的刻蚀速率接近停止。

118.作为一种示例,所述湿法刻蚀工艺采用的hna溶液中,氢氟酸、硝酸和醋酸之间的体积比例为1:3:8。

119.作为一种示例,所述湿法刻蚀工艺所采用的氢氟酸、硝酸和醋酸的混合溶液中,硝酸和氢氟酸之间的分子比率至少为2,硝酸的摩尔百分比至少为14%。

120.作为一种示例,所述湿法刻蚀工艺所采用的氢氟酸、硝酸和醋酸的混合溶液中,氢氟酸的摩尔百分比为0.2%至6%,硝酸的摩尔百分比为14%至28%,醋酸的摩尔百分比为66%至86%。

121.通过将硝酸和氢氟酸之间的分子比率、以及氢氟酸、硝酸和醋酸的摩尔百分比设置在上述范围,有利于使得hna溶液对牺牲层160和抗刻蚀层150的刻蚀选择比的提高效果更显著,甚至对抗刻蚀层150的刻蚀速率接近停止,同时,还有利于使得所述湿法刻蚀工艺对牺牲层160的刻蚀速率较慢,从而使得所述湿法刻蚀工艺的刻蚀速率可控、提高所述湿法刻蚀工艺的工艺控制性,进一步降低去除所述牺牲层160的工艺难度。

122.参考图21和图22,图21为俯视图,图22为图21沿yy割线的剖面图,以所述抗刻蚀层150和侧墙190为掩膜,刻蚀所述第一凹槽210和第二凹槽220底部的所述目标层100,形成目标图形300。

123.由前述记载可知,所述第一凹槽210和所述第二凹槽220的图形精度以及图形质量较高,且所述抗刻蚀层150用于作为刻蚀目标层100的掩膜作用能够得到保障,相应有利于提高图形化所述目标层100的工艺效果,进而提高了目标图形300的图形精度和图形质量。

124.本实施例中,所述目标层100为介电层,因此,以所述抗刻蚀层150和侧墙190为掩膜,刻蚀所述第一凹槽210和第二凹槽220底部的所述介电层,形成互连槽。相应地,本实施例中,所述目标图形300为互连槽。

125.所述互连槽用于为形成金属线提供空间位置。

126.本实施例中,所述目标层100上还形成有硬掩膜材料层110和刻蚀停止层120,第一凹槽210和第二凹槽220的底部暴露出刻蚀停止层120。

127.因此,以所述抗刻蚀层150和侧墙190为掩膜,依次刻蚀第一凹槽210和第二凹槽220底部的刻蚀停止层120和硬掩膜材料层110,剩余的硬掩膜材料层110作为硬掩膜层230;以所述硬掩膜层230为掩膜,图形化所述目标层100。

128.通过先将第一凹槽210和第二凹槽220的图形传递到硬掩膜材料层110中形成硬掩膜层230,有利于提高图形化目标层100的工艺稳定性和工艺效果。

129.本实施例中,采用干法刻蚀工艺(例如:各向异性干法刻蚀工艺),依次刻蚀所述第一凹槽210和第二凹槽220底部的刻蚀停止层120、硬掩膜材料层110和目标层100。干法刻蚀工艺具有各向异性刻蚀的特性,刻蚀剖面控制性较好,有利于提高图形传递的精度,进而使得在所述目标层100中形成的目标图形300满足工艺要求,且干法刻蚀工艺还有利于实现较大的刻蚀选择比,从而提高图形化所述目标层100的工艺效果。

130.本实施例中,在图形化所述目标层100的过程中,所述抗刻蚀层150和所述侧墙190也被消耗部分厚度。

131.结合参考图23和图24,图23为俯视图,图24为图23沿yy割线的剖面图,本实施例中,所述半导体结构的形成方法还包括:在形成所述互连槽之后,在所述互连槽中形成金属线310。

132.金属线310用于实现半导体结构与外部电路或其他互连结构的电连接。

133.由前述记载可知,所述互连槽的图形精度和图形质量高,且相邻的所述互连槽之间的间距易于满足设计最小间隔,相应有利于使所述金属线310在纵向上的间距满足设计最小间隔,同时,所述互连槽在头对头的位置处也能够实现较小的距离,还有利于提高金属线310的图形精度和设计自由度,进而有利于提高金属线310的电连接性能。

134.本实施例中,所述金属线310的材料为铜。其他实施例中,所述线的材料还能够为钴、钨、铝等导电材料。

135.本实施例中,在形成所述金属线310的过程中,还去除剩余的所述抗刻蚀层150、侧墙190、刻蚀停止层120以及硬掩膜层230,从而暴露出所述介电层的顶面,为后续工艺做准备。

136.虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。