1.本公开涉及半导体存储器件和用于制造该半导体存储器件的方法,并且更具体地,涉及用于半导体存储器件的组件的支撑图案。

背景技术:

2.半导体存储器件由于诸如小型化、多功能性和低制造成本的特点而在电子行业会越来越有价值。然而,随着电子行业不断发展,更高集成度的半导体存储器件变得更加重要。

3.对于更高集成度的半导体存储器件,半导体存储器件的图案的线宽可以逐渐减小。然而,由于图案的微型化可能需要诸如更高成本的曝光技术等的新的曝光技术,更高集成度的半导体存储器件已经变得越来越困难。因此,已经对新的集成技术进行了研究。例如,在dram存储器件中,正在研究将字线掩埋在半导体衬底内部的结构。

技术实现要素:

4.本公开的各方面提供了高度集成的半导体存储器件。

5.然而,本公开的各方面不限于在此阐述的方面。通过参考下面给出的本公开的详细描述,本公开的以上和其他方面对于本公开所属领域的普通技术人员将变得更加明显。

6.根据本公开的一方面,提供了一种半导体存储器件,其包括:衬底;第一下电极组,所述第一下电极组位于所述衬底上并且包括多个第一下电极;第二下电极组,所述第二下电极组位于所述衬底上并且包括多个第二下电极;第一支撑图案,所述第一支撑图案位于每个所述第一下电极的侧壁上并且连接每个所述第一下电极;以及第二支撑图案,所述第二支撑图案位于每个所述第二下电极的侧壁上并且连接每个所述第二下电极。所述多个第一下电极包括以第一六边形形状布置的第一边缘下电极和设置在所述第一六边形形状的中心处的第一中心下电极。所述多个第二下电极包括以第二六边形形状布置的第二边缘下电极和设置在所述第二六边形形状的中心处的第二中心下电极。所述第一中心下电极在彼此不同的第一方向、第二方向和第三方向上与每个所述第一边缘下电极间隔开。所述第一支撑图案紧邻所述第二支撑图案。所述第一中心下电极在与所述第一方向、所述第二方向和所述第三方向不同的第四方向上与所述第二中心下电极间隔开。

7.根据本公开的另一方面,提供了一种半导体存储器件,其包括:衬底,所述衬底包括单元区域,所述单元区域包括第一区域和沿着所述第一区域的边界的第二区域;多个支撑图案,所述多个支撑图案位于所述单元区域的所述第一区域上并且彼此间隔开;虚设支撑图案,所述虚设支撑图案沿着所述单元区域的所述第二区域延伸;多个下电极,所述多个下电极位于所述单元区域的所述第一区域上,其中,所述下电极的各个子集由相应的所述支撑图案连接;以及多个虚设下电极,所述多个虚设下电极位于所述衬底的所述单元区域的所述第二区域上并且由所述虚设支撑图案连接,其中,所述支撑图案以蜂窝结构布置。

8.根据本公开的另一方面,提供了一种半导体存储器件,其包括:衬底;多个下电极,

所述多个下电极位于所述衬底上;以及多个支撑图案,所述多个支撑图案连接到所述下电极。所述多个下电极布置成在第一方向上延伸的第一下电极线和第二下电极线。所述第一下电极线和所述第二下电极线在与所述第一方向不同的第二方向上彼此相邻,其中,所述第二下电极线的一个所述下电极相对于所述第一下电极线的一个所述下电极在所述第二方向上偏移。所述多个支撑图案布置成在与所述第一方向和所述第二方向不同的第三方向上延伸的第一支撑图案线。

附图说明

9.通过参照附图详细描述本公开的示例性实施例,本公开的以上以及其他方面和特征将变得更加容易理解,在附图中:

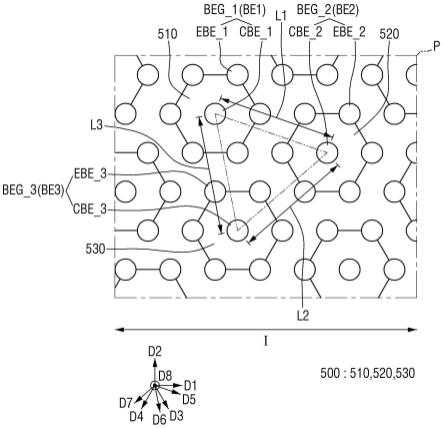

10.图1是示出了根据本公开的一些实施例的半导体存储器件的俯视图。

11.图2是图1的区域p的放大图。

12.图3a和图3b是沿着图1的a1-a1'截取的截面图。

13.图4a和图4b是沿着图1的a2-a2'截取的截面图。

14.图5是图1的区域q的放大图。

15.图6a和图6b是沿着图1的b-b'截取的截面图。

16.图7是图1的区域r的放大图。

17.图8是沿着图1的c-c'截取的截面图。

18.图9、图10、图11、图12、图13、图14、图15、图16和图17是示出了根据一些实施例的用于制造半导体存储器件的方法的中间阶段图。

具体实施方式

19.在下文中,将参照图1至图8描述根据本公开的一些实施例的半导体存储器件。附图不一定以固定比例示出,并且在一些实施例中,在附图中示出的结构中的至少一些结构的比例可能被夸大以清楚地示出实施例的特征。

20.在根据本公开的一些实施例的半导体器件的附图中,虽然dram(动态随机存取存储器)被示出为示例半导体存储器件,但是本公开的实施例不限于此,并且可以应用于其他半导体存储器件。

21.图1是用于说明根据本公开的一些实施例的半导体存储器件的俯视图。图2是图1的区域p的放大图。图3a和图3b是沿着图1的a1-a1'截取的截面图。图4a和图4b是沿着图1的a2-a2'截取的截面图。

22.参照图1至图4b,提供了衬底100。衬底100可以包括单元区域。单元区域可以包括第二区域ii和位于第二区域ii的边界内的第一区域i。即,第二区域ii可以围绕第一区域i的边界布设(place)或可以沿着第一区域i的边界延伸。术语第一、第二等在本文中可以仅用于将一个元件或区域与另一元件或区域区分开。

23.在一些实施例中,半导体存储器件可以包括沿着单元区域的第二区域ii延伸的虚设支撑图案500d。多个支撑图案500布设或布置在单元区域的第一区域i上或内并且彼此间隔开。第二区域ii可以围绕第一区域i。

24.从平面视角看(即,在俯视图中),支撑图案500可以以蜂窝结构布置。即,支撑图案

500可以均具有六边形形状。为了便于说明,尽管从平面视角看,支撑图案500被示出为具有正六边形形状,但是实施例不限于此。支撑图案500的侧壁也可以具有圆形或圆角形式。这样,如本文使用的术语“六边形形状”可以包括大体上六边形形状,其包括可能由例如制造中的偏差或公差导致的不对称。蜂窝结构包括由相应的支撑图案500限定的六边形形状的布置。

25.支撑图案500和虚设支撑图案500d均可以包括例如以下至少一种:氮化硅(sin)、碳氮化硅(sicn)、硼氮化硅(sibn)、碳氧化硅(sioc)、氮氧化硅(sion)、碳氮氧化硅(siocn)或它们的组合。然而,本公开的技术思想不限于此。

26.尽管未示出,但是外围电路区域或核心区域可以位于单元区域的外部。单元区域的第一区域i可以是其中布置有可运行或功能性存储单元的区域。

27.单元区域的第二区域ii可以是与单元区域的第一区域i相同或类似但是其中布置有虚设存储单元(其是非功能性的或实际上不可运行以存储数据)的区域。

28.出于防止图案的形状在光刻工艺中在单元存储区域的外围上未形成为期望的形状和/或形状由于光的干涉、衍射等而扭曲的问题,可以形成布设在单元区域的第二区域ii中的虚设存储单元。另外,由于在蚀刻工艺中单元区域的外围处的蚀刻条件变得不同于中心部分的蚀刻条件,因此可能出现图案之间的桥接(bridge)。因此,可以形成虚设存储单元,使得单元区域的外围区域处的蚀刻条件与中心部分的蚀刻条件相同或更相似。

29.衬底100可以是体硅或soi(绝缘体上硅)。或者,衬底100可以是硅衬底,或可以包括其他材料,诸如但不限于例如硅锗、sgoi(绝缘体上硅锗)、锑化铟、铅碲化合物、砷化铟、磷化铟、砷化镓或锑化镓。在下面的描述中,将通过示例的方式将衬底100解释为硅衬底。

30.尽管未示出,但是单元区域的衬底100可以包括有源区。元件隔离或分隔膜(例如,图8的110)可以布设在衬底100中,以限定有源区。随着半导体存储器件的设计规则减少,有源区可以以对角地延伸的条的形式形成。

31.在俯视图中,下电极be和虚设下电极dbe可以以z字形图案布置在衬底100的单元区域上。下电极be可以布设在单元区域的第一区域i上。虚设下电极dbe可以布设在单元区域的第二区域ii上。虚设下电极dbe可以布设在单元区域的第一区域i和第二区域ii上。即,至少一部分虚设下电极dbe可以布设在单元区域的第二区域ii上。

32.支撑图案500可以布设在下电极be的侧壁上,并且可以沿着下电极be的侧壁延伸。支撑图案500可以连接每个下电极be或下电极be的组/子集,从而为下电极be提供结构支撑。虚设支撑图案500d可以布设在虚设下电极dbe的侧壁上,并且可以沿着虚设下电极dbe的侧壁延伸。虚设支撑图案500d可以连接每个虚设下电极dbe或虚设下电极dbe的组/子集,从而为虚设下电极dbe提供结构支撑。如本文在描述支撑图案时使用的,术语“连接”可以指由支撑图案提供的物理或结构连接。

33.下电极be和虚设下电极dbe可以包括但不限于例如掺杂的半导体材料、导电金属氮化物(例如,氮化钛、氮化钽或氮化钨等)、金属(例如,钌、铱、钛或钽等)或导电金属氧化物(例如,氧化铱等)。

34.参照图2,根据一些实施例的半导体存储器件可以包括布设在衬底100上的第一下电极组beg_1和第二下电极组beg_2。

35.第一下电极组beg_1可以包括多个第一下电极be1。第二下电极组beg_2可以包括

多个第二下电极be2。第一下电极组beg_1和第二下电极组beg_2可以彼此间隔开。

36.支撑图案500可以包括连接第一下电极be1的第一支撑图案510和连接第二下电极be2的第二支撑图案520。第一支撑图案510和第二支撑图案520可以以蜂窝结构布置。即,从平面视角看(即,在俯视图中),第一支撑图案510和第二支撑图案520可以具有六边形形状。第一支撑图案510和第二支撑图案520可以是彼此最靠近的一对支撑图案500。

37.表述彼此“最靠近”可以指第一支撑图案510和第二支撑图案520二者彼此紧邻而它们之间无中间的支撑图案500。即,当第一支撑图案510和第二支撑图案520被称为彼此最靠近时,另一支撑图案500不布设或布置在第一支撑图案510和第二支撑图案520之间。

38.第一下电极be1可以包括第一中心下电极cbe_1,第一中心下电极cbe_1设置或布设在由布设在六角形的顶点处的多个第一边缘下电极ebe_1限定的六角形或六边形形状的中心处。第一中心下电极cbe_1可以与每个第一边缘下电极ebe_1间隔开。第一中心下电极cbe_1与每个第一边缘下电极ebe_1之间的距离可以是相同的。

39.类似地,第二下电极be2可以包括第二中心下电极cbe_2,第二中心下电极cbe_2设置或布设在由布设在六角形的顶点处的多个第二边缘下电极ebe_2限定的六角形或六边形形状的中心处。第二中心下电极cbe_2可以与每个第二边缘下电极ebe_2间隔开。第二中心下电极cbe_2与每个第二边缘下电极ebe_2之间的距离可以是相同的。

40.六个第一边缘下电极ebe_1和六个第二边缘下电极ebe_2可以分别设置在第一中心下电极cbe_1和第二中心下电极cbe_2周围。然而,本公开的技术思想不限于此。

41.第一边缘下电极ebe_1可以在第一方向d1、第三方向d3和第四方向d4上与第一中心下电极cbe_1间隔开。具体地,六个第一边缘下电极ebe_1当中的两个第一边缘下电极ebe_1可以在第一方向d1上与第一中心下电极cbe_1间隔开。两个其他第一边缘下电极ebe_1可以在第三方向d3上与第一中心下电极cbe_1间隔开。其余两个第一边缘下电极ebe_1可以在第四方向d4上与第一中心下电极cbe_1间隔开。

42.第二边缘下电极ebe_2可以在第一方向d1、第三方向d3和第四方向d4上与第二中心下电极cbe_2间隔开。六个第二边缘下电极ebe_2当中的两个第二边缘下电极ebe_2可以在第一方向d1上与第二中心下电极cbe_2间隔开。两个其他第二边缘下电极ebe_2可以在第三方向d3上与第二中心下电极cbe_2间隔开。其余两个第二边缘下电极ebe_2可以在第四方向d4上与第二中心下电极cbe_2间隔开。

43.第一中心下电极cbe_1可以在第五方向d5上与第二中心下电极cbe_2间隔开。第五方向d5不同于第一方向d1、第三方向d3和第四方向d4。第五方向d5可以是第一方向d1与第三方向d3之间的任意方向。即,第一中心下电极cbe_1和第一边缘下电极ebe_1彼此间隔开的方向d1、d3、d4不同于第一中心下电极cbe_1和第二中心下电极cbe_2彼此间隔开的方向d5。

44.在一些实施例中,本公开的半导体存储器件还可以包括布设在衬底100上的第三下电极组beg_3。第三下电极组beg_3可以最靠近第一下电极组beg_1和第二下电极组beg_2二者。即,第一至第三下电极组beg_1、beg_2和beg_3均可以彼此最靠近。

45.第三下电极组beg_3可以包括多个第三下电极be3。多个第三下电极be3可以包括第三中心下电极cbe_3和与第三中心下电极cbe_3间隔开的第三边缘下电极ebe_3。

46.支撑图案500可以包括连接相应的第三下电极be3的第三支撑图案530。第三支撑

图案530可以以蜂窝结构布置。即,从平面视角看(即,在俯视图中),第三支撑图案530可以具有六边形形状。

47.第三边缘下电极ebe_3可以布置为限定六角形或六边形形状,例如,布设在六角形的相应顶点处。第三中心下电极cbe_3可以设置或布设在由第三边缘下电极ebe_3限定的六角形的中心处。可以提供六个第三边缘下电极ebe_3。然而,本公开的技术思想不限于此。

48.第三边缘下电极ebe_3可以在第一方向d1、第三方向d3和第四方向d4上与第三中心下电极cbe_3间隔开。六个第三边缘下电极ebe_3当中的两个第三边缘下电极ebe_3可以在第一方向d1上与第三中心下电极cbe_3间隔开。两个其他第三边缘下电极ebe_3可以在第三方向d3上与第三中心下电极cbe_3间隔开。其余两个第三边缘下电极ebe_3可以在第四方向d4上与第三中心下电极cbe_3间隔开。

49.第三中心下电极cbe_3可以与第一中心下电极cbe_1和第二中心下电极cbe_2间隔开。第一至第三中心下电极cbe_1、cbe_2和cbe_3之间的距离中的每一者可以是基本上相同的。第一中心下电极cbe_1与第二中心下电极cbe_2之间的距离l1、第二中心下电极cbe_2与第三中心下电极cbe_3之间的距离l2和第三中心下电极cbe_3与第一中心下电极cbe_1之间的距离l3均可以是相同的。

50.第一中心下电极cbe_1可以在第六方向d6上与第三中心下电极cbe_3间隔开。第六方向d6不同于第一方向d1、第三方向d3、第四方向d4和第五方向d5。例如,第六方向d6可以是第三方向d3与第四方向d4之间的任意方向。

51.第二中心下电极cbe_2可以在第七方向d7上与第三中心下电极cbe_3间隔开。第七方向d7不同于第一方向d1、第三方向d3、第四方向d4、第五方向d5和第六方向d6。例如,第七方向d7可以是不同于第二方向d2和第四方向d4的任意方向和/或可以是第二方向d2与第四方向d4之间的任意方向。

52.第三中心下电极cbe_3和第一中心下电极cbe_1彼此间隔开的方向d6不同于第三中心下电极cbe_3和第三边缘下电极ebe_3彼此间隔开的方向d1、d3、d4。第三中心下电极cbe_3和第二中心下电极cbe_2彼此间隔开的方向d7不同于第三中心下电极ceb_3和第三边缘下电极ebe_3彼此间隔开的方向d1、d3、d4。第一至第三中心下电极cbe_1、cbe_2和cbe_3彼此间隔开的方向可以均不同。

53.在一些实施例中,第一至第三中心下电极cbe_1、cbe_2和cbe_3可以均对应于等边三角形的顶点。因此,第五方向d5与第六方向d6之间的角度可以为60

°

。类似地,第六方向d6与第七方向d7之间的角度可以为60

°

。然而,本公开的技术思想不限于此。

54.参照图3a至图4b,连接到有源区的定位焊盘(landing pad)200可以布设在衬底100上。将定位焊盘200电隔离的层间绝缘膜105可以布设在衬底100上。

55.定位焊盘200可以包括导电材料。例如,尽管定位焊盘200可以包括钨(w),但是本公开的技术思想不限于此。

56.层间绝缘膜105包括绝缘材料,并且可以将多个定位焊盘200彼此电隔离。例如,尽管层间绝缘膜105可以包括氧化硅,但是本公开的技术思想不限于此。

57.蚀刻停止膜300可以布设在层间绝缘膜105上。蚀刻停止膜300可以为例如氮化硅膜。下电极be可以穿透蚀刻停止膜300并且连接到定位焊盘200。

58.第一下电极be1可以包括第一中心下电极cbe_1以及在第一方向d1上与第一中心

下电极cbe_1间隔开的两个第一边缘下电极ebe_1。

59.第一支撑图案510可以布设在第一下电极be1的侧壁be1_ss上。第一支撑图案510可以在结构上或机械地支撑第一中心下电极cbe_1和第一边缘下电极ebe_1。

60.第一支撑图案510可以包括在第八方向d8上与衬底100间隔开的第一上支撑图案511和布设在第一上支撑图案511与衬底100之间的第一下支撑图案513。第八方向d8可以为例如衬底100的厚度方向。然而,本公开的技术思想不限于此。例如,第一支撑图案510可以是单个图案,或者第一支撑图案510也可以由三个或更多个图案形成。

61.第二下电极be2可以包括在第一方向d1上彼此间隔开的多个第二边缘下电极ebe_2。第二下电极be2可以包括在第四方向d4上彼此间隔开的多个第二边缘下电极ebe_2。

62.第二支撑图案520可以布设在第二下电极be2的侧壁be2_ss上。第二支撑图案520可以在结构上或机械地支撑第二边缘下电极ebe_2。

63.第二支撑图案520可以包括在第八方向d8上与衬底100间隔开的第二上支撑图案521和布设在第二上支撑图案521与衬底100之间的第二下支撑图案523。然而,本公开的技术思想不限于此。例如,第二支撑图案520可以是单个图案,或者第二支撑图案520也可以由三个或更多个图案形成。

64.第三下电极be3可以包括第三中心下电极cbe_3和在第四方向d4上与第三中心下电极cbe_3间隔开的两个第三边缘下电极ebe_3。

65.第三支撑图案530可以布设在第三下电极be3的侧壁be3_ss上。第三支撑图案530可以包括在第八方向d8上与衬底100间隔开的第三上支撑图案531和布设在第三上支撑图案531与衬底100之间的第三下支撑图案533。然而,本公开的技术思想不限于此。例如,第三支撑图案530可以是单个图案,或者第三支撑图案530也可以由三个或更多个图案形成。

66.第一至第三上支撑图案511、521和531的上表面511_us、521_us和531_us可以分别与第一至第三下电极be1、be2和be3的上表面be1_us、be2_us和be3_us基本上共面或布设在相同的平面上。然而,本公开的技术思想不限于此。

67.电容性电介质膜400可以布设在第一至第三下电极be1、be2和be3上。电容性电介质膜400可以布设在第一至第三支撑图案510、520和530上。

68.电容性电介质膜400可以沿着第一下电极be1的侧壁be1_ss、蚀刻停止膜300的上表面和第一下支撑图案513的下表面形成。电容性电介质膜400可以沿着第一下电极be1的侧壁be1_ss、第一下支撑图案513的上表面和第一上支撑图案511的下表面形成。

69.电容性电介质膜400可以沿着第二下电极be2的侧壁be2_ss、蚀刻停止膜300的上表面和第二下支撑图案523的下表面形成。电容性电介质膜400可以沿着第二下电极be2的侧壁be2_ss、第二下支撑图案523的上表面和第二上支撑图案521的下表面形成。

70.电容性电介质膜400可以沿着第三下电极be3的侧壁be3_ss、蚀刻停止膜300的上表面和第三下支撑图案533的下表面形成。电容性电介质膜400可以沿着第三下电极be3的侧壁be3_ss、第三下支撑图案533的上表面和第三上支撑图案531的下表面形成。

71.上电极600可以布设在电容性电介质膜400上,从而上电极600、下电极be和位于它们之间的电容性电介质膜400限定用于存储器件的电容器。

72.电容性电介质膜400可以包括但不限于例如以下至少一种:氧化硅、氮化硅、氮氧化硅、氧化铪、氧化铪硅、氧化镧、氧化镧铝、氧化锆、氧化锆硅、氧化钽、氧化钛、氧化钡锶

钛、氧化钡钛、氧化锶钛、氧化钇、氧化铝、氧化铅钪钽、铌酸铅锌或它们的组合。

73.上电极600可以包括但不限于例如以下至少一种:掺杂的半导体材料、金属、导电金属氮化物或金属硅化物。

74.第一至第三下电极be1、be2和be3可以具有圆柱形,如图3a和图4a所示。另外,第一至第三下电极be1、be2和be3可以具有柱形,如图3b和图4b所示。

75.图5是图1的区域q的放大图。图6a和图6b是沿着图1的b-b'截取的截面图。为了便于说明,将主要描述与在图1至图4b中描述的点或特征不同的点或特征。

76.参照图5至图6b,根据一些实施例的半导体存储器件的单元区域可以包括第一区域i和第二区域ii。

77.单元区域的第一区域i可以是其中布设并运行有功能性存储单元的区域。单元区域的第二区域ii可以是具有与单元区域的第一区域i相同或类似的结构但是其中布设有非功能性的或实际上不运行的虚设存储单元的区域。

78.下电极be可以布设在单元区域的第一区域i上。支撑图案500可以布设在衬底100上。支撑图案500布设在下电极be的侧壁be_ss上,并且可以连接每个下电极be。

79.支撑图案500可以包括在第八方向d8上与衬底100间隔开的上支撑图案501和布设在上支撑图案501与衬底100之间的下支撑图案503。然而,本公开的技术思想不限于此。例如,支撑图案500可以是单个图案,或者支撑图案500也可以由三个或更多个图案形成。

80.支撑图案500可以以蜂窝结构布置。从平面视角看(即,在俯视图中),支撑图案500可以具有六边形形状。下电极be可以包括布设或设置在六角形的中心处的中心下电极cbe。下电极be可以包括布设或外围地布置在六角形的顶点处并且与中心下电极cbe间隔开的边缘下电极ebe。

81.多个虚设下电极dbe可以布设在单元区域的第二区域ii上。布设在虚设下电极dbe的侧壁dbe_ss上并且连接相应的虚设下电极dbe的虚设支撑图案500d可以布设在衬底100上。虚设支撑图案500d可以沿着单元区域的第二区域ii延伸。

82.虚设支撑图案500d可以包括在第八方向d8上与衬底100间隔开的上虚设支撑图案501d和布设在上虚设支撑图案501d与衬底100之间的下虚设支撑图案503d。然而,本公开的技术思想不限于此。例如,虚设支撑图案500d可以是单个图案,或者虚设支撑图案500d也可以由三个或更多个图案形成。

83.虚设下电极dbe可以布设在单元区域的第一区域i和第二区域ii之间的边界处。即,虚设下电极dbe的至少一部分可以在第八方向d8上与单元区域的第二区域ii交叠。

84.下电极be可以在第八方向d8上与单元区域的第一区域i交叠。下电极be可以在第八方向d8上与单元区域的第二区域ii不交叠。

85.下电极be和虚设下电极dbe可以具有圆柱形或柱形。然而,本公开的技术思想不限于此。

86.下电极be的上表面be_us、上支撑图案501的上表面501_us、虚设下电极dbe的上表面dbe_us和上虚设支撑图案501d_us的上表面可以基本上共面或布设在相同的平面上。然而,本公开的技术思想不限于此。

87.图7是图1的区域r的放大图。

88.参照图7,多个下电极be和多个支撑图案500可以布设在衬底100上。支撑图案500

可以连接一组下电极be中的每一者。

89.在一些实施例中,下电极be可以布置成在第一方向d1上延伸的第一下电极线bel_1和第二下电极线bel_2。即,下电极be的子集可以沿着方向d1对准,以限定下电极线bel_1、bel_2。第一下电极线bel_1和第二下电极线bel_2可以彼此不相交。第一下电极线bel_1和第二下电极线bel_2可以延伸成彼此平行。

90.第一下电极线bel_1和第二下电极线bel_2可以在第二方向d2上彼此相邻。第一下电极线bel_1和第二下电极线bel_2可以在第二方向d2上彼此间隔开。

91.包括在第一下电极线bel_1中的下电极be可以相对于包括在第二下电极线bel_2中的下电极be在第二方向d2上偏移(offset)。包括在第一下电极线bel_1中的下电极的各自中心和包括在第二下电极线bel_2中的下电极的各自中心可以在第二方向d2上不交叠。即,多个下电极be可以以z字形图案布置。

92.支撑图案500可以具有六边形形状。下电极be可以包括布设在六角形的顶点处的边缘下电极ebe和设置在六角形的中心处(例如,布设在六角形的中心处)的中心下电极cbe。即,六个边缘下电极ebe可以围绕中心下电极cbe设置。然而,本公开的技术思想不限于此。

93.支撑图案500可以布置成在第五方向d5上延伸的第一支撑图案线500l_1和第二支撑图案线500l_2。第五方向d5可以是多个中心下电极cbe彼此间隔开的方向之一。

94.第一支撑图案线500l_1和第二支撑图案线500l_2可以在第四方向d4上彼此间隔开。第四方向d4可以是中心下电极cbe和边缘下电极ebe彼此间隔开的方向之一。

95.第四方向d4和第五方向d5可以彼此相交。因此,第一支撑图案线500l_1和第二支撑图案线500l_2可以彼此不相交。第一支撑图案线500l_1和第二支撑图案线500l_2可以彼此平行。

96.包括在第一支撑图案线500l_1中的支撑图案500的各自中心和包括在第二支撑图案线500l_2中的支撑图案500的各自中心可以在第四方向d4上彼此偏移。包括在第一支撑图案线500l_1中的支撑图案500的各自中心和包括在第二支撑图案线500l_2中的支撑图案500的各自中心可以在第四方向d4上不交叠。即,支撑图案500可以以z字形图案布置。

97.图8是沿着图1的c-c'截取的截面图。为了便于说明,将主要描述与在图1至图7中描述的点或特征不同的点或特征。

98.参照图1和图8,本公开的半导体存储器件可以包括元件隔离或分隔膜110、栅极结构130、掩埋接触bc、层间绝缘膜105和定位焊盘200。

99.元件分隔膜110可以形成在衬底100中。元件分隔膜110可以包括具有优异的元件分隔特性的sti(浅沟槽隔离)结构。

100.在一些实施例中,栅极结构130可以被掩埋在衬底100中。栅极结构130可以包括栅极绝缘膜131、栅电极132和栅极覆盖图案133。栅电极132可以为字线。尽管未示出,但是字线可以被掩埋在衬底100中并且在第一方向d1上延伸。字线可以在第二方向d2上彼此间隔开。

101.由于栅极绝缘膜131和栅极覆盖图案133,栅极结构130可以与衬底100绝缘。杂质注入区可以在字线的相对侧形成在衬底100中或布设在衬底100上,以形成源极/漏极区。每条字线可以电连接到字线的一侧的相应杂质注入区。

102.栅极绝缘膜131可以包括氧化硅、氮化硅、氮氧化硅或具有比氧化硅高的介电常数的高介电常数材料。高介电常数材料可以包括例如以下至少一种:氧化铪、氧化铪硅、氧化铪铝、氧化镧、氧化镧铝、氧化锆、氧化锆硅、氧化钽、氧化钛、氧化钡锶钛、氧化钡钛、氧化锶钛、氧化钇、氧化铝、氧化铅钪钽、铌酸铅锌或它们的组合。

103.栅电极132可以包括例如以下至少一种:氮化钛(tac)、碳化钽(tac)、氮化钽(tan)、氮化钛硅(tisin)、氮化钽硅(tasin)、氮化钽钛(tatin)、氮化钛铝(tialn)、氮化钽铝(taaln)、氮化钨(wn)、钌(ru)、钛铝(tial)、碳氮化钛铝(tialc-n)、碳化钛铝(tialc)、碳化钛(tic)、碳氮化钽(tacn)、钨(w)、铝(al)、铜(cu)、钴(co)、钛(ti)、钽(ta)、镍(ni)、铂(pt)、镍铂(ni-pt)、铌(nb)、氮化铌(nbn)、碳化铌(nbc)、钼(mo)、氮化钼(mon)、碳化钼(moc)、碳化钨(wc)、铑(rh)、钯(pd)、铱(ir)、锇(os)、银(ag)、金(au)、锌(zn)、钒(v)或它们的组合。

104.栅极覆盖图案133可以包括例如以下至少一种:多晶硅、氮化硅(sin)、氮氧化硅(sion)、氧化硅(sio2)、碳氮化硅(sicn)、碳氮氧化硅(siocn)和它们的组合。

105.连接到有源区的掩埋接触bc可以形成在衬底100上。定位焊盘200可以连接到掩埋接触bc。掩埋接触bc可以包括导电材料。这使得掩埋接触bc电连接到有源区。尽管掩埋接触bc可以包括例如多晶硅,但是本公开的技术思想不限于此。

106.定位焊盘200可以布设在掩埋接触bc的上表面上。定位焊盘200可以与掩埋接触bc接触。类似于掩埋接触bc,定位焊盘200可以形成彼此间隔开的多个电隔离区域。

107.层间绝缘膜105可以包括第一层间绝缘膜105_1和第二层间绝缘膜105_2。

108.第一层间绝缘膜105_1可以形成在衬底100和元件分隔膜110上。第一层间绝缘膜105_1可以形成为与形成在衬底100和元件分隔膜110中的栅极结构130交叠。

109.尽管第一层间绝缘膜105_1可以包括例如以下至少一种:氧化硅、氮化硅、氮氧化硅或它们的组合,但是本公开的技术思想不限于此。第一层间绝缘膜105_1可以将掩埋接触bc分开。

110.第二层间绝缘膜105_2可以限定形成了多个电隔离区域的定位焊盘200的区域。即,第二层间绝缘膜105_2可以将多个定位焊盘200彼此分开。

111.第二层间绝缘膜105_2包括绝缘材料,并且可以将多个定位焊盘200彼此电隔离。例如,尽管第二层间绝缘膜105_2可以包括氧化硅,但是本公开的技术思想不限于此。

112.连接到定位焊盘200的下电极be可以布设在定位焊盘200和层间绝缘膜105上。支撑图案500可以布设在每个下电极be的侧壁上。支撑图案500可以机械地或在结构上支撑每个下电极be(或下电极be的组)。

113.支撑图案500可以包括在第八方向d8上与衬底100间隔开的上支撑图案501和位于上支撑图案501与衬底100之间的下支撑图案503。

114.电容性电介质膜400可以沿着下电极be和上支撑图案501的轮廓共形地形成。上电极600可以形成在电容性电介质膜400上,以形成一个或更多个电容器结构。

115.图9至图17是根据一些实施例的用于制造半导体存储器件的方法的中间阶段图。将参照在图1至图8中示出的实施例中的一些实施例来描述根据一些实施例的用于制造半导体存储器件的方法。

116.参照图9,可以在衬底100上形成定位焊盘200和层间绝缘膜105。层间绝缘膜105可

以使多个定位焊盘200电绝缘。

117.尽管未示出,但是多条字线可以掩埋在衬底100中。限定多个有源区的元件分隔膜(例如,图8的110)可以形成在衬底100中。可以在衬底100上形成连接到有源区的掩埋接触(例如,图8的bc)。定位焊盘200可以连接到掩埋接触。

118.可以在定位焊盘200和层间绝缘膜105上形成预蚀刻停止膜300p。接下来,可以顺序地形成第一模制层ml1、预下支撑图案503p、第二模制层ml2和预上支撑图案501p。第一模制层ml1和第二模制层ml2可以是氧化硅膜。

119.预下支撑图案503p和预上支撑图案501p可以包括例如以下至少一种:氮化硅(sin)、碳氮化硅(sicn)、硼氮化硅(sibn)、碳氧化硅(sioc)、氮氧化硅(sion)或碳氮氧化硅(siocn)。然而,本公开的技术思想不限于此。

120.尽管附图示出了形成两个预支撑图案501p和503p,但是本公开的技术思想不限于此,并且当然可以仅形成一个预支撑图案。在这种情况下,根据一些实施例的半导体存储器件的支撑图案(例如,图6a的500)可以是单个图案。另外,可以形成三个或更多个预支撑图案。在这种情况下,根据一些实施例的半导体存储器件的支撑图案可以包括三个或更多个支撑图案。

121.参照图10,可以在预上支撑图案501p上形成第一掩模图案mp1。可以形成暴露预上支撑图案501p的第一掩模孔mh1。

122.第一掩模图案mp1可以为例如光刻胶膜。第一掩模图案mp1可以在垂直方向(例如,d8)上与层间绝缘膜105交叠。

123.参照图11,可以蚀刻预上支撑图案501p、第二模制层ml2、预下支撑图案503p、第一模制层ml1和预蚀刻停止膜300p,以形成多个沟槽tr。

124.沟槽tr可以形成为与第一掩模孔mh1的宽度相同。沟槽tr可以暴露定位焊盘200。可以通过蚀刻工艺形成上支撑图案501、下支撑图案503和蚀刻停止膜300。

125.参照图12,可以形成填充沟槽tr的下电极be。可以去除第一掩模图案mp1。

126.下电极be可以连接到定位焊盘200。下电极be的上表面be_us可以与上支撑图案501的上表面501_us基本上共面或布设在相同的平面上。这里,术语“相同”不意味着在物理上完全相同,而是还可以包括工艺余量。

127.图13是用于说明第二掩模图案mp2的俯视图。

128.参照图13,从平面视角看(即,在俯视图中),第二掩模图案mp2可以具有圆形(例如,环形)形状。然而,本公开的技术思想不限于此,并且第二掩模图案mp2可以具有椭圆形形状或六边形形状。

129.第二掩模图案mp2可以为光刻胶膜。第二掩模图案mp2可以限定在图1至图7中示出的支撑图案500的形状。

130.下电极be可以中心地设置或布设在相应的第二掩模图案mp2的中心处。此外,下电极be可以沿着第二掩模图案mp2的外圆周外围地设置或布设。布设在第二掩模图案mp2的中心处的下电极be可以为中心下电极(例如,图5的cbe)。布设在第二掩模图案mp2的外圆周上的下电极be可以为边缘下电极(例如,图5的ebe)。

131.尽管未示出,但是从平面视角看,第二掩模图案mp2可以具有矩形形状。可以在上支撑图案501和下电极be上形成掩模层。还可以通过以两条不同的线蚀刻掩模层来形成第

二掩模图案mp2。两条不同的线之间的交点可以是第二掩模孔(例如,图14的mh2)。

132.图14至图17是沿着图13的d-d'截取的截面图。

133.参照图14,可以在下电极be和上支撑图案501上形成第二掩模图案mp2。

134.可以形成暴露下电极be的一部分和上支撑图案501的一部分的第二掩模孔mh2。第二掩模孔mh2可以是第二掩模图案mp2之间的孔。

135.参照图15,可以去除与第二掩模孔mh2交叠的支撑图案500。

136.此外,可以去除第一模制层ml1和第二模制层ml2。由下电极be的侧壁、下支撑图案503的下表面和蚀刻停止膜300的上表面限定的空间可以为空的空间。由上支撑图案501的下表面、下支撑图案503的上表面和下电极be的侧壁限定的空间可以为空的空间。

137.空的空间可以是在稍后将描述的工艺中形成电容性电介质膜(例如,图16的400)和上电极(例如,图17的600)的空间。

138.参照图16,可以沿着下电极be、蚀刻停止膜300和上支撑图案501之间的边界形成电容性电介质膜400。

139.电容性电介质膜400可以沿着下电极be的侧壁、蚀刻停止膜300的上表面和下支撑图案503的下表面形成。电容性电介质膜400可以沿着下电极be的侧壁、下支撑图案503的上表面和上支撑图案501的下表面形成。

140.参照图17,可以在电容性电介质膜400上形成上电极600。

141.下电极be、电容性电介质膜400和上电极600可以形成根据本公开的一些实施例的半导体存储器件的电容器。

142.尽管附图仅示出了下电极be具有圆柱形形状,但是本公开的技术思想不限于此,并且下电极be可以包括柱形或其他形状。

143.在总结详细描述时,本领域技术人员将理解的是,在基本上不背离本公开的原理的情况下,可以对实施例进行许多变化和修改。因此,本公开的所公开的实施例仅用于一般性和描述性的意义,而不是出于限制的目的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。