技术特征:

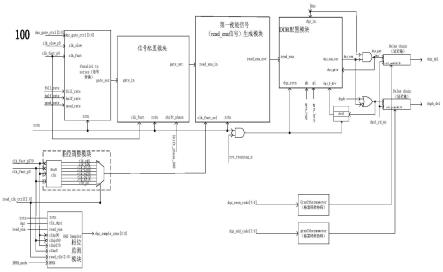

1.一种可编程电路,其特征在于,包括:信号转换模块,用于将外部电路输入的并行信号转换为串行信号,并输出至信号配置模块;信号配置模块,用于接收所述信号转换模块输出的串行信号,和所述外部电路输入的第二时钟时钟频率信号,将所述信号转换模块输出的串行信号的相位偏移0度或者360度,并输出所述相位偏移后的串行信号至第一使能信号生成模块;第一使能信号生成模块,用于接收所述相位偏移后的串行信号,生成第一使能信号,并输出至ddr配置模块和相位监测模块;ddr配置模块,用于接收所述第一使能信号和所述外部电路输入的dqs信号,生成第二使能信号;并用于根据所述外部电路输入的第一门控信号、所述外部电路输入第二门控信号和所述外部电路输入至相位监测模块的ddr_mode信号,设置所述可编程电路的ddr模式;相位监测模块,用于监测所述dqs信号的相位,并输出监测结果至所述外部电路;相位调整模块,用于根据所述外部电路输入的监测结果调整所述第一使能信号生成模块生成的第一使能信号的相位。2.如权利要求1所述的可编程电路,其特征在于,所述可编程电路还包括第一与门、第二与门、或门和二分频器;所述第一与门的第一输入端接收所述外部电路输入的全局复位信号,并分别与所述信号转换模块、所述信号配置模块、所述第一使能信号生成模块、所述相位监测模块和所述相位调整模块的复位端和连接,所述第一与门的第二输入端接收所述外部电路输入的局部复位信号,所述第一与门的输出端与所述ddr配置模块和所述二分频器的的复位端连接;所述第二与门的第一输入端接收所述外部电路输入的dqs信号,所述第二与门的第二输入端接收所述ddr配置模块输出的第二使能信号,所述第二与门的输出端输出所述dqs信号和所述第二使能信号的逻辑与信号至所述ddr配置模块,所述逻辑与信号为dqs_gating信号;所述或门的第一输入端接收所述外部电路输入的dqs相位方向信号,所述或门的第二输入端接收所述ddr配置模块输出的第二使能信号,所述或门的第二输入端为低电平触发,所述或门的输出端输出逻辑或信号至所述二分频器;所述二分频器的输入端接收所述或门的输出端输出的逻辑或信号,所述二分频器的输出端输出dqs相位方向信号的二分频信号至所述ddr配置模块。3.如权利要求2所述的可编程电路,其特征在于,所述可编程电路还包括:格雷码转热码模块,用于将所述外部电路输入的格雷码转换为热码,并输出至延迟链模块;延迟链模块,包括第一延迟链区域和第二延迟链区域,所述第一延迟链区域用于接收所述第二与门输出的dqs_gating信号和延迟链使能信号;所述第二延迟链区域用于接收所述或门输出的逻辑或信号和所述延迟链使能信号;所述延迟链模块用于使dqs信号与dq信号产生45度的相位偏移。4.如权利要求1所述的可编程电路,其特征在于,所述并行信号为四比特的dqs_gate_ctrl信号;所述信号转换模块还包括:第一速率模式,所述第一速率模式下,所述信号转换模块的第一时钟clk_slow的时钟

频率与第二时钟clk_fast的时钟频率相同,且所述串行信号为只使用一比特的dqs_gate_ctrl信号;第二速率模式,所述第二速率模式下,所述信号转换模块的第一时钟clk_slow的时钟频率与第二时钟clk_fast的时钟频率的比值为1:2,且所述串行信号为使用二比特的dqs_gate_ctrl信号;第三速率模式,所述第三速率模式下,所述信号转换模块的第一时钟clk_slow的时钟频率与第二时钟clk_fast的时钟频率的比值为1:4,且所述串行信号为使用四比特的dqs_gate_ctrl信号;所述第一时钟的时钟频率、所述第二时钟的时钟频率从所述外部电路输入。5.如权利要求1所述的可编程电路,其特征在于,所述ddr配置模块,用于根据所述外部电路输入的第一门控信号、所述外部电路输入第二门控信号和所述外部电路输入至相位监测模块的ddr_mode信号,设置所述可编程电路的ddr模式;包括:设置ddr3模式,所述ddr3模式下,所述第一门控信号为0、所述第二门控信号为0、所述ddr4_mode信号为0;设置ddr4 1tck模式,所述ddr4 1tck模式下,所述第一门控信号为0、所述第二门控信号为1、所述ddr4_mode信号为0;设置ddr4 2tck模式,所述所述ddr4 2tck模式下,所述第一门控信号为1、所述第二门控信号为1;所述ddr4_mode信号经所述外部电路输入至所述相位监测模块。6.如权利要求2所述的可编程电路,其特征在于,所述相位监测模块,用于监测所述外部电路输入的dqs信号的相位;包括:接收所述外部电路输入的四个时钟频率信号,所述四个时钟频率信号的相位分别为0度、90度、180度、270度;接收所述第一使能信号生成模块输出的第一使能信号,根据所述外部电路输入的dqs信号和所述第一使能信号生成模块输出的第一使能信号监测所述外部电路输入的dqs信号的相位相对所述dqs_gating信号的位置;所述dqs信号的相位相对所述dqs_gating信号向左偏移,所述dqs相位监测模块输出端输出0111或1111;所述dqs信号的相位相对所述dqs_gating信号向右偏移,所述dqs相位监测模块输出端输出0000或0001;所述dqs信号的相位相对所述dqs_gating信号未偏移,所述dqs相位监测模块输出端输出0011。7.如权利要求6所述的可编程电路,其特征在于,所述相位监测模块,输出监测结果至所述外部电路;包括:所述dqs相位监测模块接收所述外部电路输入的read_clk_ctrl[2:0]信号;所述外部电路接收所述相位监测模块输出端的输出值;所述外部电路根据所述相位监测模块输出端的输出值调整所述read_clk_ctrl[2:0]信号;所述相位监测模块输出端输出0111或1111,所述read_clk_ctrl[2:0]信号的值增大;所述dqs相位监测模块输出端输出0001或0000,所述read_clk_ctrl[2:0]信号的值减小。

8.如权利要求7所述的可编程电路,其特征在于,所述相位调整模块,用于根据所述外部电路输入的监测结果调整所述第一使能信号生成模块生成的第一使能信号的相位;包括:接收所述外部电路输入的read_clk_ctrl[2:0]信号;接收所述外部电路输入的时钟频率信号并经所述相位调整模块的四时钟转八时钟区域增加所述时钟频率信号的相位数,所述外部电路输入的时钟频率信号的相位分别为0度、90度、180度、270度,所述经所述相位调整模块的四时钟转八时钟区域后的所述时钟频率信号相位分别为0度、45度、90度、135度、180度、225度、270度和315度;根据所述read_clk_ctrl[2:0]信号的值使所述第一使能信号生成模块生成的第一使能信号的相位增加45度或者减少45度,所述read_clk_ctrl[2:0]信号的值增大,所述dqs_gating信号的相位增加45度,所述read_clk_ctrl[2:0]信号的值减小,所述dqs_gating信号的相位减小45度。9.一种集成电路,其特征在于,包括上述权利要求1~8任一项所述的可编程电路。10.一种电子设备,其特征在于,包括设备主体以及设于所述设备主体内的如权利要求9所述的集成电路。

技术总结

本申请公开了一种可编程电路、集成电路及电子设备,属于集成电路技术领域。所述可编程电路包括信号转换模块,将外部电路输入的并行信号转换为串行信号;信号配置模块,将信号转换模块输出的串行信号的相位偏移0度或360度;第一使能信号生成模块,生成第一使能信号;DDR配置模块,生成第二使能信号;设置可编程电路的DDR模式;相位监测模块,监测外部电路输入的DQS信号的相位,输出监测结果;相位调整模块,根据外部电路输入的监测结果调整第一使能信号生成模块生成的第一使能信号的相位。实现了实时监测DQS信号的偏移状态并实时修正,扩大了DQS gate的单位时间间隔,避免了DQS采样DQ数据发生错误,并经过DDR配置模块实现了DDR3、DDR4 1tCK和DDR4 2tCK的3种模式的设置。2tCK的3种模式的设置。2tCK的3种模式的设置。

技术研发人员:刘可勇 林协群 王祯元

受保护的技术使用者:深圳市紫光同创电子有限公司

技术研发日:2022.03.01

技术公布日:2022/6/16

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。