1.本发明涉及集成电路技术领域,尤其涉及一种可编程电路、集成电路及电子设备。

背景技术:

2.ddr(double data rate,双倍速率同步动态随机存储器)存储器内,ddr3/4(第三代和第四代ddr)在读写切换时dqs信号会高阻态,因此需要通过ddr phy(端口物理层)产生一个dqs_gate(dqs窗口)来避免dqs信号的高阻态,防止ddr3/4读数据时出现误码。

3.ddr phy(端口物理层)用一个可调延迟的内部信号rxena(使能信号)去采样读返回的dqs信号,返回一个比特信号样本,通过dqs gate training算法调整rxena的延迟,再判断连续的样本值来确定读返回dqs信号的第一个上升沿的位置,再结合读burst(突发)长度来确定dqs_gate的宽度,ddr phy(端口物理层)通过这种反馈调节机制可以获得dqs的有效窗口,并且电路在获得有效dqs_gate后,ddrphy(端口物理层)需要实时监控由于vt的变化导致dqs抖动或者clk抖动,dqs gate training出来的gate位置可能已经不是在最佳位置,所以需要ddr phy(端口物理层)具有动态调整dqs gate的能力。

4.然而根据当前技术方案得到的dqs_gate都只有半个ui(1ui对应半个时钟周期的时间间隔),因此当dqs信号偏移大于0.5个ui时,该方案将无法正确去除dqs的高阻态,导致dqs采样dq数据发生错误,并且该方案还无法设定系统的ddr模式,缺少dqs信号偏移的实时监测与修正功能。

5.如图1是根据现有的方法针对ddr4的mem颗粒的ui效果图,从图中可以看出a处或b处的位置dqs_gate都只有半个ui,导致了在温变和电压波动时很容易由于dqs的抖动导致需要电路频繁调整dqs gate位置,这个过程中会浪费系统带宽甚至导致系统出现不可恢复的误码,并且ddr4颗粒可以设定1个或者2个周期,但是现有的电路只能支持其中的一种模式。

技术实现要素:

6.本发明的目的在于提供一种可编程电路、集成电路及电子设备,以解决现有电路在解决dqs信号偏移时dqs_gate只有半个ui,无法实时监测到dqs信号偏移并实时修正,进一步解决了电路的ddr模式单一的技术问题。

7.本发明的技术方案如下:

8.提供一种可编程电路,包括:

9.信号转换模块,用于将外部电路输入的并行信号转换为串行信号,并输出至信号配置模块;

10.信号配置模块,用于接收所述信号转换模块输出的串行信号,和所述外部电路输入的第二时钟时钟频率信号,将所述信号转换模块输出的串行信号的相位偏移0度或者360度,并输出所述相位偏移后的串行信号至第一使能信号生成模块;

11.第一使能信号生成模块,用于接收所述相位偏移后的串行信号,生成第一使能信

号,并输出至ddr配置模块和相位监测模块和;

12.ddr配置模块,用于接收所述第一使能信号和所述外部电路输入的dqs信号,生成第二使能信号;并用于根据所述外部电路输入的第一门控信号、所述外部电路输入第二门控信号和所述外部电路输入至相位监测模块的ddr_mode信号,设置所述可编程电路的ddr模式;

13.相位监测模块,用于监测所述dqs信号的相位,并输出监测结果至所述外部电路;

14.相位调整模块,用于根据所述外部电路输入的监测结果调整所述第一使能信号生成模块生成的第一使能信号的相位。

15.在一些实施例中,所述可编程电路还包括第一与门、第二与门、或门和二分频器;

16.所述第一与门的第一输入端接收所述外部电路输入的全局复位信号,并分别与所述信号转换模块、所述信号配置模块、所述第一使能信号生成模块、所述相位监测模块和所述相位调整模块的复位端和连接,所述第一与门的第二输入端接收所述外部电路输入的局部复位信号,所述第一与门的输出端与所述ddr配置模块和所述二分频器的的复位端连接;

17.所述第二与门的第一输入端接收所述外部电路输入的dqs信号,所述第二与门的第二输入端接收所述ddr配置模块输出的第二使能信号,所述第二与门的输出端输出所述dqs信号和所述第二使能信号的逻辑与信号至所述ddr配置模块,所述逻辑与信号为dqs_gating信号;

18.所述或门的第一输入端接收所述外部电路输入的dqs相位方向信号,所述或门的第二输入端接收所述ddr配置模块输出的第二使能信号,所述或门的第二输入端为低电平触发,所述或门的输出端输出逻辑或信号至所述二分频器;

19.所述二分频器的输入端接收所述或门的输出端输出的逻辑或信号,所述二分频器的输出端输出dqs相位方向信号的二分频信号至所述ddr配置模块。

20.在一些实施例中,所述可编程电路还包括:

21.格雷码转热码模块,用于将所述外部电路输入的格雷码转换为热码,并输出至延迟链模块;

22.延迟链模块,包括第一延迟链区域和第二延迟链区域,所述第一延迟链区域用于接收所述第二与门输出的dqs_gating信号和延迟链使能信号;所述第二延迟链区域用于接收所述或门输出的逻辑或信号和所述延迟链使能信号;所述延迟链模块用于使dqs信号与dq信号产生45度的相位偏移。

23.在一些实施例中,所述并行信号为四比特的dqs_gate_ctrl信号;所述信号转换模块还包括:

24.第一速率模式,所述第一速率模式下,所述信号转换模块的第一时钟clk_slow的时钟频率与第二时钟clk_fast的时钟频率相同,且所述串行信号为只使用一比特的dqs_gate_ctrl信号;

25.第二速率模式,所述第二速率模式下,所述信号转换模块的第一时钟clk_slow的时钟频率与第二时钟clk_fast的时钟频率的比值为1:2,且所述串行信号为使用二比特的dqs_gate_ctrl信号;

26.第三速率模式,所述第三速率模式下,所述信号转换模块的第一时钟clk_slow的时钟频率与第二时钟clk_fast的时钟频率的比值为1:4,且所述串行信号为使用四比特的

dqs_gate_ctrl信号;

27.所述第一时钟的时钟频率、所述第二时钟的时钟频率从所述外部电路输入。

28.在一些实施例中,所述ddr配置模块,用于根据所述外部电路输入的第一门控信号、所述外部电路输入第二门控信号和所述外部电路输入至相位监测模块的ddr_mode信号,设置所述可编程电路的ddr模式;包括:

29.设置ddr3模式,所述ddr3模式下,所述第一门控信号为0、所述第二门控信号为0、所述ddr4_mode信号为0;

30.设置ddr4 1tck模式,所述ddr4 1tck模式下,所述第一门控信号为0、所述第二门控信号为1、所述ddr4_mode信号为0;

31.设置ddr4 2tck模式,所述所述ddr4 2tck模式下,所述第一门控信号为1、所述第二门控信号为1;

32.所述ddr4_mode信号经所述外部电路输入至所述相位监测模块。

33.在一些实施例中,所述相位监测模块,用于监测所述外部电路输入的dqs信号的相位;包括:

34.接收所述外部电路输入的四个时钟频率信号,所述四个时钟频率信号的相位分别为0度、90度、180度、270度;

35.接收所述第一使能信号生成模块输出的第一使能信号,根据所述外部电路输入的dqs信号和所述第一使能信号生成模块输出的第一使能信号监测所述外部电路输入的dqs信号的相位相对所述dqs_gating信号的位置;

36.所述dqs信号的相位相对所述dqs_gating信号向左偏移,所述dqs相位监测模块输出端输出0111或1111;

37.所述dqs信号的相位相对所述dqs_gating信号向右偏移,所述dqs相位监测模块输出端输出0000或0001;

38.所述dqs信号的相位相对所述dqs_gating信号未偏移,所述dqs相位监测模块输出端输出0011。

39.在一些实施例中,所述相位监测模块,输出监测结果至所述外部电路;包括:

40.所述dqs相位监测模块接收所述外部电路输入的read_clk_ctrl[2:0]信号;

[0041]

所述外部电路接收所述相位监测模块输出端的输出值;

[0042]

所述外部电路根据所述相位监测模块输出端的输出值调整所述read_clk_ctrl[2:0]信号;所述相位监测模块输出端输出0111或1111,所述read_clk_ctrl[2:0]信号的值增大;所述dqs相位监测模块输出端输出0001或0000,所述read_clk_ctrl[2:0]信号的值减小。

[0043]

在一些实施例中,所述相位调整模块,用于根据所述外部电路输入的监测结果调整所述第一使能信号生成模块生成的第一使能信号的相位;包括:

[0044]

接收所述外部电路输入的read_clk_ctrl[2:0]信号;

[0045]

接收所述外部电路输入的时钟频率信号并经所述相位调整模块的四时钟转八时钟区域增加所述时钟频率信号的相位数,所述外部电路输入的时钟频率信号的相位分别为0度、90度、180度、270度,所述经所述相位调整模块的四时钟转八时钟区域后的所述时钟频率信号相位分别为0度、45度、90度、135度、180度、225度、270度和315度;

[0046]

根据所述read_clk_ctrl[2:0]信号的值使所述第一使能信号生成模块生成的第一使能信号的相位增加45度或者减少45度,所述read_clk_ctrl[2:0]信号的值增大,所述dqs_gating信号的相位增加45度,所述read_clk_ctrl[2:0]信号的值减小,所述dqs_gating信号的相位减小45度。

[0047]

本发明的另一技术方案如下:

[0048]

提供一种集成电路,包括上述任一项的可编程电路。

[0049]

本发明的另一技术方案如下:

[0050]

提供一种电子设备,包括设备主体以及设于设备主体内的如上述的集成电路。

[0051]

本发明的有益效果:

[0052]

本发明提供的可编程电路、集成电路及电子设备,通过上述的技术方案,

[0053]

扩大了dqs gate的ui,实时监测了dqs信号的偏移状态进行实时修正,避免了dqs采样导致的dq数据发生错误,并通过ddr配置模块实现了ddr3、ddr4 1tck和ddr4 2tck的3中ddr模式的配置。

附图说明

[0054]

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

[0055]

图1为本技术背景技术的针对ddr4的mem颗粒的ui效果图;

[0056]

图2为本技术实施例的电路连接图;

[0057]

图3为本技术实施例ddr3模式的效果图

[0058]

图4为本技术实施例ddr4 1tck模式的效果图

[0059]

图5为本技术实施例ddr4 2tck模式的效果图

[0060]

图6为本技术实施例提供的一种集成电路结构示意图;

[0061]

图7为本技术实施例提供的电子设备结构示意图。

具体实施方式

[0062]

下面结合本技术实施例中的附图,对本发明实施例中的技术方案进行清楚、完整的描述。应当明确,所描述的实施例仅仅是本发明一部分实施例,而不是全部实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0063]

需要说明的是,在实施例的描述中,使用的“模块”“第一”“第二”等的前缀词和后缀词是为了有利于本技术的说明,其本身没有特定的意义;并且本实施例中所描述的“连接”指电学连接,可以是直接连接关系,也可以是间接连结关系。

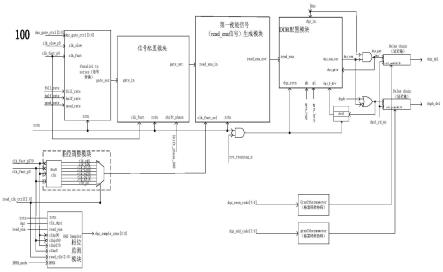

[0064]

图2是本技术实施例的电路连接图,如图2所示,本技术实施例的可编程电路100包括信号转换模块(parallel to series)、信号配置模块、第一使能信号生成模块、ddr配置模块、相位监测模块、相位调整模块、格雷码转热码模块、延迟链模块,还包括了连接各模块复位端的第一与门,以及与ddr配置模块和延迟链模块分别连接的第二与门和或门。具体

地:

[0065]

本技术实施例的信号转换模块(parallel to series)将从外部电路输入的并行信号转换为串行信号,并经信号转换模块的gate_ser端口输出至与信号转换模块连接的信号配置模块,dqs_gate_ctrl[3:0]信号是四比特的dqs_gating信号控制码,本技术实施例的外部电路即指与本技术可编程电路相接的外部控制电路,不在本技术实施例中做详细解释;

[0066]

作为本实施例的一种实施方式,外部电路选择信号转换模块的速率模式,在对应的速率模式下,外部电路输入至信号转换模块的时钟频率和dqs_gate_ctrl[3:0]信号有不同的状态,其中,信号转换模块的速率模式包括:

[0067]

第一速率模式full_rate模式(全速率)时,信号转换模块的第一时钟clk_slow的时钟频率与第二时钟clk_fast的时钟频率相同,此时信号转换模块的串行信号为只使用一比特的dqs_gate_ctrl[0]信号;

[0068]

第二速率模式half_rate模式(半速率)时,信号转换模块的第一时钟clk_slow的时钟频率与第二时钟clk_fast的时钟频率的比值为1:2,此时信号转换模块的串行信号为使用二比特的dqs_gate_ctrl[2:0]信号;

[0069]

第三速率模式quad_rate模式(四分之一速率)时,信号转换模块的第一时钟clk_slow的时钟频率与第二时钟clk_fast的时钟频率的比值为1:4,此时信号转换模块的串行信号为使用四比特的dqs_gate_ctrl[3:0]信号。

[0070]

本技术实施例的信号配置模块,用于接收信号转换模块输出的串行信号,和外部电路输入的第二时钟时钟频率信号,将信号转换模块输入的串行信号的相位偏移0度或者360度,其中,如触发shift_phase_360信号,信号转换模块输入的串行信号的相位偏移360度,如果没有触发该信号,则相位不偏移;随后输出相位偏移后的串行信号至第一使能信号(read_ena信号)生成模块;

[0071]

本技术实施例的第一使能信号(read_ena信号)生成模块,用于接收相位偏移后的串行信号,,输出至相位监测模块和ddr配置模块;

[0072]

其中,第一使能信号(read_ena信号)生成模块还接收相位调整模块的输出信号,根据该信号调整生成的第一使能信号(read_ena信号)的相位,且每次调整的相位不超过45度。

[0073]

本技术实施例的ddr配置模块,用于接收第一使能信号(read_ena信号)生成模块输入的第一使能信号read_ena信号,生成第二使能信号dqs_ena信号;并用于根据外部电路输入的第一门控信号gate_high信号、外部电路输入第二门控信号gate_latch信号和外部电路输入至相位监测模块的ddr_mode信号,设置可编程电路的ddr模式,其中,ddr模式包括ddr3模式、ddr4 1tck模式、ddr4 2tck模式;

[0074]

具体地,如图3的ddr3模式的效果图所示,ddr3模式时,ddr配置模块的第一门控信号gate_high信号为0、第二门控信号gate_latch信号为0、dqs相位监测模块的ddr4_mode信号为0,此时电路中dqs信号最大左右偏移1个ui,也能正确去除dqs的高阻态,极大地增加了ddr3系统的鲁棒性;

[0075]

如图4的ddr4 1tck模式的效果图,ddr4 1tck模式,ddr4 1tck模式下,ddr配置模块的第一门控信号gate_high信号为0、第二门控信号gate_latch信号为1、dqs相位监测模

块的ddr4_mode信号为0,此时电路中dqs信号最大左右偏移1个ui,也能正确去除dqs的高阻态,降低了ddr4系统1tck模式的出错率;

[0076]

如图5的ddr4 2tck模式的效果图所示,ddr4 2tck模式,ddr42tck模式下,ddr配置模块的第一门控信号gate_high信号为1、第二门控信号gate_latch信号为1,此时电路中dqs信号最大左右偏移2个ui,也能正确去除dqs的高阻态,降低了ddr4系统2tck模式的出错率。

[0077]

本技术实施例的相位监测模块,监测从外部电路输入的dqs信号的相位,并输出dqs_sample_sync[3:0]信号,dqs相位监测模块还接收外部电路输入的四个时钟频率信号,其中,四个时钟频率信号的相位分别为0度、90度、180度、270度,接收第一使能信号(read_ena信号)生成模块输出的第一使能信号read_ena信号,根据外部电路输入的dqs信号和第一使能信号(read_ena信号)生成模块输出的第一使能信号read_ena信号监测外部电路输入的dqs信号的相位相对dqs_gating信号的位置,其中,第一使能信号read_ena信号经ddr配置模块生成dqs_ena信号,dqs_ena信号和dqs信号逻辑与生成dqs_gating信号,因此根据read ena信号和dqs信号即可确定dqs信号的相位相对dqs_gating信号的位置;

[0078]

具体地,当dqs信号的相位相对dqs_gating信号向左偏移,相位监测模块输出端dqs_sample_sync[3:0]信号输出0111或1111;

[0079]

当dqs信号的相位相对dqs_gating信号向右偏移,相位监测模块输出端dqs_sample_sync[3:0]信号输出0000或0001;

[0080]

当dqs信号的相位相对dqs_gating信号未偏移,相位监测模块输出端dqs_sample_sync[3:0]信号输出0011;

[0081]

本技术实施例的相位监测模块还接收外部电路输入的read_clk_ctrl[2:0]信号;外部电路接收dqs相位监测模块输出端的输出值,根据dqs相位监测模块输出端的输出值调整read_clk_ctrl[2:0]信号;其中,dqs相位监测模块输出端输出0111或1111,read_clk_ctrl[2:0]信号的值增大;dqs相位监测模块输出端输出0001或0000,read_clk_ctrl[2:0]信号的值减小;

[0082]

作为本实施例的一种实施方式,相位监测模块还包括了外部电路输入ddr4_mode信号,与本技术ddr配置模块共同配置本技术的ddr模式。

[0083]

本技术实施例的相位调整模块,用于根据外部电路输入的监测结果read_clk_ctrl[2:0]信号的值调整第一使能信号read_ena信号的相位。

[0084]

本技术实施例的相位调整模块接收外部电路输入的read_clk_ctrl[2:0]信号,并接收外部电路输入的时钟频率信号,经dqs_gating相位修正模块的“4to8clk”模块(四时钟转八时钟区域)增加时钟频率信号的相位数,外部电路输入的时钟频率信号的相位分别为0度、90度、180度、270度,经dqs_gating相位修正模块的四时钟转八时钟区域后的时钟频率信号相位分别为0度、45度、90度、135度、180度、225度、270度和315度;

[0085]

随后根据read_clk_ctrl[2:0]信号的值使第一使能信号read_ena信号的相位增加45度或者减少45度,read_clk_ctrl[2:0]信号的值增大,dqs_gating信号的相位增加45度,read_clk_ctrl[2:0]信号的值减小,dqs_gating信号的相位减小45度。

[0086]

本技术实施例的格雷码转热码模块,将外部电路输入的格雷码转换为热码,并输出至延迟链模块;

[0087]

本技术实施例的延迟链模块,包括第一延迟链区域和第二延迟链区域,第一延迟链区域用于接收第二与门输出的dqs_gating信号和延迟链使能信号,生成dqs延迟信号(dqs del);所述第二延迟链区域用于接收或门输出的逻辑或信号和延迟链使能信号,生成dqs相位方向延迟信号(dqsb del信号);延迟链模块用于使dqs信号与dq信号产生45度的相位偏移。

[0088]

本技术实施例第一与门的第一输入端接收外部电路输入的全局复位信号,并分别与信号转换模块、信号配置模块、第一使能信号(read_ena信号)生成模块、相位监测模块和相位调整模块的复位端和连接,第一与门的第二输入端接收外部电路输入的局部复位信号,第一与门的输出端与ddr配置模块和二分频器的的复位端连接;

[0089]

本技术实施例第二与门的第一输入端接收外部电路输入的dqs信号,第二与门的第二输入端接收ddr配置模块输出的第二使能信号dqs_ena信号,第二与门的输出端输出逻辑与信号,即dqs_gating信号分别至延迟链模块和ddr配置模块;

[0090]

本技术实施例或门的第一输入端接收外部电路输入的dqs相位方向信号,或门的第二输入端接收ddr配置模块输出的第二使能信号dqs_ena信号,或门的第二输入端为低电平触发,或门的输出端输出逻辑或信号分别至延迟链模块和二分频器;

[0091]

本技术实施例二分频器的输入端接收或门的输出端输出的逻辑或信号,二分频器的输出端输出dqs相位方向信号的二分频信号至ddr配置模块。

[0092]

如图6所示,本技术实施例还提供一种集成电路200,该集成电路200包括上树的可编程电路。

[0093]

如图7所示,本技术实施例还提供一种电子设备300,该电子设备300包括设备主体310以及上述的集成电路200,其中集成电路200设于设备主体300内。

[0094]

以上内容是结合具体的实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限与这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简单推演或替换,都应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。