cmos成像传感器及相关制造方法

交叉引用

1.本技术要求于2021年11月15日提交的、题为“saddle-gate source follower for imaging pixels”美国非临时专利申请号17/127,065的优先权权益,该美国非临时专利申请是2020年12月18日提交的题为“3-dimensional fin-shaped transistor designs and applications in semiconductor image sensors”的美国临时专利申请号63/127,494的非临时申请并要求该美国临时专利申请的优先权权益,上述两个申请在此通过引用整体并入本文。

技术领域

1.本文献涉及互补金属氧化物半导体(cmos)图像传感器。更具体地,实施例涉及用于与cmos图像传感器(cis)像素的像素内电路系统集成的鞍形栅极源极跟随器晶体管块。

背景技术:

2.许多现代电子应用包括基于互补金属氧化物半导体(cmos)图像传感器(cis)技术的集成数码相机和/或其他成像系统。cis通常可以包括像素阵列,其中,每个像素包括单个光电传感器(例如,光电二极管),或一组多个光电传感器。每个像素还可以包括支撑硬件,诸如用于将光电传感器的光学响应转换为相应的电信号以供其他部件使用的源极跟随器晶体管。像素的性能与其尺寸相关。例如,增加像素中光电二极管区域的尺寸可以增加光电二极管的全阱电容(fwc),这往往支持更高的动态范围、更高的对比度和/或其他图像性能改进。类似地,增加源极跟随器晶体管的有源区域可以改进像素的噪声性能,诸如通过增加其信噪比(snr)。

3.对于任何给定的像素尺寸,(多个)光学传感器和源极跟随器晶体管都必须共享占用空间。因此,任何一个尺寸的增加都会迫使另一个尺寸的减小,这样像素设计通常代表图像性能(与尺寸和相应的光学传感器的fwc相关)和噪声性能(与源极跟随器晶体管的有源区域相关)之间的折衷。随着像素尺寸不断减小,在优化fwc的同时保持可接受的噪声性能(即高snr)变得越来越困难。

技术实现要素:

4.实施例提供用于实施用于与互补金属氧化物半导体(cmos)图像传感器(cis)像素集成的鞍形栅极源极跟随器晶体管的电路、装置和方法。例如,cis可以包括大量成像像素(例如,数百万个成像像素)阵列。每个成像像素可以包括一个或多个光电传感器,用于将入射照射转换为积累的光电荷,以及像素内电路系统,用于读出积累的光电荷并将其转换为像素输出信号。每个像素内电路包括读出链中的源极跟随器块,并且本文描述的源极跟随器块的实施例是用鞍形栅极源极跟随器晶体管结构来实施的。鞍形栅极源极跟随器晶体管结构可以包括沟道区,该沟道区具有由沟槽在其轴向侧上限定的三维几何形状。栅极氧化层形成在沟道区的顶部和轴向侧上方,并且鞍形栅极结构形成在栅极氧化层上。因此,鞍形

栅极结构包括在沟道区的顶部上方延伸的座部,以及在沟道区的第一和第二轴向侧上方延伸的第一和第二防护部,使得第一和第二防护部被掩埋在半导体衬底的上表面下面。

5.根据一组实施例,提供了互补金属氧化物半导体(cmos)成像传感器(cis)。cis包括成像像素,具有:半导体衬底;光电传感器块,包括至少一个光电传感器,其被配置为响应于暴露于照射而积累光电荷并将积累的光电荷转移到浮置扩散区以供读出;和像素内电路系统,与所述浮置扩散区耦合以将积累的光电荷转换为像素输出信号。所述像素内电路系统包括:鞍形栅极源极跟随器晶体管块,其具有:具有三维几何形状的沟道区,包括:具有轴向长度尺寸和平面宽度尺寸的上部、由第一侧沟槽限定以具有轴向长度尺寸和第一防护深度尺寸的第一轴向侧部、以及由第二侧沟槽限定以具有轴向长度尺寸和第二防护深度尺寸的第二轴向侧部,所述沟道区被注入有沟道掺杂;栅极氧化层,形成在至少所述沟道区的上部、所述第一轴向侧部和所述第二轴向侧部的上方;和鞍形栅极结构,形成在所述栅极氧化层上以具有在所述沟道区的上部上方延伸的座部、在所述沟道区的第一轴向侧部上方延伸的第一防护部以及在所述沟道区的第二轴向侧部上方延伸的第二防护部,使得所述第一防护部和所述第二防护部掩埋在半导体衬底的上表面下面。

6.一些此类实施例还包括:将电隔离材料填充到第一隔离沟槽中形成的第一侧隔离区,所述第一隔离沟槽沿着至少轴向长度蚀刻至半导体衬底中比所述第一沟槽深度更深的第一隔离沟槽深度;和将电隔离材料填充到第二隔离沟槽中形成的第二侧隔离区,所述第二隔离沟槽沿着至少轴向长度蚀刻至半导体衬底中比所述第二沟槽深度更深的第二隔离沟槽深度,其中,所述第一侧沟槽被蚀刻到所述第一隔离沟槽的电隔离材料中,并且所述第二侧沟槽蚀被刻到所述第二隔离沟槽的电隔离材料中。一些这样的实施例还包括源极区和漏极区,注入到所述半导体衬底中,所述源极区位于所述沟道区的第一轴向端处,而漏极区位于所述沟道区的与所述第一轴向端相对的第二轴向端处并与所述第一轴向端分隔开对应于轴向长度的距离。

7.根据另一组实施例,提供一种用于制造鞍形栅极源极跟随器晶体管块的方法。该方法包括:通过以下来形成所述鞍形栅极源极跟随器晶体管块的沟道区:沿着半导体衬底的轴向长度蚀刻第一侧沟槽至第一沟槽深度;沿着半导体衬底的轴向长度蚀刻第二侧沟槽至第二沟槽深度,所述第二侧沟槽基本上平行于所述第一侧沟槽并且与所述第一侧沟槽分隔开水平距离,使得沟道区的三维几何形状包括根据轴向长度、水平距离、第一沟槽深度和第二沟槽深度限定的上部、第一轴向侧部和第二轴向侧部;和根据沟道区的三维几何形状,将沟道掺杂注入到所述半导体衬底中;在半导体衬底上至少在沟道区的上部、第一轴向侧部和第二轴向侧部上方形成栅极氧化层;和在栅极氧化层上形成鞍形栅极结构,以具有:在沟道区的上部上方延伸以具有对应于水平距离的平面宽度尺寸的座部、在沟道区的第一轴向侧部上方延伸以具有对应于第一沟槽深度的第一防护深度尺寸的第一防护部、以及在沟道区的第二轴向侧部上方延伸以具有对应于第二沟槽深度的第二防护深度尺寸的第二防护部。

8.一些这样的实施例还包括通过以下来形成侧隔离区:沿着至少轴向长度蚀刻第一隔离沟槽至比第一沟槽深度更深的第一隔离沟槽深度;沿着至少轴向长度蚀刻第二隔离沟槽至比第二沟槽深度更深的第二隔离沟槽深度;和利用电隔离材料来填充第一隔离沟槽和第二隔离沟槽;其中,第一侧沟槽蚀刻到第一隔离沟槽的电隔离材料中,且第二侧沟槽蚀刻

到第二隔离沟槽的电隔离材料中。一些这样的实施例还包括将源极区和漏极区注入到所述半导体衬底中,所述源极区位于所述沟道区的第一轴向端处,而漏极区位于所述沟道区的与所述第一轴向端相对的第二轴向端处并与所述第一轴向端分隔开对应于轴向长度的距离。

9.下面的附图、描述和权利要求提供了具有混合结构的晶体管、其实施方式和所公开技术的特征的上述和其他方面的更详细的描述。

附图说明

10.本文引用并构成其一部分的附图示出了本公开的实施例。附图与描述一起用于解释本发明的原理。

11.图1示出了作为本文描述的各种实施例的上下文的说明性数字成像系统的一部分的简化框图。

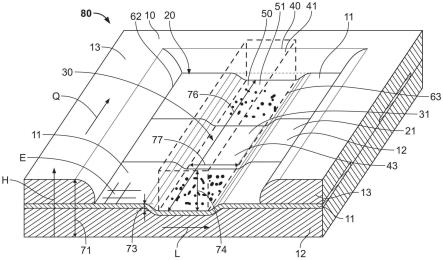

12.图2a和2b分别示出作为传统cis像素设计的典型代表的、被实现为平面源极跟随器晶体管的传统源极跟随器块的侧截面图和透视图。

13.图3a-3d示出了根据本文描述的各种实施例的说明性新颖鞍形栅极源极跟随器晶体管的简化视图。

14.图4示出了根据各种实施例的具有带有2

×

2光电传感器布置的集成鞍形栅极源极跟随器晶体管的说明性cis像素的简化物理布局。

15.图5示出了根据各种实施例的具有带有2

×

4光电传感器布置的集成鞍形栅极源极跟随器晶体管的另一说明性cis像素的简化物理布局。

16.图6示出了根据本文描述的各种实施例的cis像素的简化电路示意图。

17.图7示出了根据各种实施例的用于在集成电路的半导体衬底上制造鞍形栅极源极跟随器晶体管的说明性集成电路部分制造工艺。

18.图8a-8d示出了在沿着图7的制造工艺的各个阶段处的制造中的鞍形栅极源极跟随器晶体管的说明图。

19.在附图中,相似的部件和/或特征可以具有相同的附图标记。此外,相同类型的各种部件可以通过在附图标记后面加上区分相似部件的第二标记来区分。如果说明书中仅使用第一附图标记,则该描述可适用于具有相同第一附图标记的任何一个相似部件,而与第二附图标记无关。

具体实施方式

20.在以下描述中,提供了许多具体细节以彻底理解本发明。然而,本领域技术人员应当理解,可以在没有这些细节中的一个或多个的情况下实现本发明。在其他示例中,出于简洁的目的,将不描述本领域中已知的特征和技术。

21.许多现代电子应用包括基于互补金属氧化物半导体(cmos)图像传感器(cis)技术的集成数码相机和/或其他成像系统。cis通常可以包括像素阵列,每个像素包括单个光电传感器(例如,光电二极管),或一组多个光电传感器。每个成像像素可以包括光敏元件和像素内电路系统,该光敏元件响应于光而生成光电荷,像素内电路系统用于处理所产生的光电荷以产生电像素输出信号并用于控制每个成像像素的操作。cis成像像素的像素内电路

系统通常包括多个金属氧化物半导体场效应晶体管(mosfet),用于执行传感和控制功能。

22.图1示出了作为本文描述的各种实施例的上下文的说明性数字成像系统100的一部分的简化框图。数字成像系统100可以围绕互补金属氧化物半导体(cmos)图像传感器(cis)技术被构建。这种cis系统通常可以包括一个或多个像素105阵列,诸如以行和列布置的大量像素105。每个像素105可以包括光电传感器块110,其可以包括单个光电二极管115(例如,或任何合适的光电传感器,诸如光电门、光电晶体管等),或者一组多个光电二极管115(例如,一组四个光电二极管)。

23.像素105还包括附加部件(像素内电路系统)以促进使用光电传感器块110进行光学感测。如图所示,实施例可以包括增益块120、重置块130、源极跟随器块140和选择块150。每个都可以使用至少一个对应的晶体管来实施。增益块120可以控制像素105的增益,诸如通过实施双转换增益(dcg)。重置块130可以选择性地重置像素105部件。源极跟随器块140(本文使用鞍形栅极源极跟随器装置来实施)可以支持将来自光电传感器块110的输出转换成指示由光电传感器块110检测到的光学信息的电信号。选择块150可以支持从像素105阵列当中选择像素105信号,例如作为行选择操作的一部分。像素105可以与诸如列选择总线等的读出总线160耦合。

24.随着技术的进步,在许多应用上下文中已经存在趋向于减小这种像素105的尺寸的动力。实际上,许多数字成像应用正在寻求在其图像传感器芯片上不断增加像素105的数量和密度(即,驱动105像素尺寸的减小),同时还需要设计继续满足或超过多个性能参数,诸如与图像对比度、动态范围、帧捕获速率、信噪比(snr)、功耗等相关的参数。然而,已经证明像素105的某些性能参数往往通过降低像素105内的部件的尺寸而受到不利影响。例如,减小光电传感器块110中的光电二极管115的尺寸可以减小其全阱电容(fwc),这可能往往导致较低的动态范围、较低的对比度和/或其他图像性能降低。类似地,减小源极跟随器块140的有源区域可以降低像素105的噪声性能,诸如通过降低其信噪比(snr)。例如,减小源极跟随器块140的有源区域往往会增加其对低频噪声(有时称为1/f噪声)和/或突发噪声(也称为随机电报信号(rts)噪声、脉冲噪声、双稳态噪声等)。一些传统像素105设计寻求在像素105的有限占用空间内最大化部件尺寸,但是每个像素105的占用空间由其所有部件共享;增加一个部件(例如,光电传感器块110)的尺寸往往需要减小另一个(例如,源极跟随器块140)的尺寸。因此,传统像素105设计经常被迫在图像性能(与光电传感器的尺寸和相应的fwc相关)和噪声性能(与源极跟随器晶体管的有源区域相关)之间进行折衷。

25.随着像素105尺寸持续减小,甚至在图像性能和噪声性能之间达到可接受的折衷也变得越来越困难。为了增加上下文,图2a和2b分别示出了被实施为平面源极跟随器晶体管200的传统源极跟随器块140的侧截面图和透视图,这是传统cis像素设计的典型代表。如图所示,平面源极跟随器晶体管200包括漏极区210、源极区215和栅极区220,它们都实施在衬底205上。例如,衬底205是p掺杂的硅晶片,漏极区210和源极区215中的每个分别是衬底205的n掺杂区,且栅极区220是在衬底205上沉积构建(例如通过沉积)的多晶硅结构。向栅极区220施加栅极电压可以使得电流沟道形成并且电流在漏极区210和源极区215之间沿箭头225的方向流动。电流沟道的长度(l)在图2a中被示为尺寸230。平面源极跟随器晶体管200的有源区宽度(w)在图2b中被示出为尺寸235。同样如图2b所示,有源区可以使用隔离区240,诸如浅沟槽隔离(sti)区来界定(例如,与相邻装置隔离)。

26.实现cis像素的特定性能水平可以涉及实施源极跟随器块140以在阈值可接受噪声水平内产生至少跨导(g_m)阈值水平。跨导量可以在功能上对应于性能特性,诸如帧速率、功耗和某些类型的噪声。通常,饱和区处的广义源极跟随器晶体管的跨导可以计算为:gm=c

oxvsat

其中w是源极跟随器晶体管的宽度(例如,传统设计中图2b的尺寸235),c_ox是氧化物电容,并且v_sat是饱和电压。可以看出,源极跟随器晶体管的跨导往往与其宽度成正比,使得宽度的减小往往会产生跨导相关性能的相应减小。

27.此外,源极跟随器晶体管栅极(s_vg)处的电压噪声可以计算为:其中m是经验参数,且β是频率相关参数。源极跟随器晶体管栅极处的电压信号往往与栅极电容成比例,由c_ox*w*l描述,其中l是电流沟道长度(例如,传统设计中图2a的尺寸230)。从栅极电压噪声和栅极电压信号可以得出,源极跟随器晶体管的snr在功能上与c_ox3*w2*l2相关。因此,可以看出源极跟随器晶体管的snr往往与其宽度和长度成正比,使得源极跟随器晶体管的尺寸减小往往导致噪声性能相应降低。值得注意的是,在传统设计中,这种噪声性能往往在装置边缘处进一步降低,诸如在隔离区240中。例如,在电流沟道中流动的电流会被陷在sti区中并且会产生额外的噪声。

28.许多现代数字成像应用已经将像素尺寸推动低到大约1.12微米的尺度。即使在如此小的规模下,一些基于平面源极跟随器晶体管200的传统设计也已经在可接受的噪声水平下实现了足够的跨导(gm)以提供高cis性能。然而,随着像素尺寸不断减小,保持跨导(gm)和snr的理想水平变得极其困难、不切实际或者甚至不可能。

29.如上所述,在传统平面源极跟随器晶体管200中,栅极区220设置在衬底205的顶部上。向栅极区220施加栅极电压可使得电流沟道正好形成在漏极区210和源极区215之间的衬底205的表面下方(正好在栅极区220下方)。因此,所形成的电流沟道的长度和宽度与栅极区220的长度和宽度相关;当前沟道的物理布局宽度大约是当前沟道的有效有源宽度。例如,降低栅极区220的长度或宽度将往往降低电流沟道的长度或宽度,从而影响源极跟随器的性能。

30.本文描述的实施例提供了一种使用鞍形栅极源极跟随器晶体管来实施的新颖源极跟随器块140。一般而言,本文描述的鞍形栅极源极跟随器晶体管的实施例包括注入到半导体衬底中的分离的源极区和漏极区,并且沟道区在源极区和漏极区之间的轴向方向上延伸。鞍形栅极结构与衬底以以下这样的方式来集成:鞍形栅极结构包括沉积在沟道区上方的座部,以及掩埋在衬底中(例如,进入先前形成的隔离区中)以包裹在沟道区的轴向侧周围的防护部。栅极氧化层夹在鞍形栅极结构和沟道区之间,使得栅极氧化层也包裹在沟道区的顶部和沟道区的轴向侧周围。将栅极电压施加到在鞍形栅极结构上被图案化的端子产生电场,其使得电流沟道在沟道区中形成。鞍形栅极源极跟随器晶体管的有效沟道宽度(由三维鞍形栅极结构产生)明显大于其二维物理布局宽度。因此,与具有相同物理布局尺寸的传统平面源极跟随器晶体管相比,鞍形栅极源极跟随器晶体管可以提供更好的性能(例如,跨导相关和/或噪声相关性能的增加)。

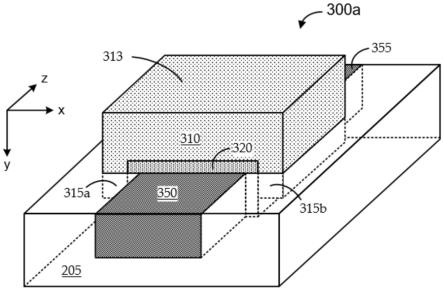

31.图3a-3d示出了根据本文描述的各种实施例的说明性新颖的鞍形栅极源极跟随器

晶体管300的简化视图。鞍形栅极源极跟随器晶体管300可以是图1的源极跟随器块140的实施方案。图3a示出了被示出为切割穿过鞍形栅极源极跟随器晶体管300的栅极区域的简化透视图(标记为300a)。为了更清楚,图3a示出了参考坐标系,其中“z”方向沿着装置的长度(本文称为“轴向”方向)延伸,“x”方向沿着装置的宽度延伸,而“y”方向表示垂直维度(即,垂直于zx平面布局维度)。图3b示出了根据图3a中所示的图示轴规定的对应于在x-y平面中穿过鞍形栅极源极跟随器晶体管300的栅极的宽度方向切割的剖视图(标记为300b)。图3c示出了根据图3a中所示的图示轴规定的对应于在z-y平面中沿着鞍形栅极源极跟随器晶体管300的长度方向切割的剖视图(标记为300c)。图3d示出了根据图3a中所示的图示轴规定的鞍形栅极源极跟随器晶体管300的俯视平面图(标记为300d)。图3a至图3d被一起描述。

32.鞍形栅极源极跟随器晶体管300被示为由诸如硅晶片的一部分的硅衬底205支撑(即,在所述硅衬底上实施、与硅衬底集成等)。源极区350和漏极区355被注入到衬底205中并且被有效地限定装置的有源区的沟道区330分隔开。鞍形栅极结构310被形成以包裹在沟道区330的顶部并沿轴向侧向下,如下文更全面地描述的。源极区350和漏极区355通常实施为在栅极的任一端处注入到衬底205中的掺杂阱,如在图3a、3c和3d中可见的。在一些实施方式中,衬底205是p型衬底,并且源极区350和漏极区355是n掺杂区。在其他实施方式中,衬底205是n型衬底,而源极区350和漏极区355是p掺杂区。

33.如同在其他金属氧化物半导体场效应晶体管(mosfet)装置中一样,在鞍形栅极结构310的栅极端子312处施加电压电势产生了电场,该电场改变了源极区350和漏极区355之间的沟道区330的导电性。例如,将至少阈值电平的电压施加到栅极端子312可以使得耗尽区形成在衬底205的沟道区330中,这允许电流在源极区350和漏极区355之间流动。相反,因为如本文所述的鞍形栅极结构310包裹在沟道区330的顶部上方并沿轴向侧向下,所以在鞍形栅极结构310的栅极端子312处施加电压电势从沟道区330的顶部和轴向侧产生电场,其可以产生与具有明显更宽有源区的平面型源极跟随器晶体管的效果类似的效果(例如,关于噪声性能、跨导和/或其他特性)。

34.如图3a和3b所示,鞍形栅极源极跟随器晶体管300包括形成在沟道区330顶部和轴向侧(即,沿沟道区330的长度延伸的侧部)周围的栅极氧化层320,以及沉积在栅极氧化层320的顶部和轴向侧的周围的鞍形栅极结构310。鞍形栅极结构310可以由金属、导电多晶硅材料和/或任何其他合适的材料制成。特别地,鞍形栅极结构310包括在沟道区330的顶部上方延伸的座部313,以及通过被掩埋在衬底205中(例如,进入下面描述的侧隔离区中)来包裹在沟道区的轴向侧周围的防护部315。图3b示出了鞍形栅极结构310的座部313形成平面(即,水平)宽度尺寸314,其在“x”维度上延伸穿过沟道区330(并且还在“z”维度上在沟道区330上方纵向延伸)。鞍形栅极结构310的防护部315向下(即,通常在“y”维度上)延伸到衬底205中防护深度尺寸316。防护深度尺寸316可以对应于掩埋的防护部315延伸到衬底205(例如,进入到先前在衬底205中形成的蚀刻到隔离区中的沟槽)中的最大深度。在一些实施例中,防护深度尺寸316可以大于或等于平面宽度尺寸314。虽然两个防护深度尺寸316被示为相等,但其他实施例可以利用不同的防护深度尺寸316(即,利用具有不同的相应深度的每个防护部315)来实施。

35.防护深度尺寸316增加了鞍形栅极源极跟随器晶体管300的有效有源区宽度(w)。例如,座部313限定了300纳米(nm)的平面宽度尺寸314(w),并且每个防护部315限定了

150nm的防护宽度尺寸。在该示例中,两个防护部315一起提供额外的300nm的有效宽度,从而将装置有源区的有效宽度加倍至2w。参考上面提供的等式,可以看出,将装置有源区的有效宽度增加两倍可以使装置的snr增加四倍。因此,具有这些尺寸的鞍形栅极源极跟随器晶体管300可以表现出具有相同平面有源区宽度(w)的传统平面型源极跟随器晶体管的大约四倍的snr。

36.栅极氧化层320用作鞍形栅极结构310和沟道区330之间的介电层。特别地,栅极氧化层320的至少一部分夹在鞍形栅极结构310和沟道区330之间以在沟道区330的三个侧面周围形成电介质。在图3a-3d中可以看出,沟道区330具有三维几何形状,其包括:具有轴向长度尺寸318(参见图3c,在“z”方向上延伸的尺寸318)和平面宽度尺寸314的上部;第一轴向侧部(与鞍形栅极结构310的第一防护部315a相邻),其由第一侧沟槽限定以具有轴向长度尺寸;以及第二轴向侧部(与鞍形栅极结构310的第二防护部315b相邻),其由第二侧沟槽限定以具有轴向长度尺寸和第二防护深度尺寸316。因此,至少如图3a和3b所示,栅极氧化层320被形成在沟道区330的至少上部、第一轴向侧部和第二轴向侧部的上面;以及鞍形栅极结构310被形成在栅极氧化层320上以使其座部313在(即,通常覆盖沟道区的上部的区域,并遵循其大体轮廓)沟道区的上部上方延伸,其第一防护部315a在沟道区330的第一轴向侧部上方延伸,并且其第二防护部315b在沟道区的第二轴向侧部上方延伸,使得第一防护部和第二防护部315掩埋在半导体衬底205的下表面下面。

37.一些实施例包括在鞍形栅极结构310的防护部315的外部和/或底部周围的一个或多个隔离区325。隔离区325可以是浅沟槽隔离(sti)。隔离区325可由任何合适的电隔离材料制成,诸如未掺杂的多晶硅或二氧化硅。如下所述,隔离区325可以在形成栅极氧化层320和鞍形栅极结构310之前形成。例如,隔离沟槽被蚀刻到衬底205中并且填充有隔离材料。然后将沟槽蚀刻到隔离材料中,这可以最终至少部分地限定鞍形栅极结构310的防护部315的几何形状。蚀刻到隔离材料中的沟槽还暴露衬底205以形成沟道区330的轴向侧壁。栅极氧化层320可以在沟道区330周围生长,包括在被蚀刻的沟槽所暴露的沟道区330的轴向侧壁上生长。如图所示,隔离区325的实施例可以形成在比用于形成鞍形栅极结构310的防护部15的那些更深的沟槽中。

38.一些实施例包括附加结构。例如,图3b示出了图案化到鞍形栅极结构310的座部313上的栅极触点312和围绕鞍形栅极结构310在衬底205的表面上沉积的间隔件340(例如,氮化物间隔件)。虽然没有明确示出,但实施例可以包括其他结构,诸如附加掺杂区等。例如,一些实施例包括沿着隔离区325和衬底205之间的界面的附加p型注入,诸如以降低暗电流和时间噪声。

39.图3a和3b的视图是高度简化的视图并且仅旨在示出某些特征。例如,虽然各个区和结构被示出为具有方角和/或限定的边缘,但这些区和结构的实际实施方式通常具有有机形状。因此,这些区和结构的边界或边缘实际上没有完全可限定的边界,而是往往以更统计的方式被限定(例如,通过标称值、工艺角等),如本领域技术人员将理解的那样。因此,各种所示的区和结构通常旨在示出结构和区的一般相对布置、结构和区之间的一般隔离等;但并非旨在限定特定的形状、尺寸、边界和/或其他特征。

40.新颖的鞍形栅极源极跟随器晶体管300可用于各种不同类型的集成电路应用中。一些应用使用这样的鞍形栅极源极跟随器晶体管300来实施半导体图像传感器装置(例如

在cis中)中的成像像素105(例如,如图1所示)的像素内电路系统的源极跟随器块140。这样的图像传感器装置可以形成在衬底上以包括由衬底支撑的成像像素105阵列并且可操作以检测入射光以捕获由入射光携带的图像。每个成像像素105可以被构造为包括光敏装置或元件,该光敏装置或元件响应于由光敏装置接收的一部分入射光以产生指示入射光的所接收部分的像素信号。每个成像像素105包括被耦合以接收和处理来自光敏装置的像素信号以产生像素输出信号的像素内电路系统。因此,来自成像像素的像素输出信号共同携带入射光所携带的图像的图像信息。

41.每个成像像素105中的像素内电路系统可以包括由衬底支撑的基于上述鞍形栅极源极跟随器晶体管300设计的源极跟随器块140。在这样的实施方式中,鞍形栅极源极跟随器晶体管300耦合到与将入射光转换为光电荷的光电传感器块110相邻放置的浮置扩散节点,并且光电荷被转移到浮置扩散节点以用于由源极跟随器块140读出以将光电荷转换成表示光电荷的电压像素信号。使用鞍形栅极源极跟随器晶体管300的源极跟随器块140的实施方式可以降低snr并增加每个成像像素105的读出信号链中的跨导(gm)。

42.图4示出了根据各种实施例的具有与2

×

2光电传感器115布置集成的鞍形栅极源极跟随器晶体管300的说明性cis像素400的简化物理布局。说明性布局可以是图1的框图的实施方式。所示布局的中心区包括具有四个光电传感器115(例如,光电二极管)的光电传感器块110。所示布局的上部包括具有相应触点的增益块120(例如,用于dcg)和重置块130。所示布局的下部包括选择块150和新颖的源极跟随器块140,实施为具有鞍形栅极结构310的鞍形栅极源极跟随器晶体管300。可以看出,各个部件块的宽度由布局的设计所建立。

43.如上所述,至少由于掺杂参数和边缘隔离结构,源极跟随器块140的有源层的有源区具有可定义的宽度(w),被指示为鞍形栅极源极跟随器晶体管300的物理布局宽度410。如上所述,物理布局宽度410是基于鞍形栅极源极跟随器晶体管300的平面宽度尺寸314。宽度410至少部分地由像素设计参数和制造工艺约束来确定。例如,如上所述,像素占用空间设计平衡了光电传感器块110和包括源极跟随器块140的支撑部件之间的分配空间。分配空间通常可以限定晶体管部件的最大(或标称)宽度。如图所示,鞍形栅极源极跟随器晶体管300的实施例可以占据与传统平面型源极跟随器晶体管基本相同的布局区域,包括占据相同的物理布局宽度410。这样的实施方式允许鞍形栅极源极跟随器晶体管300在传统间距参数(例如,在标准2

×

2cis像素布局的典型物理设计参数内)适配,包括为光电传感器块110留下所需区域,并允许至少将漏极触点355(通常对应于漏极区355)和栅极接触312放置在可以符合用于cis像素400的传统制造工艺的位置中。一些实施方式还包括源极触点。在其他实施方式中,如图所示,鞍形栅极结构310的源极区350由选择块150共享,并且没有其他信号耦合到其上;并且可能不需要源极触点。其他实施方式可以根据其他cis光学传感器块设计、其他制造工艺约束等使用其他合适的物理布局尺寸。

44.即使在电流沟道的物理布局宽度410和物理布局沟道长度与传统cis光电传感器块中使用的传统平面源极跟随器晶体管的电流沟道的物理布局宽度和物理布局沟道长度相似的实施方式中,鞍形栅极结构310也可以提供装置的明显更大的有效有源宽度。例如,鞍形栅极源极跟随器晶体管300的有效宽度可以对应于鞍形栅极结构310的物理布局宽度加上每个防护部315的防护板深度尺寸316。在所示的实施方式中,四个光电传感器115与浮置扩散节点415耦合,积累的光电荷从光电传感器115转移到浮置扩散节点415以供像素内

电路系统读出。虚线矩形示出了浮置扩散互连420,浮置扩散节点415可通过该浮置扩散互连420与鞍形栅极源极跟随器晶体管300的栅极触点312(以及重置块130和/或dcg的源极端子)耦合以作为像素400的读出链的一部分。

45.图5示出了根据各种实施例的具有2

×

4光电传感器115布置的集成鞍形栅极源极跟随器晶体管300的另一说明性cis像素500的简化物理布局。说明性布局类似于参考图4描述的布局,除了光电传感器块110被分成两个区,每个区具有四个光传感器115,使得cis像素500包括2

×

4布置中的八个光传感器115之外。在所示实施方式中,所有八个光电传感器115直接或经由浮置扩散互连420与浮置扩散节点415耦合,并且所有八个光电传感器115共享像素内电路系统。例如,所有八个光电传感器115都经由浮置扩散互连420与鞍形栅极源极跟随器晶体管300耦合。在一些实施方式中,2

×

4光电传感器115布置使用两个晶体管用于重置块130和dcg块120中的每个(例如,一个示出为在光电传感器块110a的上部上面,而一个示出为在光电传感器块110b的下部下面)。

46.图6示出了根据本文描述的各种实施例的cis像素的简化电路示意图600。所示的实施方式类似于图5的具有2

×

4光电传感器115布置的cis像素500。通过去除示意图600的标记为110b的部分,示意图600可以表示类似于图4的具有2

×

2光电传感器115布置的cis像素400的实施方式。示意图600示出了所有的光电传感器115和光电传感器块140的栅极(由鞍形栅极源极跟随器晶体管300实施)与浮置扩散节点415耦合。

47.可以以各种方式来制造鞍形栅极源极跟随器晶体管300的实施例,包括上述那些。图7示出了根据各种实施例的用于在集成电路的半导体衬底上制造鞍形栅极源极跟随器晶体管300的说明性集成电路部分制造工艺700。为了更清楚,图8a-8d示出了在沿着图7的制造工艺700的各个阶段处的制造中的鞍形栅极源极跟随器晶体管800的说明性视图。可以看出,制造工艺700的说明性结果、图8d所示的制造中的鞍形栅极源极跟随器晶体管800d与图3b中所示的鞍形栅极源极跟随器晶体管300基本相同。

48.图7中所示的制造工艺700的部分开始于阶段705,其中蚀刻和填充隔离区325,诸如浅沟槽隔离(sti)区(标记为“sti蚀刻”和“sti填充”)。在一些实施方式中,如本文所使用的蚀刻是使用光刻来执行的。这种隔离区325可以将源极跟随器晶体管与cis的其他部件(例如,源极跟随器块被并入其中的cis像素的相邻块)隔离。在阶段710处,可以执行“鞍形蚀刻”工艺。如图8a所示,将沟槽810蚀刻到衬底205中和/或蚀刻到先前形成的隔离区325中。这些沟槽810将限定沟道区的侧面并且将至少部分地限定鞍形栅极结构310的防护部315的几何形状。

49.在一些实施例中,制造工艺700在阶段720和730通过注入掩埋沟道以用作沟道区330而进行。图8b和8c分别大体示出了阶段720和730。图8b中的垂直箭头820表示用于将掩埋沟道的上部注入到衬底205中的基本上垂直的注入。图8c中的成角度箭头830表示用于经由沟槽810将掩埋沟道的轴向侧部注入到衬底205中的成角度注入。图8c还示出了在前面的图8b中注入的掩埋沟道的上部(标记为330a)。

50.制造工艺700可以在阶段740和750处通过形成栅极氧化层320(标记为“栅极ox”)以及沉积且蚀刻鞍形栅极结构310(标记为“poly沉积/蚀刻”)来进行。这些阶段的结果可以在图8d中看出。从阶段740,可以在图8d中看出,在沟道区330的顶部上方和轴向侧周围已经形成了栅极氧化层320。例如,在注入阶段之后,栅极氧化层320可以在衬底205的在沟道区

330的顶部和侧面周围的暴露表面上生长。从阶段750,可以在图8d中看到,鞍形栅极结构310被沉积和图案化以包括在沟道区330的顶部上方延伸的座部313和沿着沟道区330的轴向侧向下延伸的防护部315,所有这些都通过栅极氧化层320的介电特性与沟道区330绝缘。例如,通过沉积多晶硅、掩蔽与鞍形栅极结构310相对应的多晶硅区并蚀刻多晶硅的未掩蔽部分以在鞍形栅极结构310后面留下来形成栅极结构310。如图所示,栅极触点312也可以图案化到鞍形栅极结构310的座部313上。

51.在阶段740和750之前,得到的鞍形栅极源极跟随器晶体管300的沟道区330可以包括在阶段720中注入并在顶部处以衬底205的顶部表面为界的上部,以及在阶段730中注入并在衬底205的蚀刻侧表面(即,沟槽810的内表面)处为界的轴向侧部。然后,可以根据衬底的界定了沟道区330的顶部表面和蚀刻侧表面,鞍形栅极结构310(和栅极氧化层320)被形成在沟道区330的上注入部分和轴向侧注入部分周围。

52.可以看出,鞍形栅极源极跟随器晶体管300的栅极氧化层320、鞍形栅极结构310和其他结构的制造可以与标准制造工艺技术(诸如沉积和蚀刻)集成。此外,制造工艺700的其他阶段(包括在所示阶段之前和之后的那些阶段)可以根据用于mosfet、cis部件等的标准制造工艺来实施。然而,所示出的制造工艺700的某些方面特别适合于本文描述的用于鞍形栅极源极跟随器晶体管300的注入的上下文。例如,制造包括围绕沟道区的一部分包裹的栅极的传统的所谓fin-fet晶体管通常以不同于所示制造工艺700的方式的方式来执行。对于这样的fin-fet晶体管,掺杂衬底通常可以形成为沟道区的形状,并且栅极可以在掺杂衬底的顶部和侧面周围沉积,从而制造独立的(例如,分立的)晶体管部件。这种fin-fet工艺不包括所示制造工艺700的各个阶段,诸如隔离区的蚀刻和填充(阶段705)、鞍形蚀刻(阶段710)等。

53.一些现代cis实施方式被制造为使得源极跟随器的平面布局宽度约为300nm。利用这样的工艺,鞍形栅极源极跟随器晶体管300的一些实施方式可以被制造为使得防护部315具有大约155nm的防护深度尺寸316和大约50nm的宽度(厚度)。一些实施方式可以使用高纵横比蚀刻工艺,该工艺已结合某些存储器和逻辑应用而采用。在一些实施例中,为了保持期望量的轴向侧掩埋沟道注入(例如,在制造工艺700的阶段730处),制造具有大约两倍于平面宽度尺寸314的防护深度尺寸316的鞍形栅极结构310。在这样的实施例中,座部313有效地为装置的有效有源宽度产生了w,而防护部315为装置的有效有源宽度产生了额外的4w,导致装置的有效有源宽度总共增加了五倍。

54.将理解的是,当元件或部件在本文中被称为“连接到”或“耦合到”另一元件或部件时,它可以连接或耦合到另一元件或部件、或者中间元件或部件也可能存在。相反,当元件或部件被称为“直接连接到”或“直接耦合到”另一个元件或部件时,它们之间不存在中间元件或部件。将理解的是,尽管本文可以使用术语“第一”、“第二”、“第三”等来描述各种元件、部件,但是这些元件、部件、区不应受这些术语的限制。这些术语仅用于将一个元件、部件与另一个元件、部件区分开来。因此,在不脱离本发明的教导的情况下,下面讨论的第一元件、部件可以被称为第二元件、部件。如本文所使用的,术语“逻辑低”、“低状态”、“低电平”、“逻辑低电平”、“低”或“0”可互换使用。术语“逻辑高”、“高状态”、“高电平”、“逻辑高电平”、“高”或“1”可互换使用。

55.如本文所用的,术语“一”、“一个”和“该”可包括单数和复数参考。将进一步理解,

术语“包括”、“包含”、“具有”及其变体,当在本说明书中使用时,指定所述特征、步骤、操作、元件和/或部件的存在,但不排除一个或多个其他特征、步骤、操作、元件、部件和/或它们的组的存在或添加。相比之下,术语“由

……

组成”当在本说明书中使用时,指定所述特征、步骤、操作、元件和/或部件,并且排除附加特征、步骤、操作、元件和/或部件。此外,如本文所使用的,词语“和/或”可指并涵盖相关所列的一项或多项的任何可能组合。

56.虽然本文参考说明性实施例描述了本发明,但是该描述并不旨在被解释为限制性的。相反,说明性实施例的目的是使本领域技术人员更好地理解本发明的精神。为了不模糊本发明的范围,省略了众所周知的工艺和制造技术的许多细节。在参考描述时说明性实施例以及其他实施例的各种修改对于本领域技术人员来说将是显而易见的。因此,所附权利要求旨在涵盖任何此类修改。

57.此外,本发明的优选实施例的一些特征可以在没有其他特征的相应使用的情况下被有利地使用。因此,上述描述应被认为仅是对本发明原理的说明,而不是对其进行限制。本领域技术人员将理解落入本发明范围内的上述实施例的变化。因此,本发明不限于以上讨论的特定实施例和说明,而是由以下权利要求及其等同物来限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。