只读存储器

1.相关申请的交叉引用

2.本技术要求于2020年12月18日提交的法国申请号fr 2013741的权益,该申请通过引用并入本文。

技术领域

3.本公开一般涉及电子系统和设备,尤其是存储器电路或存储器。本公开更具体地涉及只读存储器(rom)。

背景技术:

4.目前,电子设备的小型化及其性能的改善需要改善数据存储设备。事实上,存储器必须越来越小并且存储越来越多的数据。

5.存在多种不同的存储器类型。实际上,在某些存储器中,可以随时查阅和/或修改存储的数据,而其他存储器仅在通电时存储数据。

6.闪存是一种易失性存储存储器,即可以随时写入和/或修改数据的存储器。

7.rom是一种不可重写存储器,通常在制造过程中将数据写入其中,并且不再能够被修改。存储在rom中的数据只能被查阅。

8.希望至少部分改善已知rom的某些方面。

技术实现要素:

9.需要更小的rom。

10.需要rom更能抵抗黑客技术,如逆向工程技术。

11.实施例克服了已知rom的全部或部分缺点。

12.实施例提供了一种rom,其包括至少一个第一可重写存储器单元。

13.根据一个实施例,所述第一存储器单元为e-stm型。

14.根据一个实施例,rom还包括至少一个包括第二存储器单元,其包括晶体管。

15.根据实施例,晶体管是mos晶体管。

16.根据实施例,晶体管为n沟道mos晶体管。

17.根据实施例,当第一存储器单元或第二存储器单元的阈值电压高于阈值时,则所述第一存储器单元或第二存储器单元表示第一位值,并且当所述阈值电压低于所述阈值时,然后所述第一存储器单元或第二存储器单元表示与所述第一值不同的第二位值。

18.根据实施例,第一存储器单元和第二存储器单元包括一种结构,该结构依次包括:第一导电类型的掺杂衬底;位于所述衬底上的第二导电类型的第一半导体层;以及位于所述第一半导体层上的第一导电类型的第二半导体层。

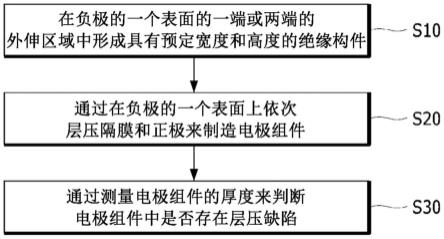

19.根据实施例,第一存储器单元包括彼此堆叠的第一绝缘栅极和第二绝缘栅极。

20.根据实施例,所述第一存储器单元的第一绝缘栅极和第二绝缘栅极布置在所述结构的表面的第一部分上。

21.根据实施例,第二存储器单元包括第三绝缘栅极,其厚度等于第一存储器单元的第一绝缘栅极和第二绝缘栅极的厚度之和。

22.另一个实施例提供了一种制造rom的方法,该rom包括至少一个第三可重写存储器单元和至少一个第四存储器单元,该存储器单元包括晶体管,该方法包括以下连续步骤:在半导体结构上依次沉积第一绝缘层和第一栅极层;在第一栅极层中的第四存储器单元的晶体管的栅极位置处形成腔体;以及依次沉积第二绝缘层和第二栅极层。

23.根据一个实施例,该结构依次包括:第一导电类型的第二掺杂衬底;位于所述衬底上的第二导电类型的第三半导体层;以及位于所述第一半导体层上的第一导电类型的第三半导体层。

24.根据一个实施例,该方法还包括蚀刻第一绝缘栅极和第二绝缘层的步骤以及蚀刻能够形成所述至少一个第二存储器单元的绝缘栅极的第二栅极层的步骤。

25.根据实施例,第三可重写存储器单元为e-stm类型。

26.根据实施例,该方法还包括蚀刻第一绝缘栅极和第二绝缘层的步骤以及蚀刻第一栅极层和第二栅极层的步骤,使得能够形成e-stm类型的第三存储器单元的两个绝缘栅极的堆叠。

27.根据实施例,半导体结构包括由半导体材料制成的至少一个沟槽,并且第四存储器单元的晶体管的栅极位置在一侧由所述至少一个沟槽横向界定。

28.另一个实施例提供了一种rom,该rom至少包括e-stm类型的第一存储器单元和第二存储器单元,每个存储器单元包括彼此堆叠的第一绝缘栅极和第二绝缘栅极,其中第一绝缘栅极电耦合到第二绝缘栅极。

29.根据一个实施例,当第一存储器单元或第二存储器单元的阈值电压高于阈值时,则所述第一存储器单元或第二存储器单元表示第一位值,并且当所述阈值电压低于所述阈值时,然后所述第一或第二存储器单元表示与所述第一值不同的第二位值。

30.根据实施例,所述第一存储器单元还包括n型掺杂阱。

31.根据一个实施例,所述阱具有在1x10^13至5x10^13at.cm^(-3)范围内的掺杂元素植入物浓度。

32.根据一个实施例,所述阱布置在第一存储器单元的第一栅极下。

33.根据一个实施例,第一存储器单元的第一绝缘栅极包括第一绝缘层,并且第二存储器单元的第一绝缘栅极包括第二绝缘层。

34.根据实施例,第一绝缘层的材料不同于第二绝缘层的材料。

35.根据实施例,第一绝缘层的材料和第二绝缘层的材料为氧化硅。

36.根据实施例,第一绝缘层的厚度不同于第二绝缘层的厚度。

37.根据实施例,第一绝缘层的厚度和第二绝缘层的厚度在5到20nm的范围内。

38.根据一个实施例,第一绝缘层的厚度约为15nm,第二绝缘层的厚度约为8.7nm。

39.根据实施例,第一存储器单元和第二存储器单元依次由以下结构形成:第一导电类型的掺杂衬底;位于所述衬底上的第二导电类型的第一半导体层;以及位于所述第一半导体层上的第一导电类型的第二半导体层。

40.根据一个实施例,第一绝缘栅极和第二绝缘栅极形成在所述结构表面的第一部分上。

(1)或“零”(0)。

61.rom 100更具体地包括两种不同类型的存储器单元,每种存储器单元表示位的值。第一类型的存储器单元102适于表示二进制“1”,第二类型的存储器单元104适于表示二进制“0”。在图1中,存储器单元102示出为空块,存储器单元104示出为包括十字的块。图2示出了能够在rom 100类型的rom中使用的两种类型的存储器单元的第一实施例。类似地,图8和图10分别示出了能够在rom中使用的两种类型的存储器单元的实施例。

62.rom 100可以附带允许其操作的电路,如读出电路、加密和/或解密电路等。图1中未示出这些电路。

63.图2是两个存储器单元200和202的一个实施例的横截面图,这两个存储器单元适用于与图1相关的rom 100类型的rom。

64.存储器单元200示出在图2的部分(a)(图2的左侧部分)上,存储器单元202示出在图2的部分(b)(图2的右侧部分)上。结合图4和图5描述制造存储器单元200和202的方法的实施方式的示例。

65.存储器单元200和202在结构204上并排形成。结构204包括p型掺杂半导体衬底206(p-),例如,轻度p型掺杂。图2中仅示出衬底206的上部。衬底206例如由掺杂有硼原子的硅制成。该结构还包括形成在衬底206的表面210上的半导体层208。层208(n-)为n型掺杂,例如,轻度n型掺杂。层208例如由掺杂有磷原子的硅制成。层208的厚度范围为0.5至10μm,例如,约为1μm。该结构还包括形成在层208的表面214上的半导体层212(p-)。层212是p型掺杂的,例如,轻度p型掺杂。层212例如由掺杂有硼原子的硅制成。层212的厚度范围为0.1至1μm,例如,约为0.5μm。

66.存储器单元200是n沟道金属氧化物半导体晶体管,其n型掺杂源区由层208形成,p型掺杂衬底区由层212形成。这里,n沟道mos晶体管的衬底区域指定p型掺杂衬底或阱,其一部分形成晶体管沟道区域。

67.阱216(n )由层212表面的第一部分218形成,位于图2部分a的左侧。阱216是n型掺杂的,例如,重n型掺杂。阱216形成存储器单元200的漏极区域。可以在阱216上形成触点217。例如,阱216由掺杂有磷原子的硅制成。阱216向下延伸的深度范围为0.01至0.5μm,例如约为0.2μm。

68.绝缘栅极220形成在层212表面的第二部分222上。部分222位于图2部分(a)的右侧,并且布置在部分218旁边。绝缘栅极220形成存储器单元200的栅极。绝缘栅极220包括两个绝缘层224和226以及栅极层228。绝缘层224位于层212表面的部分222上。绝缘层224由氧化硅(sio2)制成,其厚度范围为5至10nm,例如,约为8.7nm,即87埃。绝缘层226位于层224的表面上。绝缘层226由氧化物-氮化物-氧化物合金制成,其厚度范围为10至15nm,例如,约为12.7nm,即127埃。栅极层228位于绝缘层226的表面上。栅极层228由多晶硅制成,其厚度范围为50至500nm,例如,约为200nm。

69.任选地,n型掺杂阱230(i)可以由部分222形成。阱230可以使能调整由存储器单元200形成的晶体管的阈值电压。

70.存储器单元200通过半导体沟槽232与存储器单元202分离,半导体沟槽232延伸穿过层212的整个厚度,即一直延伸到层208的表面214。此外,层208可以在其与沟槽232接触的位置处包括加厚部234。加厚部234可以通过注入磷原子获得。沟槽232例如由多晶硅制

成。沟槽232的宽度范围为50nm至500nm,例如,约为120nm。

71.存储器单元202是e-stm(嵌入式沟槽内选择存储器,embedded selected in trench memory)类型的存储器单元。e-stm型存储器单元是通常用于闪存中的可重写存储器单元。存储器单元202具有与存储器单元200的结构相似的结构,并且由此形成镜像。因此,与存储器单元200类似,存储器单元202包括由层212表面的部分238形成的阱236,类似于阱216。部分238位于图2部分(b)的右侧。可以在阱236上形成触点239。存储器单元202还包括形成在层212表面的部分240上的两个绝缘栅极的堆叠,该部分位于图2部分(b)的左侧部分。部分240从沟槽232延伸到层212表面的部分238。两个绝缘栅极的堆叠在部分240上依次包括:与制造分散体内的存储器单元200的绝缘层224相同的绝缘层242,直接位于部分240上;位于绝缘层242上的第一栅极层244;绝缘层246,与存储器单元200的绝缘层226相同(制造差异内),直接位于层244上;以及位于绝缘层246上的第二栅极248。

72.因此,存储器单元202包括由层242和244形成的第一绝缘栅极,其上具有由层246和248形成的第二绝缘栅极。

73.此外,与存储器单元200类似,存储器单元202可以任选地包括由层212表面的部分240形成的n型掺杂阱250(i)。阱250可以使能调整由存储器单元200形成的晶体管的阈值电压。

74.栅极层244和248例如由多晶硅制成。例如,栅极层244和248具有接近或甚至相等的厚度。栅极层244和248的厚度范围为50至500nm,例如,约为100nm。

75.存储器单元200的绝缘栅极220和存储器单元202的两个绝缘栅极的堆叠具有接近或甚至相等的厚度。更具体地说,存储器单元200的栅极层228的厚度等于存储器单元202的栅极层244和248的厚度之和。

76.存储器单元200和202具有不同的阈值电压,这使得它们能够用作rom的存储器单元。实际上,存储器单元的阈值电压电平可以用作数据位编码装置。根据一个示例,当阈值电压的电平大于参考电平时,存储器单元可以表示二进制“一”(1),并且相反地当阈值电压的该电平小于该参考电平时,存储器单元可以表示二进制“零”(0)。根据一种变型,可以设想相反的情况。对于存储器单元200类型的存储器单元,即对于晶体管,阈值电压基于所使用尺寸和的材料来通过制造来定义和调整。对于存储器单元202类型的存储器单元,阈值电压基于所使用的尺寸和材料来通过制造来定义,但也可以在其使用期间通过擦除或写入存储器单元的操作来调整。关于图3,进一步详细描述了存储器单元202类型的存储器单元的阈值电压的调整。

77.结合图4和图5描述了制造存储器单元200和202的方法。

78.图3是示出结合图2描述的存储器单元200和202类型的存储器单元的阈值电压电平的图表。此图表的纵坐标轴以伏特(v)为单位。

79.按照惯例,将存储器单元200(即由mos晶体管形成的存储器单元)类型的存储器单元的阈值电压vtmos设置为1v作为基准。该电压vtmos在图3中用线支承附图标记vtmos表示。

80.图3的图形是通过测量在同一衬底上形成的多个相同尺寸(在制造差异范围内)的存储器单元202类型的存储器单元的阈值电压绘制的。

81.第一组点301表示在制造结束时,即在擦除或写入操作之前,对存储器单元202类

型的存储器单元的阈值电压的测量。阈值电压从大约-3v延伸到大约1.8v。阈值电压延伸的范围相当宽,并且不能区分存储器单元202类型的存储器单元的阈值电压和存储器单元200类型的存储器单元的阈值电压。

82.第二组点302表示存储器单元202类型的存储器单元在全部提交擦除操作后的阈值电压测量值。阈值电压从大约-3.5v扩展到大约-1.2v。该范围与参考阈值电压vtmos相当远。根据实施例,考虑包括存储器单元200类型的存储器单元和存储器单元202类型的存储器单元的rom,存储器单元202类型的存储器单元具有比存储器单元200类型的存储器单元更低的阈值,从而存储器单元202类型的存储器单元可以表示二进制“零”(0),存储器单元200类型的存储器单元可以表示二进制“一”(1)。根据备选实施例,可以设想相反的情况。

83.第三组点303表示存储器单元202类型的存储器单元在全部提交到写入操作后的阈值电压测量值。阈值电压从约2.6v延伸至约4.8v。该范围与参考阈值电压vtmos相差甚远。根据另一实施例,考虑包括存储器单元200类型的存储器单元和存储器单元202类型的存储器单元的rom,存储器单元202类型的存储器单元具有比存储器单元200类型的存储器单元更高的阈值电压,其中,存储器单元202类型的存储器单元可以表示二进制“1”(1),存储器单元200类型的存储器单元可以表示二进制“0”(0)。根据替代实施例,可以设想相反的情况。

84.图4和图5包括(a)、(b)、(c)和(d)视图,说明了在同一衬底上并排制造两个存储器单元200和202类型的存储器单元的方法的连续步骤。

85.与图2类似,每个视图(a)、(b)、(c)和(d)包括视图左侧的部分(a)和视图右侧的部分(b)。在视图(a)至(d)的部分(a)中制造存储器单元200类型的存储器单元,在视图(a)至(d)的部分(b)中制造存储器单元202类型的存储器单元。

86.视图(a)示出了制造结构401的步骤,该结构401为结合图2描述的结构204类型。因此,结构401包括部分示出的p型掺杂衬底403,该p型掺杂衬底403具有位于其上的n型掺杂半导体层405和p型掺杂半导体层407的堆叠。衬底403以及层405和407分别与衬底206以及结合图2描述的层208和212相同。因此,与层208类似,层405在沟槽232类型的沟槽位置处展示加厚部409,该沟槽类型如图2所述。层206和208依次沉积在衬底403上以形成结构401。

87.视图(a)进一步说明了形成沟槽411的步骤,该沟槽411与图2所述的沟槽232相同。该形成步骤例如包括在层405的加厚部409的水平蚀刻沟槽的步骤和填充该沟槽的步骤。填充步骤可以在沟槽壁氧化步骤之前进行。氧化步骤可以例如能够避免在沟槽填充材料与层407的材料之间的欧姆接触。根据示例,沟槽填充有多晶硅。为此,沟槽可以填充非晶硅,然后进行一个或多个晶化步骤以形成多晶硅。

88.在蚀刻沟槽的步骤之后,可以执行注入步骤,以形成结合图2描述的阱230和250类型的阱。

89.视图(a)进一步说明了在结构401的整个表面上沉积绝缘层413的步骤。该步骤连续于形成沟槽411的步骤。绝缘层413由与结合图2所述的层224和242相同的材料制成。绝缘层413的厚度在5到10nm的范围内,例如,在8.7nm的量级,即87埃。

90.视图(a)进一步示出了在绝缘层413的整个表面上沉积栅极层415的步骤。栅极层415由与结合图2描述的栅极层244相同的材料制成。栅极层415具有在20nm到200nm范围内的厚度,例如,在100nm量级。

91.视图(b)示出了蚀刻至少向下延伸至绝缘层413表面的层415中的腔体417的步骤。腔体417形成在视图(b)的部分(a)的侧上。更具体地说,该腔体417的位置指定要制造的存储器单元200类型的存储器单元的绝缘栅极的位置。腔体417例如由包括掩蔽步骤和蚀刻步骤的方法形成。

92.视图(b)进一步说明了在蚀刻步骤后获得的结构的整个表面上沉积绝缘层419的步骤,尤其是在腔体417的底部。绝缘层419由与结合图2所述的层226和246相同的材料制成。绝缘层413的厚度范围为10至15nm,例如,约为12.7nm,即127埃。

93.视图(c)示出了在视图(b)所示结构的整个表面上沉积栅极层421的步骤。栅极层421填充整个腔体417,并且其表面在视图(c)中被定为水平。栅极层421由与结合图2描述的栅极层228和248相同的材料制成,即,例如多晶硅。栅极层421的厚度范围为20至200nm,例如,约为80nm。

94.视图(d)示出蚀刻步骤,用于使存储器单元200类型的存储器单元的绝缘栅极423与存储器单元202类型的存储器单元的两个绝缘栅极的堆叠425独立化。在该步骤期间,绝缘栅极423和堆叠425被横向界定,之后去除多余的层413、415、419和421。该步骤可以包括使用多个连续掩蔽和蚀刻步骤。关于图6和图7,对该步骤俯视图中的结果进行了更详细的描述。

95.视图(d)进一步说明了制造方法的完成。该完成包括:掺杂与图2所述的阱216和218类似的两个阱427和429;以及在阱427和429上形成触点431,类似于图2所述的触点217和239。

96.视图(d)的部分(a)接着示出了存储器单元200类型的存储器单元433,部分(b)接着示出了存储器单元202类型的存储器单元435。

97.本文所述方法的优点在于,它能够使用图2所述的存储器单元制造rom,其中只有一个蚀刻步骤,即视图(b)所述的蚀刻步骤,能够区分表示二进制“零”的存储器单元和表示二进制“一”的存储器单元。

98.图6示出了与图1相关的rom 100类型的rom 500简化实施例的更详细俯视图。

99.rom 500包括以两行三列排列的六个存储器单元。根据一个示例,rom 500包括五个存储器单元501,其类型为关于图2所述的存储器单元202,以及一个存储器单元503,其类型为关于图2所述的存储器单元200。

100.在rom 500中,存储器单元的行成对形成。在每对行中,两个存储器单元行由图2所述的半导体沟槽232类型的半导体沟槽505分隔。沟槽505沿着存储器单元行完全延伸,因此对于同一行的所有存储器单元是公共的。根据示例,可以在沟槽505的端部形成触点。在俯视图中,沟槽505的宽度例如在20到200nm的范围内,例如在100nm的量级。

101.此外,同一行的存储器单元501和503具有公共绝缘栅极507。更具体地说,存储器单元503具有其绝缘栅极(即图2所述的绝缘栅极220)与存储器单元501的第二绝缘栅极相同(即,由图2所述的层246和248形成的绝缘栅极)。根据示例,触点可以形成在绝缘栅极507的端部。在俯视图中,绝缘栅极507的宽度例如在50到500nm的范围内,例如在90nm的量级。

102.此外,同一列的存储器单元501具有公共第一绝缘栅极509。存储器单元501的第一绝缘栅极509对应于由绝缘层242和结合图2描述的栅极层244形成的绝缘栅极。当列包括存储器单元503(即,包括单个绝缘栅极的存储器单元)时,绝缘栅极509在该存储器单元的绝

缘栅极的水平处示出凹槽。实际上,如关于图4和图5所述,能够形成存储器单元501的第一栅极层的栅极层在形成存储器单元503的绝缘栅极的位置被蚀刻。根据示例,触点511可以形成在关于图2所述的阱216和236类型的n型掺杂阱的端部水平。在俯视图中,绝缘栅极509的宽度例如在20到200nm的范围内,例如在60nm的量级。

103.使用存储器单元501和503的优点在于,它们能够形成具有0.037μm2大小的俯视面积的存储器单元,该面积小于rom的存储器单元面积,而rom的存储器单元面积通常为0.052μm2大小。

104.另一个优点是,使用存储器单元501和503的rom对逆向工程攻击不太敏感。

105.图7示出了rom 600的另一个简化实施例的更详细俯视图。

106.rom 600类似于rom 500,包括存储器单元501和503。与rom 500相反,rom 600包括四个存储器单元501和两个存储器单元503。此外,两个存储器单元503位于同一列中。

107.与rom 500类似,在rom 600中,存储器单元行成对形成。在每对行中,两个存储器单元行由半导体沟槽505分隔,该半导体沟槽505沿着存储器单元行延伸,并且因此对同一行的所有存储器单元共用。此外,同一行的存储器单元501和503具有公共绝缘栅极507。

108.此外,与rom 500的绝缘栅极509一样,同一列的存储器单元501具有公共第一绝缘栅极601。存储器单元501的第一绝缘栅极601对应于由绝缘层242和结合图2描述的栅极层244形成的绝缘栅极。当列包括存储器单元503(即,包括单个绝缘栅极的存储器单元)时,绝缘栅极601在该存储器单元503的绝缘栅极的水平处示出凹槽。此外,当列并排包括两个存储器单元503时,出于蚀刻装置的精度原因,在晶体管503的栅极位置处的绝缘栅极601中形成凹槽在技术上可能是困难的。因此,绝缘栅极601的宽度被扩大,使得在形成凹槽后剩余的部分在图7中的水平方向上足够宽,以到达相邻列的绝缘栅极。根据一个示例,可以在绝缘栅极601的端部形成触点。

109.图8是两个存储器单元700和702的另一个实施例的横截面图,这两个存储器单元700和702适用于与图1相关的rom 100类型的rom中。

110.存储器单元700示出在图8的部分(a)(图8的左侧部分)上,存储器单元702示出在图8的部分(b)(图8的右侧部分)上。

111.存储器单元700和702与结合图2描述的存储器单元202相似。下文将不再详细描述存储器单元202、700和702共有的元件,并且仅突出示出它们的差异。

112.与存储器单元202类似,存储器单元700和702形成在由堆叠形成的结构204上,堆叠依次包括:p型掺杂半导体衬底206;n型掺杂半导体层208;以及p型掺杂半导体层212。

113.层212包括在其表面部分238水平延伸的n型掺杂阱236。触点239能够与该阱接触。

114.与存储器单元200和202类似,存储器单元700和702由在层208中形成的半导体沟槽232隔开,该沟槽一直延伸到层208的加厚部234。

115.与存储器单元202类似,存储器单元700和702包括形成在层212表面的部分240上的两个绝缘栅极的堆叠。第一绝缘栅极由绝缘层242和栅极层244形成,第二绝缘栅极由绝缘层246和栅极层248形成。然而,存储器单元700和702与存储器单元202的不同之处在于,它们的绝缘栅极彼此耦合(优选地连接)。然后,存储器单元700和702的操作类似于晶体管的操作。根据一个示例,存储器单元700和702的两个绝缘栅极通过在第二绝缘栅极中形成一直延伸到第一绝缘栅极的通孔来连接。通过将此通孔连接到另一个连接到第二绝缘栅极

的通孔,两个绝缘栅极连接。

116.存储器单元700和702彼此不同之处在于,存储器单元700包括形成在两个绝缘栅极的堆叠下的层212中的阱703(i),并且存储器单元702不包括该阱703。703阱与图2所述的250阱相似。因此,通过n型掺杂获得阱703。阱703的掺杂元素浓度可以在1x10^13至5x10^13at.cm^(-3)范围内,例如,在3x10^13at.cm^(-3)的量级。阱703使得能够调整存储器单元700的阈值电压。有关图9,对阱的效果进行了更详细的描述。

117.使用存储器单元700和702的优点在于,在俯视图中,存储器单元700和702是不可分割的。

118.图9是示出与图2相关的存储器单元700和702类型的存储器单元的阈值电压电平的图表。此图表的纵坐标轴以伏特(v)为单位。横坐标轴表示以at.cm^(-3)的703阱的不同掺杂水平。

119.为了获得该图,在两组不同的存储器单元700和702上进行了测量,其中阱703的每个掺杂水平包括两组代表不同电压阈值的点。

120.两个第一组801表示不包括阱703的存储器单元702的阈值电压的测量。阈值电压的值在0.850和1.350v之间延伸。

121.两个第二组802表示存储器单元700的阈值电压测量值,该存储器单元700包括掺杂水平为1x10^13at.cm^(-3)量级的阱703。阈值电压的值在0.330和0.900v之间延伸。

122.两个第三组803表示存储器单元700的阈值电压测量值,该存储器单元700包括掺杂水平为2x10^13at.cm^(-3)量级的阱703。阈值电压的值在-0.250和0.450v之间延伸。

123.两个第四组804表示存储器单元700的阈值电压测量值,该存储器单元700包括掺杂水平为3x10^13at.cm^(-3)量级的阱703。阈值电压的值在-1.270和0v之间延伸。

124.阱703的植入剂量水平的增加使得能够修改存储器单元700的阈值电压。与存储器单元200和202类似,存储器单元700和702可以通过使用其阈值电压作为二进制数据编码装置,在存储器100类型的rom中使用。根据示例,存储器单元702可以例如表示二进制“零”(0),并且存储器单元700可以例如表示二进制“一”(1)。根据一种变型,可以设想相反的情况。

125.图10是两个存储器单元900和902的另一个实施例的横截面图,这两个存储器单元900和902适用于与图1相关的rom 100类型的rom。

126.存储器单元900示出在图10的部分(a)(图10的左侧部分)中,存储器单元902示出在图10的部分(b)(图10的右侧部分)中。

127.存储器单元900和902与图2所述的存储器单元700相似。下文将不再详细描述存储器单元700、900和902共有的元件,并且仅突出示出它们的差异。

128.与存储器单元700类似,存储器单元900和902由堆叠形成的结构204形成,堆叠依次包括:p型掺杂半导体衬底206;n型掺杂半导体层208;以及p型掺杂半导体层212。

129.层212包括在其表面部分238水平延伸的n型掺杂阱236。触点239能够与该阱接触。

130.与存储器单元700和702类似,存储器单元900和902由在第208层中形成的半导体沟槽232隔开,该沟槽一直延伸到第208层的加厚部234处。

131.与存储器单元700类似,存储器单元900和902包括形成在层212表面的部分240上的两个绝缘栅极的堆叠。然而,存储器单元900和902包括两个不同绝缘栅极的堆叠。更具体

地说,存储器单元900包括形成在层212表面的部分240上的两个绝缘栅极的堆叠905。堆叠905依次包括:直接置于部分240上的绝缘层907;位于绝缘层907上的第一栅极层244;直接位于层244上的绝缘层246;以及位于绝缘层246上的第二栅极层248。

132.存储器单元902包括在层212表面的部分240上形成的两个绝缘栅极的堆叠909。堆叠909依次包括:直接置于部分240上的绝缘层911;位于绝缘层911上的第一栅极层244;直接位于层244上的绝缘层246;以及位于绝缘层246上的第二栅极层248。

133.与存储器单元702类似,存储器单元900和902的两个绝缘栅极相互耦合(最好连接)。然后,存储器单元900和902的操作类似于晶体管的操作。

134.根据一个实施例,绝缘层907和911由不同的材料制成,例如,与图2所述的绝缘层242相同的材料以及高压绝缘材料,如氧化硅。层907和911还具有不同的厚度。通过改变层907和911的厚度和材料,可以调整存储器单元900和902的阈值电压。

135.根据一个实施例,绝缘层907由高压绝缘材料制成,其厚度范围为10至20nm,例如,约为15nm。绝缘层911与图2所述的绝缘层242相同,即,由氧化硅制成,厚度在5到10nm之间,例如约为8.7nm。

136.存储器单元900和902包括形成在层212中并且从层212表面的部分240延伸的阱703。根据替代实施例,存储器单元900和902可不包括阱703。

137.使用存储器单元900和902的优点在于,在俯视图中,存储器单元900和902是不可分割的。

138.所述实施例进一步针对具有下文所述全部或部分特性的rom。

139.一种rom,至少包括e-stm类型的第一存储器单元和第二存储器单元(700、702;900、902),每个存储器单元包括彼此堆叠的第一绝缘栅极(242,244;907;909)和第二绝缘栅极(246、248),其中第一绝缘栅极(242,244;907;909)电耦合到第二绝缘栅极(246,248)。

140.一种存储器,其中当第一存储器单元(700;900)或第二存储器单元(702;902)的阈值电压高于阈值时,则所述第一存储器单元或第二存储器单元(702;902)表示第一位值,并且当所述阈值电压低于所述阈值时,则所述第一存储器单元或第二存储器单元(702;902)表示与第一值不同的第二位值。

141.一种存储器,其中所述第一存储器单元(700;900)还包括n型掺杂阱(703)。

142.一种存储器,其中所述阱具有在1x10^13至5x10^13at.cm^(-3)范围内的掺杂元素注入浓度。

143.一种存储器,其中所述阱(703)布置在所述第一存储器单元(700)的第一栅极(242、244)下。

144.一种存储器,其中第一存储器单元(900)的第一绝缘栅极(907,244)包括第一绝缘层(907),并且第二存储器单元(902)的第一绝缘栅极(909,244)包括第二绝缘层(909)。

145.一种存储器,其中第一绝缘层(907)的材料不同于第二绝缘层(909)的材料。

146.一种存储器,其中第一绝缘层(907)和第二绝缘层(909)的材料为氧化硅。

147.一种存储器,其中第一绝缘层(907)的厚度不同于第二绝缘层(909)的厚度。

148.一种存储器,其中第一绝缘层(907)的厚度和第二绝缘层(909)的厚度在5到20nm的范围内。

149.一种存储器,其中第一绝缘层(907)的厚度约为15nm,第二绝缘层(909)的厚度约

为8.7nm。

150.一种存储器,其中第一存储器单元和第二存储器单元(700,702;900,902)依次由结构(204)形成:第一导电类型的掺杂衬底(206);位于所述衬底(206)上的第二导电类型的第一半导体层(208);以及位于所述第一半导体层(208)上的第一导电类型的第二半导体层(212)。

151.一种存储器,其中第一绝缘栅极和第二绝缘栅极(242、244、246、248;907、909)形成在所述结构(204)表面的第一部分(240)上。

152.一种制造rom的方法,该rom至少包括e-stm类型的第一存储器单元和第二存储器单元(700,702;900,902),每个存储器单元包括彼此堆叠的第一绝缘栅极(242,244;907,909)和第二绝缘栅极(246,248),其中通孔被穿过第一绝缘栅极(242,244;907,909)形成,以将第一绝缘栅极(242、244;907、909)耦合到第二绝缘栅极(246、248)。

153.已经描述了各种实施例和变型。本领域技术人员将理解,可以组合这些不同实施例和变型的某些特征,并且本领域技术人员将想到其他变型。

154.最后,基于上文给出的功能指示,所述实施例和变型的实际实现在本领域技术人员的能力范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。