一种基于fpga的adc芯片的动态指标测量系统及方法

技术领域

1.本发明涉及雷达信号分析和测试技术领域,具体涉及一种基于fpga的adc芯片的动态指标测量系统及方法。

背景技术:

2.当前在雷达信号采集系统领域中,雷达信号采集系统主要采用adc结合fpga的系统架构对雷达信号进行采集和预处理。在采集系统开发与测试过程中,经常需要对adc的动态指标进行测量与分析。传统方法是工程师利用fpga开发调试软件在线抓取adc采集的数据,对数据进行初步处理,然后导入matlab,利用matlab进行指标分析,测试流程如图1所示。

3.这种方式存在的主要问题是测试速度慢,当需要测试多组数据时,需要测试人员频繁操作,极其耗费时间和精力,出错率高。

技术实现要素:

4.有鉴于此,本发明提供了一种基于fpga的adc芯片的动态指标测量系统及方法,能够解决测试速度慢,需要测试人员频繁操作,出错率高的技术问题。

5.为了解决上述技术问题,本发明是这样实现的。

6.一种基于fpga的adc动态指标测量系统,所述系统包括:所述基于fpga的adc芯片的动态指标测量系统,包括上位机、软件模块及硬件逻辑模块;

7.所述上位机用于下发指令信息,并对计算出的adc芯片指标进行动态显示;所述上位机通过外部传输接口与所述硬件逻辑模块进行交互;

8.所述软件模块接收所述硬件逻辑模块的处理结果数据,并将运算完成后的数据发送给所述硬件逻辑模块;所述软件模块用于配置adc芯片以及对adc的指标进行运算;

9.所述硬件逻辑模块接收所述上位机的控制信息、以及所述软件模块的运算结果,用于进行数据转发和数据预处理。

10.优选地,所述软件模块包括adc芯片配置模块及adc芯片指标计算模块;所述adc芯片配置模块用于设置所述adc芯片的寄存器配置参数,以及控制所述adc芯片的工作模式,将配置参数经过硬件逻辑模块转发给adc芯片;所述adc芯片指标计算模块用于读取所述硬件逻辑模块中存储的预处理后的数据,对所述adc芯片的指标进行计算,将计算结果经过硬件逻辑模块转发给上位机。

11.优选地,所述adc芯片的指标包括无杂散动态范围sfdr、总谐波失真yhd、信纳比sinad、信噪比和有效位数。

12.优选地,所述软件模块与所述硬件逻辑模块之间通过axi总线相连。

13.优选地,所述硬件逻辑模块包括时钟分发模块、io传输模块、数据缓冲转换模块、自检信号产生模块、数据预处理模块和ram存储控制模块;

14.所述时钟分发模块将fpga外部时钟转换成内部时钟并分发内部时钟,所述时钟分

发模块将内部时钟分发给硬件逻辑模块中的其他模块;

15.所述io传输模块接收上位机下发的指令信息和所述软件模块发送的运算结果,并将计算出的adc芯片指标数据传输给上位机;

16.所述数据缓冲转换模块利用ibufds差分信号缓冲器和iddr单端双沿转换器将adc芯片输出的原始信号进行转换处理,与内部采样时钟进行同步,输出同步后的adc信号;

17.所述自检信号产生模块用于产生自检信号,用于对所述动态指标测量系统进行自检,对所述动态指标测量系统的输出adc指标进行校准;

18.所述数据预处理模块用于接收来自数据缓冲转换模块或自检信号产生模块的信号,并依据通过io传输模块设置的模式信息,将自检信号或adc芯片采集到的原始数据进行预处理,预处理包括定点数到浮点数的转换和fft处理;

19.所述ram存储控制模块用于将预处理后的数据存入ram,由所述adc芯片指标计算模块从ram中读取所述预处理后的数据,以进行adc芯片的指标的计算。

20.一种基于fpga的adc动态指标测量方法,所述方法基于如前所述系统,所述方法包括:

21.步骤s31:adc芯片将采集到的模拟信号转换成数字信号送入fpga,然后利用ibufds差分信号缓冲器和iddr单端双沿转换器进行初步转换处理;

22.步骤s32:上位机下发模式控制命令,对测量系统的工作模式进行选择,获取原始数据;所述工作模式包括测量模式、自检模式;在测量模式下原始数据来源于adc芯片,在自检模式下原始数据来源于自检模块产生的数据;

23.步骤s33:将选择的所述原始数据进行定点数到浮点数的处理;

24.步骤s34:将浮点型数据进行fft处理;

25.步骤s35:将完成fft处理的实部和虚部数据按照fft点数送入ram存储器,再向软件模块发送fft处理完成信号,通知所述软件模块读取ram中存储的数据并进行计算,所述软件模块完成指标计算后,再向ram存储控制模块发送计算完成信号,通知所述ram存储控制模块继续向ram中存储数据;

26.步骤s36:所述adc芯片指标计算模块按照adc指标的计算公式进行指标计算;

27.步骤s37:将计算完成的指标数据通过数据接口送入上位机,实现指标的动态显示。

28.有益效果:

29.本发明测量期间只需简单操作,即可实现对adc动态指标的测量和显示,能够有效缩短测量时间,测量精度高、准确率高。

附图说明

30.图1为现有技术的测量方法的流程示意图;

31.图2为本发明的基于fpga的adc动态指标测量系统结构示意图;

32.图3为本发明的基于fpga的adc动态指标测量方法流程示意图。

具体实施方式

33.下面结合附图和实施例,对本发明进行详细描述。

34.如图2所示,本发明使用fpga构建针对adc芯片的动态指标测量系统,在fpga上实现整个测量系统,adc芯片是被测量芯片。

35.所述基于fpga的adc芯片的动态指标测量系统,包括上位机、软件模块及硬件逻辑模块。

36.所述上位机用于下发指令信息,并对计算出的adc芯片指标进行动态显示;所述上位机通过外部传输接口与所述硬件逻辑模块进行交互。

37.所述软件模块接收所述硬件逻辑模块的处理结果数据,并将运算完成后的数据发送给所述硬件逻辑模块;所述软件模块用于配置adc芯片以及对adc的指标进行运算。

38.所述硬件逻辑模块接收所述上位机的控制信息、以及所述软件模块的运算结果,用于进行数据转发和数据预处理。

39.本实施例中,所述上位机将计算出的adc芯片指标结果进行动态显示,所述软件模块可以利用microblaze软核或arm硬核实现。

40.进一步地,所述指令信息包括但不限于自检指令、开始测量指令、adc通道选择指令。所述上位机还用于下发测量系统控制参数。

41.进一步地,所述软件模块包括adc芯片配置模块及adc芯片指标计算模块,所述adc芯片配置模块用于设置所述adc芯片的寄存器配置参数,以及控制所述adc芯片的工作模式,将配置参数经过硬件逻辑模块转发给adc芯片。所述adc芯片指标计算模块用于读取所述硬件逻辑模块中存储的预处理后的数据,对所述adc芯片的指标进行计算,将计算结果经过硬件逻辑模块转发给上位机。所述adc芯片的指标包括但不限于无杂散动态范围sfdr、总谐波失真yhd、信纳比sinad、信噪比和有效位数。

42.所述软件模块与所述硬件逻辑模块之间通过axi总线相连。

43.进一步地,所述硬件逻辑模块包括时钟分发模块、io传输模块、数据缓冲转换模块、自检信号产生模块、数据预处理模块和ram存储控制模块。所述硬件逻辑模块基于fpga的硬件逻辑资源实现。

44.所述时钟分发模块将fpga外部时钟转换成内部时钟并分发内部时钟,所述时钟分发模块将内部时钟分发给硬件逻辑模块中的其他模块。

45.所述io传输模块接收上位机下发的指令信息和所述软件模块发送的运算结果,并将计算出的adc芯片指标数据传输给上位机。

46.所述数据缓冲转换模块利用ibufds差分信号缓冲器和iddr单端双沿转换器将adc芯片输出的原始信号进行转换处理,与内部采样时钟进行同步,输出同步后的adc信号。

47.所述自检信号产生模块用于产生自检信号,用于对所述动态指标测量系统进行自检,对所述动态指标测量系统的输出adc指标进行校准。

48.所述数据预处理模块用于接收来自数据缓冲转换模块或自检信号产生模块的信号,并依据通过io传输模块设置的模式信息,将自检信号或adc芯片采集到的原始数据进行预处理,预处理包括定点数到浮点数的转换和fft处理。

49.所述ram存储控制模块用于将预处理后的数据存入ram,由所述adc芯片指标计算模块从ram中读取所述预处理后的数据,以进行adc芯片的指标的计算。

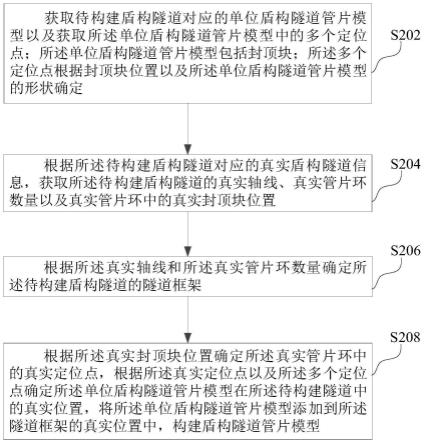

50.如图3所示,本发明提供一种基于fpga的adc动态指标测量方法,所述方法基于如前所述基于fpga的adc动态指标测量系统,所述方法包括:

51.步骤s31:adc芯片将采集到的模拟信号转换成数字信号送入fpga,然后利用ibufds差分信号缓冲器和iddr单端双沿转换器进行初步转换处理;

52.步骤s32:上位机下发模式控制命令,对测量系统的工作模式进行选择,获取原始数据;所述工作模式包括测量模式、自检模式;在测量模式下原始数据来源于adc芯片,在自检模式下原始数据来源于自检模块产生的数据;

53.步骤s33:将选择的所述原始数据进行定点数到浮点数的处理;

54.步骤s34:将浮点型数据进行fft处理;

55.步骤s35:将完成fft处理的实部和虚部数据按照fft点数送入ram存储器,再向软件模块发送fft处理完成信号,通知所述软件模块读取ram中存储的数据并进行计算,所述软件模块完成指标计算后,再向ram存储控制模块发送计算完成信号,通知所述ram存储控制模块继续向ram中存储数据;

56.步骤s36:所述adc芯片指标计算模块按照adc指标的计算公式进行指标计算;

57.步骤s37:将计算完成的指标数据通过数据接口送入上位机,实现指标的动态显示。

58.本实施例中,该adc动态指标测量方法可单独用于采集系统adc指标的测试,亦可作为完整采集系统fpga程序的一个模块来进行采集系统测量指标的实时监测。

59.通过对测量结果的分析,与原方法相比测量误差可接受。由此可以得出结论,在测量误差可接受的情况下,该adc指标测量方法可以有效缩短测量时间。

60.进一步地,系统为雷达信号采集系统,采用xc7k325t-2ffg900i型fpga为主控芯片,外部使用ad9467为采集adc芯片,具有pcie接口用于数据的传输。

61.以上的具体实施例仅描述了本发明的设计原理,该描述中的部件形状,名称可以不同,不受限制。所以,本发明领域的技术人员可以对前述实施例记载的技术方案进行修改或等同替换;而这些修改和替换未脱离本发明创造宗旨和技术方案,均应属于本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。