1.本发明涉及半导体技术领域,特别是涉及一种自对准成像工艺硬掩膜层刻蚀偏差的测量方法。

背景技术:

2.在finfet(鳍式晶体管)工艺中,首先是利用sadp(自对准双重成像技术)工艺定义整体的fin,继而通过平行于fin和垂直于fin的剪切层将多余的fin去除从而定义有源区。对于平行于fin的剪切层,理想的情况是将多余的整体的fin刻蚀掉的同时不损害到上下的fin。如图1,分别为整体的fin和经过剪切层定义出来的有源区,虚线标记区域为平行于fin的剪切层区域,临近剪切层边界的fin有明显的fin损伤。

3.从版图文件到得到最终的有源区中间经过opc(光学临近效应)修正、光刻工艺、刻蚀工艺,每个步骤都有可能造成fin损伤,其中,由于底层的三维结构,对于平行于fin的剪切层,刻蚀工艺结束后并不会在底层留下印记,因此无法直接对aei cd(刻蚀后关键尺寸测量)进行量测,无法得到刻蚀偏差及其对fin损害造成的影响,如图2所示,而将标记设计在大块有源区或者sti(浅沟槽隔离)上,并无法模拟芯片里真实的刻蚀行为。

技术实现要素:

4.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种自对准成像工艺硬掩膜层刻蚀偏差的测量方法,用于解决现有技术中由于底层的三维结构,对于平行于fin的剪切层,刻蚀工艺结束后并不会在底层留下印记,因此无法直接对显影后关键尺寸进行量测,无法得到刻蚀偏差及其对fin损害造成的影响,并无法模拟芯片里真实的刻蚀行为的问题。

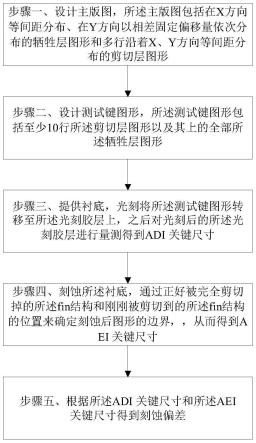

5.为实现上述目的及其他相关目的,本发明提供一种自对准成像工艺硬掩膜层刻蚀偏差的测量方法包括:

6.步骤一、设计主版图,所述主版图包括在x方向等间距分布、在y方向以相差固定偏移量依次分布的牺牲层图形和多行沿着x、y方向等间距分布的剪切层图形;

7.其中所述x方向为平行于所述主版图的方向,所述y方向垂直于所述x方向且平行于所述主版图;

8.每一行的多个所述牺牲层图形沿着y方向至少从与剪切层图形的上边缘齐平到与其下边界齐平;

9.每一列相邻的两个所述牺牲层图形在y方向的周期与所述剪切层图形的周期一致;

10.步骤二、设计测试键图形,所述测试键图形包括至少10行所述剪切层图形以及其上的全部所述牺牲层图形;

11.步骤三、提供衬底,所述衬底上形成有多个fin结构、覆盖多个所述fin结构的硬质掩膜层以及覆盖所述硬质掩膜层的牺牲层,之后在所述牺牲层上形成光刻胶层,光刻将所述测试键图形转移至所述光刻胶层上,之后对光刻后的所述光刻胶层进行量测得到adi关

键尺寸;

12.步骤四、刻蚀所述衬底,通过正好被完全剪切掉的所述fin结构和刚刚被剪切到的所述fin结构的位置来确定刻蚀后图形的边界,从而得到aei关键尺寸;

13.步骤五、根据所述adi关键尺寸和所述aei关键尺寸得到刻蚀偏差。

14.优选地,步骤一中的所述牺牲层图形的长度大于等于宽度的五倍。

15.优选地,步骤一中的所述固定偏移量为零,同一行的多个所述牺牲层图形合并。

16.优选地,步骤一中的所述固定偏移量为版图设计规则中最小格点的整数倍。

17.优选地,步骤二中的所述测试键图形设置于芯片内。

18.优选地,步骤三中的所述测试键图形设置于切割道上。

19.优选地,所述方法用来于表征sadp、saqp和saop工艺中的任何意一步剪切层工艺。

20.优选地,步骤三中采用sem量测或ocd量测得到所述adi关键尺寸。

21.优选地,步骤四中采用大场检测分析工具得到所述aei cd。

22.优选地,步骤四中的检测所述衬底包括所述fin结构的关键尺寸检测和缺陷检测。

23.优选地,所述saop工艺中刻蚀所述衬底的方法包括:

24.(1)以光刻后的所述光刻胶层为掩膜刻蚀所述牺牲层;

25.(2)去除所述光刻胶层;

26.(3)在刻蚀后的所述牺牲层的侧壁形成侧墙;

27.(4)去除剩余的所述牺牲层;

28.(5)以所述侧墙为掩膜刻蚀所述硬质掩膜层以及其下方的所述fin结构。

29.优选地,步骤三中的所述硬质掩膜层的材料为二氧化硅或氮化硅。

30.优选地,步骤三中的所述牺牲层材料为无定形硅。

31.优选地,步骤(3)中的所述侧墙的材料为二氧化硅或氮化硅。

32.如上所述,本发明的自对准成像工艺硬掩膜层刻蚀偏差的测量方法,具有以下有益效果:本发明通过测试键的设计可以准确地模拟真实的刻蚀fin结构层的刻蚀过程,使测试键的刻蚀行为与主版图一致;通过测试键的设计可以对落在三维fin结构上的剪切层的aei关键尺寸进行量测;通过大场检测工具对测试键进行整个芯片量测,减少随机因素的影响,准确地确定剪切层aei关键尺寸的边界,从而确定刻蚀偏差,为光学临近效应校正/光刻/刻蚀工艺的调整提供参考,提高工艺修正和调整的准确性,减少缺陷的产生。

附图说明

33.图1显示为现有技术刻蚀对fin的损伤示意图;

34.图2显示为现有技术衬底上标记示意图;

35.图3显示为本发明的测试键的整体设计示意图;

36.图4显示为本发明图3的局部放大示意图;

37.图5显示为本发明图4的局部放大示意图;

38.图6显示为本发明的工艺流程示意图。

具体实施方式

39.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书

所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

40.请参阅图6,本发明提供一种自对准成像工艺硬掩膜层刻蚀偏差的测量方法包括:

41.步骤一,请参阅图3至图5,设计主版图,主版图包括在x方向等间距分布、在y方向以相差固定偏移量依次分布的牺牲层图形20(mandrel)和多行沿着x、y方向等间距分布的剪切层图形10(cut layer);剪切层图形10(cut layer)用于定义出衬底上平行于fin结构和垂直于fin结构的剪切层的位置,将多余的fin去除,用以定义出有源区,在每一行剪切层图形10上均设置有多个牺牲层图形20(mandrel),全部牺牲层图形20在x方向等间距分布、在y方向以相差固定偏移量依次分布;

42.其中x方向为平行于主版图的方向,y方向垂直于x方向且平行于主版图;

43.每一行的多个牺牲层图形20沿着y方向至少从与剪切层图形10的上边缘齐平到与其下边界齐平;

44.每一列相邻的两个牺牲层图形20在y方向的间距与剪切层图形10的间距一致;

45.在一种可选的实施方案中,步骤一中的牺牲层图形20的长度大于等于宽度的五倍。

46.在一种可选的实施方案中,步骤一中的固定偏移量为零,同一行的多个牺牲层图形20合并,也就是说,每一行的剪切层图形10上有着在y方向以相差固定偏移量依次分布的一整个牺牲层图形20。

47.在一种可选的实施方案中,步骤一中的固定偏移量为版图设计规则中最小格点的整数倍。

48.步骤二,设计测试键图形,测试键图形包括至少10行剪切层图形10以及其上的全部牺牲层图形20,之后将该测试键图形放置于光罩上并进行出版,通过测试键的设计可以准确地模拟真实的刻蚀fin结构层的刻蚀过程,使测试键的刻蚀行为与主版图一致;

49.在一种可选的实施方案中,步骤二中的测试键图形设置于芯片版图内,在根据主版图完成芯片的制造后,根据测试键图形制造而成的测试键位于芯片的内部。

50.在一种可选的实施方案中,步骤三中的测试键图形设置于切割道版图上,在根据主版图完成芯片的制造后,根据测试键图形制造而成的测试键位于切割道上。

51.步骤三,提供衬底,衬底上形成有多个fin结构、覆盖多个fin结构的硬质掩膜层以及覆盖硬质掩膜层的牺牲层,通常情况下以cvd淀积牺牲层,之后在牺牲层上形成光刻胶层,光刻将测试键图形转移至光刻胶层上,用于定义出牺牲层被刻蚀的位置,之后对光刻后的光刻胶层进行量测得到adi cd(关键尺寸);

52.在一种可选的实施方案中,步骤三中采用sadp刻蚀衬底。

53.在一种可选的实施方案中,步骤三中采用sem量测或ocd量测得到adi关键尺寸。

54.优选地,方法用来于表征sadp(自对准双重成像技术)、saqp(自对准四重成像技术)和saop(自对准八重成像技术)工艺中的任何意一步剪切层工艺。

55.在一种可选的实施方案中,saop工艺刻蚀衬底的方法包括:

56.(1)以光刻后的光刻胶层为掩膜刻蚀牺牲层,被刻蚀后的牺牲层图形20被称为“mandrel”或“core";

57.(2)去除光刻胶层;

58.(3)在刻蚀后的牺牲层的侧壁形成侧墙,通常情况下以ald在刻蚀后的剩余牺牲层的表面和侧面沉积一层厚度相对比较均匀的薄膜,再通过回刻蚀在牺牲层的侧壁形成侧墙;

59.(4)使用选择性强的腐蚀液去除剩余的牺牲层;

60.(5)以侧墙为掩膜刻蚀硬质掩膜层以及其下方的fin结构。

61.在一种可选的实施方案中,步骤三中的硬质掩膜层的材料为二氧化硅或氮化硅。

62.在一种可选的实施方案中,步骤三中的牺牲层材料为非定形硅。

63.在一种可选的实施方案中,步骤(3)中的侧墙的材料为二氧化硅或氮化硅。

64.步骤四,刻蚀衬底,使得多个fin结构中的部分fin结构被完全刻蚀,另一部分fin结构被部分刻蚀,之后检测衬底,根据被完全刻蚀掉的fin结构的位置和刚刚被刻蚀到的fin结构的位置来确定刻蚀后图形的边界,从而得到aei cd;

65.优选地,步骤四中采用ep5、provision和anchor中等大场检测分析工具的任意一种得到aei cd。

66.优选地,步骤四中的检测衬底包括fin结构的关键尺寸检测和缺陷检测。

67.步骤五,根据adi cd和aei cd得到刻蚀偏差。

68.需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,遂图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

69.综上所述,本发明通过测试键的设计可以准确地模拟真实的刻蚀fin结构层的刻蚀过程,使测试键的刻蚀行为与主版图一致;通过测试键的设计可以对落在三维fin结构上的剪切层的aei cd进行量测;通过大场检测工具对测试键进行整个芯片量测,减少随机因素的影响,准确地确定剪切层aei cd的边界,从而确定刻蚀偏差,为光学临近效应校正/光刻/刻蚀工艺的调整提供参考,提高工艺修正和调整的准确性,减少缺陷的产生。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

70.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。