一种应用于spad的信号读取电路

技术领域

1.本发明涉及一种基于spad的信号读取电路,其能够实现对单光子信号的高效线性存储与读取。

背景技术:

2.近年来,固态数字图像传感器技术得到了飞速的发展。固态数字图像传感器技术目前主要包括电荷耦合器件技术(charge coupled device,简称ccd)和cmos图像传感器技术(cmos active pixel sensor,简称cmos-aps)。特别是进入二十一世纪以来,随着标准集成电路工艺向着纳米量级发展,cmos-aps技术得以获得更加升入的发展,在集成度、功耗以及成本上已经完全超越ccd,成为主流的消费品技术。

3.然而,随着微光成像技术、超高速成像技术以及量子光学技术的发展,传统的数字成像技术在成像速度和灵敏度上都遇到了巨大的挑战。在高速成像或微光条件下成像,由于曝光时间短,图像传感器所能够获得的光子信号非常微弱,而由于其本身的信噪比限制,造成传感器获得的图像不清晰。因此,如何进行微弱光信号的探测以及超高速成像,逐渐成为国内外研究的热点。

4.单光子雪崩二极管(single photon avalanche diode,简称spad)是一种工作在盖革模式(geiger mode)下的光电二极管,其灵敏度能够达到单个光子级别,并且其时间分辨率可达皮秒量级。spad兼具单光子灵敏度和皮秒分辨率两大特点,使其在微光探测和超高速成像领域得到了极大的关注,已经成为新的固态图像传感器研究热点技术。

5.如何将spad获得的高速信号及时准确的读出是现阶段急需解决的一个重要问题,读出电路的设计将直接影响到spad最终的探测质量。spad所输出的信号为一个脉冲信号,因此,传统的探测器通常都采用数字信号的读出方式,每个spad像素单元都配备一个读出电路,以及用来记录脉冲信号个数的高速计数器和锁存器等电路,所设计的电路方案可以保证最大限度的发挥spad高速探测这一特点。然而,由于每个像素都包含有一个庞大的电路模块,使得最终的单元像素面积过大,导致传感器的集成度不高,分辨率低。这也制约了spad作为成像传感器的像素分辨率性能。

技术实现要素:

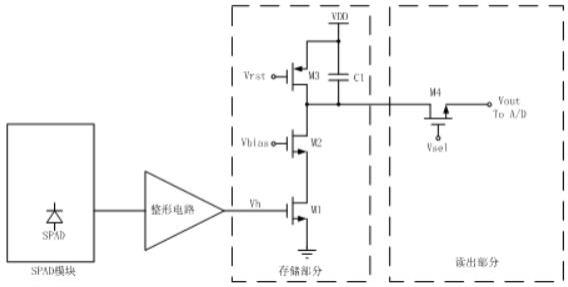

6.本发明提出了一种应用于spad的信号读取电路,其特点在于将spad所获得光信号以电压形式存储在电容器上,待一个探测周期结束后由读出电路统一读取,极大的增加了传感器的占空比,提高了像素集成度。

7.所述的应用于spad的信号读取电路,包括一个存储电路模块和一个读出电路模块,其结构示意图如图1所示。存储电路模块由一个电容和三个mos管组成,读出电路模块由一个选择mos管组成。具体的操作过程如下:(1)复位阶段:在进行光信号探测前,偏置vrst电压,使得mos管m3导通,偏置vbias电压,使得mos管m2关断,将电容cap充电至电源电压值vdd。

8.(2)光信号存储阶段:在复位阶段完成后,偏置vrst电压,使得mos管m3关断,偏置vbias电压,使得mos管m2导通,spad开始进行光电子探测。当spad探测到一个光子信号时,整形电路输出一个高电平脉冲信号vh,使得mos管m1导通,从而形成一个到地端的回路,对电容cap进行放电。当spad没有探测到光子信号时,整形电路输出低电平信号,mos管m1关断,电容放电回路被切断,维持现有电位。如此反复,spad每探测到一个光子信号,电容cap就进行一次放电,电容cap的最终端电位大小与spad所探测到的光子数成线性关系,此电位在复位之前将不会变化,相当于将光信号存储于cap之中。

9.(3)信号读出阶段:当spad完成一个周期的光信号探测后,偏置mos管m4电压vsel,使得mos管m4导通,最终的输出电压信号vout即为电容cap的终电位,从而实现对信号的读出。

10.所述的应用于spad的信号读取电路,能够将spad所探测到的光信号暂时存储于电容cap之中,无需计数器记录spad所探测到的光电子数目,从而增加了传感器阵列的占空比,提高集成度。

11.本发明的有益效益是:(1)集成度高:整个存储电路模块和信号读出模块仅有4个mos管和一个电容组成,能够有效减小单元像素尺寸,增加占空比,提高集成度。

12.(2)动态范围可调:根据实际spad应用,可通过改变电容值的大小,调节动态范围。

13.(3)便于阵列架构设计。所设计的存储电路模块的vrst、vbias电压可以由偏压产生电路同时施加相同的电压;读出电路包含一个选择管m4,可利用现有的成熟的cmos-aps成像传感器的阵列架构以及存储器的相关架构,为设计大规模成像传感器阵列提供了可能性。

附图说明

14.图1为本发明的单元像素的电路架构示意图。

15.图2为本发明电路架构的电路功能模拟仿真结果图。

16.图3位本发明提供的单光子雪崩二极管传感器的阵列架构示意图。

具体实施方式

17.以下结合附图对本发明创造作进一步的详细说明。

18.如图1所示,单光子雪崩二极管(spad)施加一个正向偏压vap,使spad工作于盖革模式下。

19.(1)复位阶段:在进行光信号探测前,偏置vrst电压,使得mos管m3导通,偏置vbias电压,使得mos管m2关断,将电容cap充电至电源电压值vdd。

20.(2)光信号存储阶段:偏置vrst电压,使得mos管m3关断,偏置vbias电压,使得mos管m2导通,spad开始进行光电子探测。当spad探测到一个光子信号时将发生雪崩,产生一个脉冲大电流,引起二极管上的电压变化,通过整形电路后输出一个高电平脉冲,将m1管导通,从而将电容一端接地,开始放电。整形电路输出的脉冲电压持续时间为t,m1管的导通电流i

int

大小可通过调节m2管的栅极电压vbias来控制。spad每探测到一个光子信号,电容cap就进行一次放电,电容cap的最终端电位大小与spad所探测到的光子数成线性关系,此电位

在复位之前将不会变化,相当于将光信号存储于cap之中。图2所示为本发明所用电路架构的模拟仿真结果图,由图可见,spad每探测到一个光子信号,整形电路输出端就输出一个脉冲电压,电容的端电位也随之降低。电容的端点位每次降低的值都是固定的,端电位的变化与spad所探测到的光子数目成正比关系,是一种标准的线性关系,便于最终光信号的读取。

21.(3)信号读出阶段:当spad完成一个周期的光信号探测后,偏置mos管m4电压vsel,使得mos管m4导通,最终的输出电压信号vout即为电容cap的终电位,从而实现对信号的读出。

22.一个光子引起的电容cap端点处的电压降为,c为电容cap的电容值,i

int

为mos管m2所控制的支路电流,其大小可由vbias控制,t为整形电路输出的脉冲电压持续时间,那么在一个探测周期时间内,假设有n

ph

个光子入射到探测器上,则电容端点处的电压降为。电容的端电压经过源极跟随器读出。

23.本发明所提出的应用于spad的信号读取电路,所用电路架构可大幅度减小单元像素的尺寸,增大占空比,利用所发明的电路架构可组成大规模传感器阵列,便于利用先进的标准集成电路工艺进行大规模的生产。图3所示为利用本发明电路架构组成的一个传感器阵列架构示意图。

24.本领域技术人员可以理解附图所示只是一个优先选择实施例的示意图,并不限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。