1.本发明实施例涉及一种半导体结构检查方法。

背景技术:

2.半导体集成电路技术已经历包含特征尺寸的持续最小化和封装密度的最大化的快速发展。特征尺寸最小化依赖于光刻的改进和打印较小特征或临界尺寸(critical dimension;cd)的相关联能力。随着临界尺寸大小持续减小,质量控制越来越多地用于保持产率和优化处理技术。可通过对缺陷和其它处理问题进行严格的晶片检查来促进对较小临界尺寸的质量控制。

技术实现要素:

3.本发明实施例提供一种半导体结构检查方法,包括:将高原子序数材料施加到晶片的半导体结构的一个或多个表面,其中所述一个或多个表面在与所述晶片的表面的深度不同的深度处;使电子束扫描遍及所述半导体结构,以使得在集电极处收集反向散射电子信号;以及基于所述集电极处的由所述高原子序数材料产生的所述反向散射电子信号的强度来产生所述半导体结构的轮廓扫描。

4.本发明实施例提供一种半导体结构检查方法,包括:将高原子序数材料施加到晶片的表面下方的半导体结构的一个或多个表面;使电子束扫描遍及所述半导体结构,以使得在集电极处收集来自所述半导体结构的反向散射电子信号;基于所述集电极处的由所述高原子序数材料产生的所述反向散射电子信号的强度来产生所述半导体结构的轮廓扫描;以及基于所述半导体结构的所述轮廓扫描来确定所述半导体结构的一个或多个临界尺寸测量。

5.本发明实施例提供一种半导体结构检查方法,包括:在晶片的表面之下形成半导体结构,其中所述半导体结构包含多个表面;在所述半导体结构的所述多个表面上方和在所述晶片的所述表面上方沉积膜,其中所述膜包含高原子序数材料;沉积材料以覆盖所述膜和所述半导体结构的所述多个表面;以及从所述晶片的所述表面去除所述材料和所述膜,其中所述膜保留在所述半导体结构的所述多个表面上方,以准许执行临界尺寸测量,从而确定所述半导体结构的轮廓。

附图说明

6.结合附图阅读以下详细描述会最佳地理解本公开的各方面。应注意,根据业界中的标准惯例,各个特征未按比例绘制。实际上,为了论述清楚起见,可任意增大或减小各个特征的尺寸。

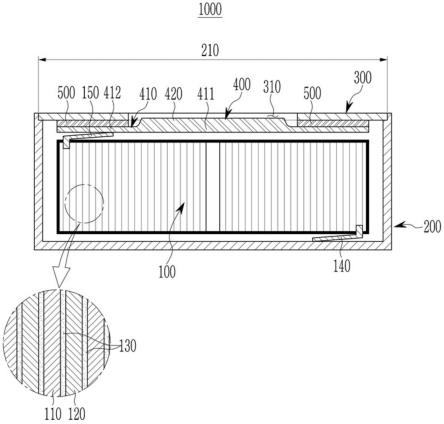

7.图1a到图1h是本文中所描述的一个或多个实例实施方案的图。

8.图2a到图2e是本文中所描述的一个或多个实例实施方案的图。

9.图3是可在其中实施本文中所描述的系统和/或方法的实例环境的图。

10.图4是图3的一个或多个装置的实例组件的图。

11.图5到图7是使用高原子序数材料进行半导体结构处理和/或检查的实例过程的流程图。

12.附图标号说明

13.100、200:实例实施方案;

14.102、202、312:晶片;

15.104、204、314:半导体结构;

16.106a、106b、206a、206b:侧表面;

17.108:底部表面;

18.110、210:表面;

19.112、212:高原子序数材料;

20.114:材料;

21.116、216:电子束;

22.118、218:反向散射电子;

23.120、220:半导体处理装置;

24.121、221:轮廓扫描;

25.122、222、304:电子显微镜;

26.124、224、310:扫描处理装置;

27.208:顶部表面;

28.300:环境;

29.302:半导体处理装置;

30.306:发射极;

31.308:集电极;

32.400:装置;

33.410:总线;

34.420:处理器;

35.430:存储器;

36.440:存储组件;

37.450:输入组件;

38.460:输出组件;

39.470:通信接口;

40.500、600、700:过程;

41.510、520、530、610、620、630、640、710、720、730、740:框。

具体实施方式

42.以下公开内容提供用于实施所提供主题的不同特征的许多不同实施方案或实例。下文描述组件和布置的具体实例以简化本公开。当然,这些组件和布置仅为实例且并不意图为限制性的。举例来说,在以下描述中,第一特征在第二特征上方或第二特征上的形成可包含第一特征与第二特征直接接触地形成的实施方案,且还可包含可在第一特征与第二特

征之间形成额外特征以使得第一特征与第二特征可不直接接触的实施方案。另外,本公开可在各种实例中重复附图标号和/或字母。此重复是出于简单和清楚的目的,且本身并不指示所论述的各种实施方案和/或配置之间的关系。

43.此外,为易于描述,可在本文中使用例如“在

…

之下(beneath)”、“在

…

下方(below)”、“下部(lower)”、“在

…

上方(above)”、“上部(upper)”等空间相对术语来描述如图式中所示出的一个元件或特征与另一(些)元件或特征的关系。除图式中所描绘的定向外,空间相对术语意图涵盖装置在使用或操作中的不同定向。设备可以其它方式定向(旋转90度或处于其它定向),且本文中所使用的空间相对描述词也可相应地解释。

44.可用于识别缺陷的一种技术包含使用电子显微镜来检查形成于晶片上的半导体结构。将晶片放置在真空腔室中,且电子显微镜将电子的电子束发射到晶片上。电子接触晶片的各种材料和其上的半导体结构,这使得材料的原子从电子束反向散射电子。反向散射电子形成在电子显微镜的集电极处收集的反向散射电子信号。当使电子束扫描遍及晶片时,计算机或另一类型的扫描处理装置从集电极接收反向散射电子信号,且基于反向散射电子信号的局部强度来产生晶片和半导体结构的二维或三维扫描或图像。可从所得扫描或图像测量半导体结构的临界尺寸以验证处理公差并识别缺陷。

45.虽然使用电子显微镜来识别半导体结构中的缺陷在半导体制造中提供许多益处,但当前处理技术中存在一些限制。举例来说,如果半导体结构的表面与晶片的表面之间的深度差过大,那么电子显微镜可能不能够产生具有足够对比度的半导体结构的扫描或图像来执行半导体结构的临界尺寸测量。这可能发生在例如半导体结构形成于晶片的表面之下或上方的情况下。半导体结构的表面与晶片的表面之间的深度差引起从半导体结构的表面产生的反向散射电子信号的信号强度,这转而在将要执行临界尺寸测量的区域中导致暗像(dark image)或低对比度。

46.根据本文所描述的一些实施方案,半导体结构可形成于晶片上,使得半导体结构的表面相对于晶片的表面的深度处于不同深度处。举例来说,半导体结构可形成于晶片的表面之下和/或上方。可进一步处理半导体结构以将高原子序数材料施加到半导体结构的表面上。与晶片和半导体结构的表面的材料相比,高原子序数材料由相对较大的原子构成。相对于晶片和半导体结构的表面的材料,高原子序数材料的较大原子更容易散射电子,从而相对于晶片和半导体结构的表面的材料产生更高强度的反向散射电子信号。相比于不使用高原子序数材料的情况,较高强度的反向散射电子信号在电子显微镜扫描或图像中产生增加的亮度和/或较高对比度。以这种方式,扫描或图像可用于更准确的临界尺寸测量,可用于晶片的表面之下和/或上方的半导体结构的临界尺寸测量,且可用于半导体结构的灰阶轮廓的分析以界定半导体结构的图案尺寸或轮廓。

47.图1a到图1h是本文中所描述的一个或多个实例实施方案100的图。如图1a到图1h中所示,实例实施方案100包含用于使用高原子序数材料处理并检查晶片102和形成于其中的半导体结构104的各种技术。

48.转向图1a,晶片102可包含由各种半导体材料、绝缘材料和/或导电材料形成的晶片。举例来说,晶片102可由结晶硅、例如砷化镓(gaas)或氮化镓(gan)的化合物iii族-v族半导体材料和/或其它材料形成。在一些实施方案中,晶片102可称作衬底或可在其上和/或其中形成半导体结构的另一结构。

49.如图1b中所示,半导体结构104可形成于晶片102中。半导体结构104可为例如晶体管的半导体装置;可为例如触点、晶体管栅极、源极或漏极的半导体装置的一部分;可为通孔,或可为另一类型的半导体结构。半导体结构104可由一个或多个表面构成。如图1b中所示,半导体结构104可包含多个表面:侧表面106a和侧表面106b以及底部表面108。半导体结构104可形成于晶片102的表面110(例如,顶部表面或外部表面)下方或之下。在这种情况下,表面106a、表面106b以及表面108可位于晶片102的表面110之下或下方,且因此相对于表面110的深度处于不同深度。虽然在实例实施方案100中将半导体结构104绘示为倒梯形形状,但可形成具有不同形状和/或不同数量和/或配置的表面的其它半导体结构104。

50.可使用各种半导体处理技术和半导体处理装置120形成半导体结构104,所述半导体处理技术例如从晶片102的表面110向下刻蚀到晶片102内的特定深度。举例来说,半导体处理装置120可形成、沉积、生长或以其它方式将光刻胶材料施加到晶片102的表面110,半导体处理装置120可暴露光刻胶以创建图案化光掩模,且半导体处理装置120可将表面110向下刻蚀到晶片102中以形成半导体结构104。可使用各种刻蚀技术,例如湿式或液体刻蚀、干式或等离子刻蚀和/或另一刻蚀技术。

51.如图1c中所示,半导体处理装置120可将高原子序数材料112施加到晶片102的至少一部分,使得半导体结构104的表面106a、表面106b以及表面108由高原子序数材料112涂布或覆盖。在一些实施方案中,半导体处理装置120将高原子序数材料112作为膜沉积到晶片102的至少一部分,使得膜沉积在半导体结构104的表面106a、表面106b以及表面108上。在一些实施方案中,半导体处理装置120经由外延或另一生长技术使高原子序数材料112在半导体结构104的表面106a、表面106b以及表面108上生长。在一些实施方案中,半导体处理装置120经由离子注入在半导体结构104的表面106a、表面106b以及表面108上创建高原子序数材料112。

52.高原子序数材料112可包含相对于晶片102的材料、表面110的材料和/或表面106a、表面106b以及表面108的材料具有较高或大体上较高原子序数的材料。实例高原子序数材料包含铪(或氧化铪)、镧(或氧化镧)、锆(或氧化锆)和/或与晶片102的材料、表面110的材料和/或表面106a、表面106b以及表面108的材料相比具有相对较大的原子的另一种材料。

53.半导体处理装置120可将高原子序数材料112施加到表面106a、表面106b以及表面108,使得高原子序数材料112的厚度大体上均一。高原子序数材料112的厚度的均一性可影响半导体结构104的临界尺寸测量。通过以均一方式施加高原子序数材料112,保留表面106a、表面106b以及表面108的特性,从而确保准确的临界尺寸测量。施加到表面106a、表面106b以及表面108的高原子序数材料112的实例厚度在近似1纳米(nanometer;nm)到近似2纳米的范围内。

54.如图1d中所示,半导体处理装置120可通过在半导体结构104中沉积材料114来回填半导体结构104,以覆盖高原子序数材料112和表面106a、表面106b以及表面108。材料114可包含介电材料、不导电材料或绝缘材料。材料114可包含相对于高原子序数材料112具有较低或大体上较低的原子序数的材料。

55.在一些情况下,高原子序数材料112和/或材料114可施加到晶片的表面110的至少一部分(例如,作为过程副产物)。在这些情况下,且如图1e中所示,半导体处理装置120可从

表面110去除高原子序数材料112和/或材料114。半导体处理装置120可使用各种材料去除技术,所述材料去除技术包含使用化学机械抛光来抛光表面110、使用平坦化技术来使表面110平坦化和/或其它材料去除技术。

56.在一些实施方案中,上文结合图1a到图1e示出和描述的处理步骤和/或技术用于形成半导体结构104和/或准备用于检查的半导体结构104。在一些实施方案中,与上文结合图1a到图1e示出和描述的处理步骤或技术相比,更多处理步骤或技术可用于形成半导体结构104和/或准备用于检查的半导体结构104。在一些实施方案中,与上文结合图1a到图1e描述的步骤或技术相比,不同步骤或技术可用于形成半导体结构104和/或准备用于检查的半导体结构104。

57.如图1f中所示,电子显微镜122可用于在已将高原子序数材料112施加到半导体结构104之后检查半导体结构104。为了检查半导体结构104,电子显微镜122可经由电子显微镜122的发射极产生并发射电子束116。电子束116包含引导到晶片102和半导体结构104处的初级电子的带电且聚焦的电子束。可将电子束116引导到晶片102所位于的真空腔室中,且引导到晶片102和半导体结构104上。

58.如进一步在图1f中所示,电子束116可接触表面110,表面106a、表面106b以及表面108上的高原子序数材料112以及材料114。电子束116可使得反向散射电子118从表面110,从表面106a、表面106b以及表面108上的高原子序数材料112,以及从材料114散射。反向散射电子118可形成在电子显微镜122的集电极处收集的反向散射电子信号(例如,电子射束或电子流)。如进一步在图1f中所示,相对于晶片102的材料和材料114,高原子序数材料112发射较高强度的反向散射电子信号(例如,发射更大数量和/或密度的反向散射电子118)。

59.如图1g中所示,可将在电子显微镜122的集电极处收集的反向散射电子信号提供给扫描处理装置124。扫描处理装置124可基于接收的反向散射电子信号来产生轮廓扫描121或图像。轮廓扫描121可为二维扫描或图像,或可为三维扫描或图像。

60.在一些实施方案中,扫描处理装置124在电子显微镜122扫描晶片102和半导体结构104时产生轮廓扫描121。电子显微镜122可以光栅图案或另一类型的扫描图案形式扫描晶片102和半导体结构104。扫描处理装置124可以类似方式产生轮廓扫描121。举例来说,扫描处理装置124可以与用于用电子束116扫描晶片102和半导体结构104的图案相同的图案形式产生轮廓扫描121。

61.扫描处理装置124可基于反向散射电子信号的信号强度来产生轮廓扫描121。举例来说,扫描处理装置124可基于晶片102或半导体结构104上的电子束116的对应位置处的反向散射电子信号的信号强度来确定轮廓扫描121的每一部分的亮度或强度。轮廓扫描121的间距(例如,轮廓扫描121的每一部分的大小,对于所述部分使用反向散射电子信号的唯一测量)可指示轮廓扫描121的粒度或清晰度。也就是说,轮廓扫描121的粒度或清晰度随着反向散射电子信号的更大数量的唯一测量用于产生轮廓扫描121而增加。

62.如进一步在图1g中所示,高原子序数材料112的使用增加晶片102的表面110与半导体结构104的表面之间的对比度。增加的对比度使得扫描处理装置124能够基于轮廓扫描121执行或确定半导体结构104的更准确的临界尺寸测量。如图1g中所示,实例临界尺寸测量包含测量半导体结构104的侧表面106a与侧表面106b之间的距离。半导体结构104的侧表面106a与侧表面106b之间的距离可对应于晶体管栅极的厚度或半导体结构104的另一类型

的临界尺寸测量。

63.如图1h中所示,扫描处理装置124可执行半导体结构104的多个临界尺寸测量,以确定半导体结构104的轮廓(例如,二维轮廓或三维轮廓)。扫描处理装置124可沿着半导体结构104的一个或多个方向或轴线执行多个临界尺寸测量,所述方向或轴线例如在从晶片102的顶部表面朝向晶片102的底部表面的方向上、在从晶片102的底部表面朝向晶片102的顶部表面的方向上、在从晶片102的第一侧表面朝向晶片102的第二侧表面的方向上、在从晶片102的第二侧表面朝向晶片102的第一侧表面的方向上、在相对于晶片102的顶部表面处于特定角度的方向上或相对于晶片102的底部表面处于特定角度的方向。以这种方式,半导体结构104的轮廓可用于分析半导体结构104沿着半导体结构104的一个或多个表面的均一性,可用于分析半导体结构104的一个或多个临界尺寸的均一性,和/或可用于分析半导体结构104的其它参数。

64.如图1h中的实例中所示出,扫描处理装置124可通过在晶片102中的半导体结构104的不同深度处执行临界尺寸测量来确定半导体结构104的轮廓。扫描处理装置124可基于电子束116的入射电子在深度处的着陆能量而在半导体结构104的特定深度处执行临界尺寸测量。举例来说,扫描处理装置124可基于电子束116的入射电子在第一深度处的着陆能量(电子束着陆能量1)而在晶片102中的半导体结构104的第一深度处执行第一临界尺寸测量(临界尺寸测量1),可基于电子束116的入射电子在第二深度处的着陆能量(电子束着陆能量2)而在晶片102中的半导体结构104的第二深度处执行第二临界尺寸测量(临界尺寸测量2),可基于电子束116的入射电子在第三深度处的着陆能量(电子束着陆能量3)而在晶片102中的半导体结构104的第三深度处执行第三临界尺寸测量(临界尺寸测量3)等。半导体装置104的不同深度处的着陆能量可用于获得半导体结构104的轮廓。扫描处理装置124可执行比图1h中所示出的更多或更少的临界尺寸测量,以确定半导体结构104的轮廓。

65.如上文所指示,提供图1a到图1h仅作为一个或多个实例。其它实例可不同于关于图1a到图1h所描述的实例。

66.图2a到图2e是本文中所描述的一个或多个实例实施方案200的图。如图2a到图2e中所示,实例实施方案200包含用于使用高原子序数材料处理并检查晶片202和形成于其中的半导体结构204的各种技术。

67.转向图2a,晶片202可包含由各种半导体材料、绝缘材料和/或导电材料形成的晶片。举例来说,晶片202可由结晶硅、例如gaas或gan的化合物iii-v族半导体材料和/或其它材料形成。在一些实施方案中,晶片202可称作衬底或可在其上和/或其中形成半导体结构的另一结构。

68.如图2b中所示,半导体结构204可形成于晶片202上。半导体结构204可为例如晶体管的半导体装置;可为例如触点、晶体管栅极、源极或漏极的半导体装置的一部分;可为通孔或另一类型的半导体结构。半导体结构204可由一个或多个表面构成。如图2b中所示,半导体结构204可包含多个表面:侧表面206a和侧表面206b以及顶部表面208。在图2b中所示出的实例中,半导体结构204形成于晶片202的表面210(例如,顶部表面或外部表面)上或上方。在此实例中,表面206a、表面206b以及表面208位于晶片202的表面210上方,且因此相对于表面210的深度处于不同深度。图2b将半导体结构204示出为呈现颈缩的大体矩形结构(例如,其中侧表面206a和侧表面206b的一部分由于半导体制造过程中的缺陷而逐渐变

窄)。虽然在实例实施方案200中将半导体结构204绘示为大体矩形形状,但可形成具有不同形状和/或不同数量和/或配置的表面的其它半导体结构204。

69.可使用各种半导体处理技术和半导体处理装置220形成半导体结构204,所述半导体处理技术例如从晶片202的表面210向下刻蚀到晶片202内的特定深度。举例来说,半导体处理装置220可形成、沉积、生长或以其它方式将光刻胶材料施加到晶片202的表面210,半导体处理装置220可暴露光刻胶以创建图案化光掩模,且半导体处理装置220可将表面210向下刻蚀到晶片202中以形成半导体结构204。特定来说,半导体处理装置220可围绕半导体结构204刻蚀表面210,使得半导体结构204从刻蚀过程保留,且使得表面210低于半导体结构204或在半导体结构204下方。可使用各种刻蚀技术,例如湿式或液体刻蚀、干式或等离子刻蚀和/或另一刻蚀技术。

70.如图2c中所示,半导体处理装置220可将高原子序数材料212施加到晶片202的至少一部分,使得半导体结构204的表面206a、表面206b以及表面208由高原子序数材料212涂布或覆盖。在一些实施方案中,半导体处理装置220将高原子序数材料212作为膜沉积到晶片202的至少一部分,使得膜沉积在半导体结构204的表面206a、表面206b以及表面208上。在一些实施方案中,半导体处理装置220经由外延或另一生长技术使高原子序数材料212在半导体结构204的表面206a、表面206b以及表面208上生长。在一些实施方案中,半导体处理装置220经由离子注入在半导体结构204的表面206a、表面206b以及表面208上创建高原子序数材料212。

71.高原子序数材料212可包含相对于晶片202的材料、表面210的材料和/或表面206a、表面206b以及表面208的材料具有较高或大体上较高原子序数的材料。实例高原子序数材料包含铪(或氧化铪)、镧(或氧化镧)、锆(或氧化锆)和/或与晶片202的材料、表面210的材料和/或表面206a、表面206b以及表面208的材料相比具有相对较大的原子的另一种材料。

72.半导体处理装置220可将高原子序数材料212施加到表面206a、表面206b以及表面208,使得高原子序数材料212的厚度大体上均一。高原子序数材料212的厚度的均一性可影响半导体结构204的临界尺寸测量。通过以均一方式施加高原子序数材料212,保留表面206a、表面206b以及表面208的特性,从而确保准确的临界尺寸测量。施加到表面206a、表面206b以及表面208的高原子序数材料212的实例厚度在近似1纳米(nm)到近似2纳米范围的内。

73.在一些实施方案中,上文结合图2a到图2c示出和描述的处理步骤和/或技术用于形成半导体结构204和/或准备用于检查的半导体结构204。在一些实施方案中,与上文结合图2a到图2c示出和描述的处理步骤或技术相比,更多处理步骤或技术可用于形成半导体结构204和/或准备用于检查的半导体结构204。在一些实施方案中,与上文结合图2a到图2c描述的步骤或技术相比,不同步骤或技术可用于形成半导体结构204和/或准备用于检查的半导体结构204。

74.如图2d中所示,电子显微镜222可用于在已将高原子序数材料212施加到半导体结构204之后检查半导体结构204。为了检查半导体结构204,电子显微镜222可经由电子显微镜222的发射极产生并发射电子束216。电子束216包含引导到晶片202和半导体结构204处的初级电子的带电且聚焦的电子束。可将电子束216引导到晶片202所位于的真空腔室中,

且引导到晶片202和半导体结构204上。

75.如进一步在图2d中所示,电子束216可接触表面210和表面206a、表面206b以及表面208上的高原子序数材料212。电子束216可使得反向散射电子218从表面210和表面206a、表面206b以及表面208上的高原子序数材料212发射。反向散射电子218可形成在电子显微镜222的集电极处收集的反向散射电子信号(例如,电子射束或电子流)。如进一步在图2d中所示,相对于晶片202和半导体结构204的材料,高原子序数材料212发射较高强度的反向散射电子信号(例如,发射更大数量和/或密度的反向散射电子218)。

76.如图2e中所示,可将在电子显微镜222的集电极处收集的反向散射电子信号提供给扫描处理装置224。扫描处理装置224可基于接收的反向散射电子信号来产生轮廓扫描221或图像。轮廓扫描221可为二维扫描或图像,或可为三维扫描或图像。

77.在一些实施方案中,扫描处理装置224在电子显微镜222扫描晶片202和半导体结构204时产生轮廓扫描221。电子显微镜222可以光栅图案或另一类型的扫描图案形式扫描晶片202和半导体结构204。扫描处理装置224可以类似方式产生轮廓扫描221。举例来说,扫描处理装置224可以与用于用电子束216扫描晶片202和半导体结构204的图案相同的图案形式产生轮廓扫描221。

78.扫描处理装置224可基于反向散射电子信号的信号强度来产生轮廓扫描221。举例来说,扫描处理装置224可基于晶片202或半导体结构204上的电子束216的对应位置处的反向散射电子信号的信号强度来确定轮廓扫描221的每一部分的亮度或强度。轮廓扫描221的间距(例如,轮廓扫描221的每一部分的大小,对于所述部分使用反向散射电子信号的唯一测量)可指示轮廓扫描221的粒度或清晰度。也就是说,轮廓扫描221的粒度或清晰度随着反向散射电子信号的更大数量的唯一测量用于产生轮廓扫描221而增加。

79.如进一步在图2e中所示,高原子序数材料212的使用增加晶片202的表面210与半导体结构204的表面之间的对比度。增加的对比度使得扫描处理装置224能够基于轮廓扫描221执行或确定半导体结构204的更准确的临界尺寸测量。如图2e中所示,实例临界尺寸测量包含测量半导体结构204的侧表面206a与侧表面206b之间的距离。

80.在一些实施方案中,扫描处理装置224执行半导体结构204的多个临界尺寸测量,以确定半导体结构204的轮廓。扫描处理装置224可沿着半导体结构204的一个或多个方向或轴线执行多个临界尺寸测量,所述方向或轴线例如在从晶片202的顶部表面朝向晶片202的底部表面的方向上、在从晶片202的底部表面朝向晶片202的顶部表面的方向上、在从晶片202的第一侧表面朝向晶片202的第二侧表面的方向上、在从晶片202的第二侧表面朝向晶片202的第一侧表面的方向上、在相对于晶片202的顶部表面处于特定角度的方向上或相对于晶片202的底部表面处于特定角度的方向。以这种方式,半导体结构204的轮廓可用于分析半导体结构204沿着半导体结构204的一个或多个表面的均一性,可用于分析半导体结构204的一个或多个临界尺寸的均一性,和/或可用于分析半导体结构204的其它参数。特定来说,半导体结构204的轮廓可用于确定半导体结构204中存在的颈缩量。

81.如上文所指示,提供图2a到图2e仅作为一个或多个实例。其它实例可不同于关于图2a到图2e所描述的实例。

82.图3是可在其中实施本文中所描述的系统和/或方法的实例环境300的图。如图3中所示,环境300可包含半导体处理装置302、包含发射极306和集电极308的电子显微镜304、

扫描处理装置310以及晶片312。环境300的一些装置和/或系统可经由有线连接、无线连接或有线连接和无线连接的组合内连。

83.半导体处理装置302包含能够使用各种半导体处理技术来处理晶片312以(例如,在晶片312上、在晶片312的表面上方、在晶片312的表面下方或之下、或其组合)形成半导体结构314的一个或多个装置。此外,半导体处理装置302包含能够在半导体结构314的表面上施加高原子序数材料以增加反向散射电子信号强度和/或以其它方式增强半导体结构314的电子显微镜检查的一个或多个装置。

84.半导体处理装置302可为独立的半导体处理装置,或可与其它半导体处理装置302一起包含于半导体处理系统中,以执行各种半导体处理技术,例如钝化技术、光刻技术、注入技术、刻蚀技术、沉积技术、抛光技术和/或其它技术中的一种或多种。举例来说,半导体处理装置302可包含表面钝化装置,或可包含于表面钝化系统、光刻胶或图案化装置(例如,旋转涂布装置)中,或可包含于光刻胶或图案化系统、步进机、深紫外曝光装置或极紫外曝光装置、湿式和/或干式(等离子)刻蚀装置、化学气相沉积装置、物理气相沉积装置、化学机械抛光装置和/或另一类型的半导体处理装置中。

85.电子显微镜304包含能够使用电子束扫描晶片312和/或形成于其上的一个或多个半导体结构314的一个或多个装置。举例来说,电子显微镜304可包含扫描电子显微镜、扫描透射电子显微镜、透射电子显微镜、反射电子显微镜和/或另一类型的电子显微镜。如图3中所示,电子显微镜304包含发射极306和集电极308。电子显微镜304可使用发射极306发射电子束,所述发射极306可称作电子枪或另一类型的电子束发射装置。在一些实施方案中,电子显微镜304可包含将电子束聚焦和/或引导到晶片312和/或半导体结构314上的一个或多个透镜和/或反光镜(未示出)。

86.在一些实施方案中,电子显微镜304用从发射极306发射的电子束来扫描晶片312和/或半导体结构314。为了扫描晶片312和/或半导体结构314,电子显微镜304可以光栅扫描图案或另一类型的扫描图案形式沿着晶片312和/或半导体结构314移动电子束。当电子显微镜304扫描晶片312和/或半导体结构314时,由于电子束与晶片312和/或半导体结构314的各种材料的原子的交互作用,从晶片312和/或半导体结构314发射包含多个反向散射电子的反向散射电子信号。电子显微镜304使用集电极308收集反向散射电子信号,所述集电极308可包含反向散射电子检测器或能够检测反向散射电子信号的另一类型的装置。

87.扫描处理装置310可包含台式计算机、笔记本电脑、服务器、云实施平台(cloud-implemented platform)和/或类似类型的装置。扫描处理装置310可与电子显微镜304通信连接,且可从集电极308接收反向散射电子信号的输出。在一些实施方案中,扫描处理装置310为独立的装置,且经由一个或多个通信接口、网络和/或其组合与电子显微镜304通信连接。在一些实施方案中,将扫描处理装置310集成到电子显微镜304中,使得扫描处理装置310和电子显微镜304是同一系统的一部分。

88.扫描处理装置310包含能够产生晶片312、半导体结构314或其部分的轮廓扫描或图像的一个或多个装置和/或系统。轮廓扫描或图像可为自上而下的二维轮廓扫描或图像,可为三维轮廓扫描或图像或另一类型的扫描和/或图像。扫描处理装置310基于在集电极308处接收的反向散射电子信号来产生半导体结构314的轮廓扫描或图像。举例来说,当电子显微镜304以图案形式使电子束沿着半导体结构314扫描时,扫描处理装置310可产生轮

廓扫描或图像的部分。轮廓扫描或图像的每一部分的亮度(且因此,轮廓扫描或图像的部分之间的对比度)可基于轮廓扫描或图像的部分的对应位置处的反向散射电子信号的强度(例如,反向散射电子信号中的电子的数量或密度)。在一些实施方案中,扫描处理装置310能够基于在集电极308处接收的反向散射电子信号来产生晶片312和/或半导体结构314的实况视频捕捉。

89.扫描处理装置310可更包含能够基于针对晶片312、半导体结构314或其部分产生的轮廓扫描或图像而执行或确定半导体结构314的一个或多个临界尺寸测量的一个或多个装置和/或系统。临界尺寸测量可包含厚度测量、深度测量、宽度测量、长度测量、距离测量和/或另一类型的测量。举例来说,扫描处理装置310可确定半导体装置的晶体管栅极的宽度。作为另一实例,扫描处理装置310可确定呈现颈缩的半导体结构314的厚度。在一些实施方案中,扫描处理装置310能够执行半导体结构314的多个临界尺寸测量,以确定半导体结构314的轮廓(例如,二维轮廓和/或三维轮廓)。

90.晶片312可包含由各种半导体材料、绝缘材料和/或导电材料形成的半导体晶片。可(例如,由一个或多个半导体处理装置302)处理晶片312,使得一个或多个半导体结构314形成于其上。在一些实施方案中,半导体结构314包含半导体装置,例如如晶体管(例如,finfet或其它类型的晶体管)、处理器、存储器装置、集成电路和/或另一类型的半导体装置。在一些实施方案中,半导体结构314包含半导体装置的一个或多个部分,例如栅极(例如,晶体管栅极)、源极、漏极和/或其它类型的半导体特征。

91.提供图3中所示的装置的数目和布置作为一个或多个实例。实际上,与图3中所示的装置相比,可存在额外装置、更少装置、不同装置或以不同方式布置的装置。此外,图3中所示的两个或大于两个装置可在单个装置内实施,或图3中所示的单个装置可实施为多个分布式装置。另外或替代地,环境300的装置的集合(例如,一个或多个装置)可执行描述为由环境300的装置的另一集合执行的一个或多个功能。

92.图4是装置400的实例组件的图。装置400可对应于半导体处理装置302、电子显微镜304、发射极306、集电极308和/或扫描处理装置310。在一些实施方案中,半导体处理装置302、电子显微镜304、发射极306、集电极308和/或扫描处理装置310可包含一个或多个装置400和/或装置400的一个或多个组件。如图4中所示,装置400可包含总线410、处理器420、存储器430、存储组件440、输入组件450、输出组件460以及通信接口470。

93.总线410包含准许在装置400的多个组件当中通信的组件。处理器420实施于硬件、固件和/或硬件与软件的组合中。处理器420为中央处理单元(central processing unit;cpu)、图形处理单元(graphics processing unit;gpu)、加速处理单元(accelerated processing unit;apu)、微处理器、微控制器、数字信号处理器(digital signal processor;dsp)、现场可编程门阵列(field-programmable gate array;fpga)、专用集成电路(application-specific integrated circuit;asic)或另一类型的处理组件。在一些实施方案中,处理器420包含能够编程成执行功能的一个或多个处理器。存储器430包含随机存取存储器(random access memory;ram)、只读存储器(read only memory;rom)和/或存储供处理器420使用的信息和/或指令的另一类型的动态或静态存储装置(例如,快闪存储器、磁性存储器和/或光学存储器)。

94.存储组件440存储与装置400的操作和使用相关的信息和/或软件。举例来说,存储

组件440可包含硬盘(例如,磁盘、光盘、和/或磁光盘)、固态驱动器(solid state drive;ssd)、压缩光盘(compact disc;cd)、数字多功能光盘(digital versatile disc;dvd)、软盘、盒带(cartridge)、磁带和/或另一类型的非暂时性计算机可读介质以及对应的驱动器。

95.输入组件450包含准许装置400例如经由用户输入(例如,触摸屏显示器、键盘、小键盘、鼠标、按钮、开关和/或麦克风)接收信息的组件。另外或替代地,输入组件450可包含用于确定位置的组件(例如,全球定位系统(global positioning system;gps)组件)和/或传感器(例如,加速计、陀螺仪、致动器或另一类型的方位或环境传感器)。输出组件460包含(经由例如显示器、扬声器、触觉反馈组件、音频或视觉指示器或另一类型的输出组件)提供来自装置400的输出信息的组件。

96.通信接口470包含使装置400能够例如经由有线连接、无线连接或有线连接和无线连接的组合与其它装置通信的收发器类组件(例如,收发器、单独的接收器、单独的发送器或另一类型的收发器类组件)。通信接口470可准许装置400自另一装置接收信息和/或向另一装置提供信息。举例来说,通信接口470可包含以太网接口、光接口(optical interface)、同轴接口(coaxial interface)、红外接口、射频(radio frequency;rf)接口、通用串行总线(universal serial bus;usb)接口、wi-fi接口、蜂窝网络接口或另一通信接口。

97.装置400可执行本文中所描述的一个或多个过程。装置400可基于处理器420执行由例如存储器430和/或存储组件440的非暂时性计算机可读介质所存储的软件指令来执行这些过程。如本文中所使用,术语“计算机可读介质”是指非暂时性存储器装置。存储器装置包含在单个物理存储装置内的存储器空间或跨多个物理存储装置散布的存储器空间。

98.软件指令可经由通信接口470从另一计算机可读介质或从另一装置读取到存储器430和/或存储组件440中。在执行时,存储在存储器430和/或存储组件440中的软件指令可使得处理器420执行本文中所描述的一个或多个过程。另外或替代地,可使用硬件电路代替或结合软件指令来执行本文中所描述的一个或多个过程。因此,本文中所描述的实施方案不限于硬件电路与软件的任何特定组合。

99.提供图4中绘示的组件的数目和布置作为实例。实际上,与图4中所示的组件相比,装置400可包含额外组件、更少组件、不同组件或以不同方式布置的组件。另外或替代地,装置400的组件的集合(例如,一个或多个组件)可执行描述为由装置400的组件的另一集合执行的一个或多个功能。

100.图5为使用高原子序数材料进行半导体结构检查的实例过程500的流程图。在一些实施方案中,图5的一个或多个过程框由一个或多个装置执行,所述一个或多个装置例如半导体处理装置(例如,半导体处理装置302)、电子显微镜(例如,电子显微镜304)、扫描处理装置(例如,扫描处理装置310)或另一装置。

101.如图5中所示,过程500可包含将高原子序数材料施加到晶片的半导体结构的一个或多个表面,其中一个或多个表面在与晶片的表面的深度不同的深度处(框510)。举例来说,如上文所描述,半导体处理装置(例如,使用处理器420、存储器430、存储组件440、输入组件450、输出组件460或通信接口470以及其它实例组件)可将高原子序数材料(例如,高原子序数材料112、高原子序数材料212)施加到晶片(例如,晶片102、晶片202)的半导体结构(例如,半导体结构104、半导体结构204等)的一个或多个表面(例如,表面106a、表面106b

和/或表面108、表面206a、表面206b和/或表面208)。在一些实施方案中,一个或多个表面在与晶片的表面(例如,表面110、表面210)的深度不同的深度处。

102.如进一步在图5中所示,过程500可包含使电子束扫描遍及半导体结构以使得在集电极处收集反向散射电子信号(框520)。举例来说,如上文所描述,电子显微镜(例如,使用发射极306、集电极308、处理器420、存储器430、存储组件440、输入组件450、输出组件460或通信接口470以及其它实例组件)可使电子束(例如,电子束116、电子束216)扫描遍及半导体结构,以使得在集电极(例如,集电极308)处收集多个反向散射电子(例如,反向散射电子118、反向散射电子218等)的反向散射电子信号。在一些实施方案中,从电子显微镜的发射极(例如,发射极306)发射电子束。

103.如进一步在图5中所示,过程500可包含基于集电极处的由高原子序数材料产生的反向散射电子信号的强度来产生半导体结构的轮廓扫描(框530)。举例来说,如上文所描述,扫描处理装置(例如,使用处理器420、存储器430、存储组件440、输入组件450、输出组件460或通信接口470以及其它实例组件)可基于集电极处的由高原子序数材料产生的反向散射电子信号的强度来产生半导体结构的轮廓扫描(例如,轮廓扫描121、轮廓扫描221)。

104.过程500可包含额外实施方案,例如下文所描述的和/或结合本文中其它地方所描述的一个或多个其它过程的任何单个实施方案或实施方案的任何组合。

105.在第一实施方案中,高原子序数材料为铪。在第二实施方案中,单独地或与第一实施方案组合,半导体结构的一个或多个表面在晶片的表面下方。在第三实施方案中,单独地或与第一实施方案和第二实施方案中的一个或多个组合,半导体结构的一个或多个表面在晶片的表面上方。在第四实施方案中,单独地或与第一实施方案到第三实施方案中的一个或多个组合,将高原子序数材料施加到晶片的半导体结构的一个或多个表面包含将高原子序数材料作为膜沉积在半导体结构的一个或多个表面上。

106.在第五实施方案中,单独地或与第一实施方案到第四实施方案中的一个或多个组合,将高原子序数材料施加到晶片的半导体结构的一个或多个表面包含将高原子序数材料施加到半导体结构的一个或多个侧表面以及将高原子序数材料施加到半导体结构的底部表面。在第六实施方案中,单独地或与第一实施方案到第五实施方案中的一个或多个组合,将高原子序数材料施加到晶片的半导体结构的一个或多个表面包含将高原子序数材料施加到半导体结构的一个或多个侧表面以及将高原子序数材料施加到半导体结构的顶部表面。

107.虽然图5绘示过程500的实例框,但在一些实施方案中,与图5中所描绘的框相比,过程500可包含额外框、更少框、不同框或以不同方式布置的框。另外或替代地,可并行地执行过程500的框中的两个或大于两个。

108.图6为使用高原子序数材料进行半导体结构检查的实例过程600的流程图。在一些实施方案中,图6的一个或多个过程框由一个或多个装置执行,所述一个或多个装置例如半导体处理装置(例如,半导体处理装置302)、电子显微镜(例如,电子显微镜304)、扫描处理装置(例如,扫描处理装置310)和/或另一装置。

109.如图6中所示,过程600可包含将高原子序数材料施加到晶片的表面下方的半导体结构的一个或多个表面(框610)。举例来说,如上文所描述,半导体处理装置(例如,使用处理器420、存储器430、存储组件440、输入组件450、输出组件460或通信接口470以及其它实

例组件)可将高原子序数材料(例如,高原子序数材料112、高原子序数材料212)施加到晶片(例如,晶片102、晶片202)的表面(例如,表面110、表面210)下方的半导体结构(例如,半导体结构104、半导体结构204)的一个或多个表面(例如,表面106a、表面106b和/或表面108、表面206a、表面206b和/或表面208)。

110.如进一步在图6中所示,过程600可包含使电子束扫描遍及半导体结构以使得在集电极处收集来自半导体结构的反向散射电子信号(框620)。举例来说,如上文所描述,电子显微镜(例如,使用发射极306、集电极308、处理器420、存储器430、存储组件440、输入组件450、输出组件460或通信接口470以及其它实例组件)可使电子束(例如,电子束116、电子束216等)扫描遍及半导体结构,以使得在集电极(例如,集电极308)处收集来自半导体结构的多个反向散射电子(例如,反向散射电子118、反向散射电子218等)的反向散射电子信号。在一些实施方案中,从电子显微镜的发射极(例如,发射极306)发射电子束。

111.如进一步在图6中所示,过程600可包含基于集电极处的由高原子序数材料产生的反向散射电子信号的强度来产生半导体结构的轮廓扫描(框630)。举例来说,如上文所描述,扫描处理装置(例如,使用处理器420、存储器430、存储组件440、输入组件450、输出组件460或通信接口470以及其它实例组件)可基于集电极处的由高原子序数材料产生的反向散射电子信号的强度来产生半导体结构的轮廓扫描(例如,轮廓扫描121、轮廓扫描221)。

112.如进一步在图6中所示,过程600可包含基于半导体结构的轮廓扫描来确定半导体结构的一个或多个临界尺寸测量(框640)。举例来说,如上文所描述,扫描处理装置(例如,使用处理器420、存储器430、存储组件440、输入组件450、输出组件460或通信接口470以及其它实例组件)可基于半导体结构的轮廓扫描来确定半导体结构的一个或多个临界尺寸测量。

113.过程600可包含额外实施方案,例如下文所描述的和/或结合本文中其它地方所描述的一个或多个其它过程的任何单个实施方案或实施方案的任何组合。

114.在第一实施方案中,高原子序数材料的原子序数相对于半导体结构的材料的原子序数更大。在第二实施方案中,单独地或与第一实施方案组合,高原子序数材料为铪。在第三实施方案中,单独地或与第一实施方案及第二实施方案中的一个或多个组合,高原子序数材料为镧。在第四实施方案中,单独地或与第一实施方案到第三实施方案中的一个或多个组合,半导体结构为倒梯形结构。

115.在第五实施方案中,单独地或与第一实施方案到第四实施方案中的一个或多个组合,确定半导体结构的一个或多个临界尺寸测量包含确定晶片的表面下方的半导体结构的不同深度处的相应临界尺寸测量。在第六实施方案中,单独地或与第一实施方案到第五实施方案中的一个或多个组合,确定半导体结构的不同深度处的相应临界尺寸测量包含基于电子束的入射电子在半导体结构的第一深度处的着陆能量来确定在第一深度处的第一临界尺寸测量以及基于电子束的入射电子在半导体结构的第二深度处的着陆能量来确定在第二深度处的第二临界尺寸测量。

116.虽然图6绘示过程600的实例框,但在一些实施方案中,与图6中所描绘的框相比,过程600可包含额外框、更少框、不同框或以不同方式布置的框。另外或替代地,可并行地执行过程600的框中的两个或大于两个。

117.图7为使用高原子序数材料处理用于检查的半导体结构的实例过程700的流程图。

在一些实施方案中,图7的一个或多个过程框由半导体处理装置(例如,半导体处理装置302)执行。在一些实施方案中,一个或多个步骤过程700可由除半导体处理装置外的一个或多个装置执行,所述一个或多个装置例如电子显微镜(例如,电子显微镜304)、扫描处理装置(例如,扫描处理装置310)和/或另一装置。

118.如图7中所示,过程700可包含在晶片的表面之下形成半导体结构,其中半导体结构包含多个表面(框710)。举例来说,如上文所描述,半导体处理装置(例如,使用处理器420、存储器430、存储组件440、输入组件450、输出组件460或通信接口470以及其它实例组件)可在晶片(例如,晶片102、晶片202)的表面(例如,表面110、表面210)之下形成半导体结构(例如,半导体结构104、半导体结构204)。在一些实施方案中,半导体结构包含多个表面(例如,表面106a、表面106b和/或表面108、表面206a、表面206b和/或表面208)。

119.如进一步在图7中所示,过程700可包含在半导体结构的多个表面上方和在晶片的表面上方沉积膜,其中膜包含高原子序数材料(框720)。举例来说,如上文所描述,半导体处理装置(例如,使用发射极306、集电极308、处理器420、存储器430、存储组件440、输入组件450、输出组件460或通信接口470以及其它实例组件)可在半导体结构的多个表面上方和在晶片的表面上方沉积膜。在一些实施方案中,膜包含高原子序数材料(例如,高原子序数材料112、高原子序数材料212)。

120.如进一步在图7中所示,过程700可包含沉积材料以覆盖膜和半导体结构的多个表面(框730)。举例来说,如上文所描述,半导体处理装置(例如,使用处理器420、存储器430、存储组件440、输入组件450、输出组件460或通信接口470以及其它实例组件)可沉积材料(例如,材料144)以覆盖膜和半导体结构的多个表面。

121.如进一步在图7中所示,过程700可包含从晶片的表面去除材料和膜,其中膜保留在半导体结构的多个表面上方,以准许执行临界尺寸测量,从而确定半导体结构的轮廓(框740)。举例来说,如上文所描述,半导体处理装置(例如,使用处理器420、存储器430、存储组件440、输入组件450、输出组件460或通信接口470以及其它实例组件)可从晶片的表面去除材料和膜。在一些实施方案中,膜保留在半导体结构的多个表面上方,以准许执行临界尺寸测量,从而确定半导体结构的轮廓。

122.过程700可包含额外实施方案,例如下文所描述的和/或结合本文中其它地方所描述的一个或多个其它过程的任何单个实施方案或实施方案的任何组合。

123.在第一实施方案中,过程700包含使用扫描电子显微镜检查半导体结构以产生半导体结构的图像,其中膜在图像中增加晶片的表面与半导体结构的多个表面之间的对比度。在第二实施方案中,单独地或与第一实施方案组合,过程700包含基于图像来执行半导体结构的临界尺寸测量。在第三实施方案中,单独地或与第一实施方案及第二实施方案中的一个或多个组合,执行半导体结构的临界尺寸测量包含在晶片的不同深度处执行半导体结构的多个临界尺寸测量以确定半导体结构的轮廓以及对晶片的不同深度使用不同的着陆能量来确定半导体结构的轮廓。

124.在第四实施方案中,单独地或与第一实施方案到第三实施方案中的一个或多个组合,半导体结构为晶体管栅极结构,且执行半导体结构的临界尺寸测量包含基于图像来确定晶体管栅极结构的宽度。在第五实施方案中,单独地或与第一实施方案到第四实施方案中的一个或多个组合,在半导体结构的多个表面上方沉积膜包含在半导体结构的多个表面

上方以几乎均一的厚度来沉积膜。

125.虽然图7绘示过程700的实例框,但在一些实施方案中,与图7中所描绘的框相比,过程700可包含额外框、更少框、不同框或以不同方式布置的框。另外或替代地,可并行地执行过程700的框中的两个或大于两个。

126.以这种方式,半导体结构形成于晶片上,使得半导体结构的表面相对于晶片的表面的深度处于不同深度。举例来说,半导体结构可形成于晶片的表面之下、晶片的表面上方,或部分形成于晶片的表面上方且部分形成于晶片的表面下方。进一步处理半导体结构以在半导体结构的表面上施加高原子序数材料。与晶片和半导体结构的表面的材料相比,高原子序数材料由相对较大的原子构成。相对于晶片和半导体结构的表面的材料,高原子序数材料的较大原子更容易散射电子,从而相对于晶片和半导体结构的表面的材料产生更高强度的反向散射电子信号。相比于不使用高原子序数材料的情况,较高强度的反向散射电子信号在电子显微镜扫描或图像中产生增加的亮度和/或较高对比度。以这种方式,扫描或图像可用于更准确的临界尺寸测量,可用于晶片的表面之下和/或上方的半导体结构的临界尺寸测量,和/或可用于半导体结构的灰阶轮廓的分析以界定图案尺寸。

127.如上文更详细地描述,本文中所描述的一些实施方案提供一种半导体结构检查方法。所述半导体结构检查方法包含将高原子序数材料施加到晶片的半导体结构的一个或多个表面。一个或多个表面在与晶片的表面的深度不同的深度处。所述半导体结构检查方法包含使电子束扫描遍及半导体结构以使得在集电极处收集反向散射电子信号。所述半导体结构检查方法包含基于集电极处的由高原子序数材料产生的反向散射电子信号的强度来产生半导体结构的轮廓扫描。

128.在一些实施例中,所述高原子序数材料为铪。在一些实施例中,所述半导体结构的所述一个或多个表面在所述晶片的所述表面下方。在一些实施例中,所述半导体结构的所述一个或多个表面在所述晶片的所述表面上方。在一些实施例中,将所述高原子序数材料施加到所述晶片的所述半导体结构的所述一个或多个表面包括:将所述高原子序数材料作为膜沉积在所述半导体结构的所述一个或多个表面上。在一些实施例中,将所述高原子序数材料施加到所述晶片的所述半导体结构的所述一个或多个表面包括:将所述高原子序数材料施加到所述半导体结构的一个或多个侧表面,以及将所述高原子序数材料施加到所述半导体结构的底部表面。在一些实施例中,将所述高原子序数材料施加到所述晶片的所述半导体结构的所述一个或多个表面包括:将所述高原子序数材料施加到所述半导体结构的一个或多个侧表面,以及将所述高原子序数材料施加到所述半导体结构的顶部表面。

129.如上文更详细地描述,本文中所描述的一些实施方案提供一种半导体结构检查方法。所述半导体结构检查方法包含将高原子序数材料施加到晶片的表面下方的半导体结构的一个或多个表面。所述半导体结构检查方法包含使电子束扫描遍及半导体结构以使得在集电极处收集来自半导体结构的反向散射电子信号。所述半导体结构检查方法包含基于集电极处的由高原子序数材料产生的反向散射电子信号的强度来产生半导体结构的轮廓扫描。所述半导体结构检查方法包含基于半导体结构的轮廓扫描来确定半导体结构的一个或多个临界尺寸测量。

130.在一些实施例中,所述高原子序数材料的原子序数相对于所述半导体结构的材料的原子序数更大。在一些实施例中,所述高原子序数材料为铪。在一些实施例中,所述高原

子序数材料为镧。在一些实施例中,所述半导体结构为倒梯形结构。在一些实施例中,确定所述半导体结构的一个或多个临界尺寸测量包括:确定所述晶片的所述表面下方的所述半导体结构的不同深度处的相应临界尺寸测量。在一些实施例中,确定所述半导体结构的所述不同深度处的所述相应临界尺寸测量包括:基于所述电子束的入射电子在所述半导体结构的第一深度处的着陆能量来确定在所述第一深度处的第一临界尺寸测量;以及基于所述电子束的入射电子在所述半导体结构的第二深度处的着陆能量来确定在所述第二深度处的第二临界尺寸测量。

131.如上文更详细地描述,本文中所描述的一些实施方案提供一种半导体结构检查方法。所述半导体结构检查方法包含在晶片的表面之下形成半导体结构。半导体结构包含多个表面。所述半导体结构检查方法包含在半导体结构的多个表面上方和在晶片的表面上方沉积膜。膜包含高原子序数材料。所述半导体结构检查方法包含沉积材料以覆盖膜和半导体结构的多个表面。所述半导体结构检查方法包含从晶片的表面去除材料和膜。膜保留在半导体结构的多个表面上方,以准许执行临界尺寸测量,从而确定半导体结构的轮廓。

132.在一些实施例中,半导体结构检查方法更包括:使用扫描电子显微镜检查所述半导体结构,以产生所述半导体结构的图像,其中所述膜在所述图像中增加所述晶片的所述表面与所述半导体结构的所述多个表面之间的对比度。在一些实施例中,半导体结构检查方法更包括:基于所述图像来执行所述半导体结构的所述临界尺寸测量。在一些实施例中,执行所述半导体结构的所述临界尺寸测量包括:在所述晶片的不同深度处执行所述半导体结构的多个临界尺寸测量;以及对所述晶片的所述不同深度使用不同的着陆能量来确定所述半导体结构的所述轮廓。在一些实施例中,所述半导体结构为晶体管栅极结构;以及其中执行所述半导体结构的所述临界尺寸测量包括:基于所述图像来确定所述晶体管栅极结构的宽度。在一些实施例中,在所述半导体结构的所述多个表面上方沉积所述膜包括:在所述半导体结构的所述多个表面上方以大体上均一的厚度沉积所述膜。

133.前文概述若干实施例的特征,使得本领域的技术人员可更好地理解本公开的各方面。本领域的技术人员应了解,其可易于使用本公开作为设计或修改用于实行本文中引入的实施方案的相同目的和/或实现相同优势的其它过程和结构的基础。本领域的技术人员还应认识到,此类等效构造并不脱离本公开的精神和范围,且本领域的技术人员可在不脱离本公开的精神和范围的情况下在本文中进行各种改变、替代以及更改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。