1.本发明涉及一种半导体装置。

背景技术:

2.以往,已知有如下技术:在将绝缘栅双极型晶体管(igbt)等晶体管部与二极管部形成于同一基板而得的半导体装置中,向半导体基板的预定深度位置照射氦离子等粒子束,设置包含寿命控制剂的寿命控制区。另外,为了抑制来自晶体管部的载流子增大,寿命控制区从二极管部起遍及到相邻的晶体管部的区域的一部分而设置。(例如,专利文献1和专利文献2)。

3.专利文献1:日本特开2017-135339号公报

4.专利文献2:日本特开2014-175517号公报

技术实现要素:

5.技术问题

6.在这样的半导体装置中,因为向晶体管部照射寿命控制剂,所以对栅极氧化膜造成损伤而引起阈值电压的降低。由于因阈值电压的降低而引起电流集中,所以存在过电流动作时因关断而引起闩锁并破坏这样的问题。

7.技术方案

8.在本发明的第一方式中,提供半导体装置。半导体装置具备半导体基板,该半导体基板具有晶体管部和二极管部,半导体基板具有设置于内部的第一导电型的漂移区,晶体管部具有:晶体管区,在俯视半导体基板时,其与二极管部分开设置;以及边界区,在俯视半导体基板时,其位于晶体管区与二极管部之间,并且在漂移区中,在半导体基板的正面侧具有寿命控制区,边界区具有电流抑制结构。

9.晶体管部可以还具有从半导体基板的正面起设置到漂移区为止的至少一个栅极沟槽部和至少一个虚设沟槽部,在边界区中,虚设比率可以大于1,所述虚设比率是虚设沟槽部的数量相对于栅极沟槽部的数量的比率。

10.边界区中的虚设比率可以高于晶体管区中的虚设比率。

11.边界区中的虚设比率可以是晶体管区中的虚设比率的1倍以上且9倍以下。

12.晶体管部可以在半导体基板的正面还具有第一导电型的发射区,边界区中的发射区的比率可以低于晶体管区中的发射区的比率。

13.在俯视半导体基板时,边界区的在晶体管部和二极管部的排列方向上的宽度可以是50μm以上且150μm以下。

14.边界区的宽度可以是100μm以上。

15.在俯视半导体基板时,边界区的面积可以是晶体管区的面积的3倍以上。

16.寿命控制区可以包含掺杂浓度为1

×e10

cm-3

以上且1

×e13

cm-3

以下的寿命控制剂。

17.在漂移区中,可以在半导体基板的背面侧以遍及整个晶体管部和整个二极管部的

方式还设置有寿命控制区。

18.应予说明,上述发明内容并没有列举本发明的全部必要特征。另外,这些特征组的子组合也能够另外成为发明。

附图说明

19.图1a是实施例一的半导体装置100的局部俯视图。

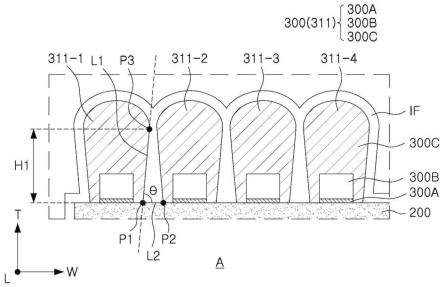

20.图1b是示出图1a中的a-a'截面的图。

21.图1c是实施例一的半导体装置100的局部俯视图。

22.图1d是实施例一的半导体装置100的局部俯视图。

23.图1e是实施例一的半导体装置100的局部俯视图。

24.图2是示出栅极电压vge与电流之间的关系的图表。

25.图3是实施例二的半导体装置200的局部俯视图。

26.符号说明

27.10

···

基板、11

···

阱区、12

···

发射区、14

···

基区、15

···

抽出区、16

···

蓄积区、17

···

插塞区、18

···

漂移区、20

···

缓冲区、21

···

正面、22

···

集电区、23

···

背面、24

···

集电极、25

···

连接部、29

···

直线部分、30

···

虚设沟槽部、31

···

前端部、32

···

虚设绝缘膜、34

···

虚设导电部、38

···

层间绝缘膜、39

···

直线部分、40

···

栅极沟槽部、41

···

前端部、42

···

栅极绝缘膜、44

···

栅极导电部、48

···

栅极流道、49

···

接触孔、50

···

栅极金属层、52

···

发射极、54

···

接触孔、56

···

接触孔、58

···

接触孔、60

···

台面部、61

···

台面部、70

···

晶体管部、72

···

晶体管区、74

···

边界区、80

···

二极管部、82

···

阴极区、85

···

寿命控制区、86

···

寿命控制区、100

···

半导体装置、200

···

半导体装置

具体实施方式

28.以下,虽然通过发明的实施方式对本发明进行说明,但是以下的实施方式并不限定权利要求所涉及的发明。另外,实施方式中所说明的特征的全部组合未必是发明的技术方案所必须的。

29.在本说明书中,将与半导体基板的深度方向平行的方向上的一侧称为“上”,将另一侧称为“下”。在基板、层或其他部件的两个主表面之中,将一个表面称为正面,将另一个表面称为背面。“上”、“下”的方向不限于重力方向或半导体装置实际安装时的方向。

30.在本说明书中,有时使用x轴、y轴以及z轴的直角坐标轴来说明技术事项。直角坐标轴只不过确定构成要素的相对位置,并不限定特定的方向。例如,z轴并不限定表示相对于地面的高度方向。应予说明, z轴方向与-z轴方向是彼此相反的方向。在不记载正负而记载为z轴方向的情况下,是指与 z轴和z轴平行的方向。

31.在本说明书中,将与半导体基板的正面和背面平行的正交轴设为x轴和y轴。另外,将与半导体基板的正面和背面垂直的轴设为z轴。在本说明书中,有时将z轴的方向称为深度方向。另外,在本说明书中,有时将包括x轴和y轴并与半导体基板的正面和背面平行的方向称为水平方向。

32.在本说明书中,在称为“相同”或者“相等”的情况下,也可以包括具有因制造偏差等引起的误差的情况。该误差例如在10%以内。

33.在本说明书中,将掺杂有杂质的掺杂区域的导电型设为p型或n型而进行说明。在本说明书中,杂质有时特别指n型的施主或p型的受主中的任一者,有时记载为掺杂剂。在本说明书中,掺杂是指向半导体基板导入施主或受主,将其设为表示n型的导电型的半导体或表示p型的导电型的半导体。

34.在本说明书中,掺杂浓度是指热平衡状态下的施主的浓度或受主的浓度。在本说明书中,净掺杂浓度是指在将施主浓度作为正离子的浓度并将受主浓度作为负离子的浓度时,包含电荷的极性相加而得的实质的浓度。作为一例,若将施主浓度设为nd,并将受主浓度设为na,则任意位置处的实质的净掺杂浓度为n

d-na。

35.施主具有向半导体供给电子的功能。受主具有从半导体获取电子的功能。施主和受主不限于杂质本身。例如,存在于半导体中的空位(v)、氧(o)以及氢(h)结合而成的voh缺陷作为供给电子的施主而起作用。

36.在本说明书中记载为p 型或n 型的情况下,意味着掺杂浓度比p型或n型的掺杂浓度高,在记载为p-型或n-型的情况下,意味着掺杂浓度比p型或n型的掺杂浓度低。另外,在本说明书中记载为p 型或n 型的情况下,意味着掺杂浓度比p 型或n 型的掺杂浓度高。

37.在本说明书中,化学浓度是指不依赖于电有源化的状态而测定的杂质的浓度。化学浓度能够通过例如二次离子质谱分析法(sims)来计测。上述净掺杂浓度能够通过电压-电容测定法(cv法)来测定。另外,可以将利用扩展电阻测定法(sr法)计测到的载流子浓度作为净掺杂浓度。通过cv法或sr法计测的载流子浓度可以被设为热平衡状态下的值。另外,在n型的区域中,施主浓度远远大于受主浓度,因此也可以将该区域中的载流子浓度设为施主浓度。同样地,在p型的区域中,也可以将该区域中的载流子浓度设为受主浓度。

38.另外,在施主、受主或净掺杂的浓度分布具有峰的情况下,可以将该峰值设为该区域的施主、受主或净掺杂的浓度。在施主、受主或净掺杂的浓度几乎均匀的情况下等,也可以将该区域中的施主、受主或净掺杂的浓度的平均值设为施主、受主或净掺杂的浓度。

39.对于通过sr法计测而得的载流子浓度而言,有时存在结晶缺陷的区域的载流子浓度低于半导体基板的载流子浓度。在测定扩展电阻时电流流通的范围内,半导体基板的载流子移动度的值低于硅的载流子移动度的值。由于晶格缺陷等引起的结晶结构的混乱(紊乱)而使载流子散乱,从而产生载流子移动度的下降。

40.[实施例一]

[0041]

图1a是本实施方式的实施例一的半导体装置100的局部俯视图。半导体装置100具备半导体基板,该半导体基板具有包括igbt等晶体管元件的晶体管部70、以及包括续流二极管(fwd)等二极管元件的二极管部80。图1a将晶体管部70和二极管部80的边界周边呈现于中心。

[0042]

应予说明,在本说明书中简称为俯视的情况是指从半导体基板的正面侧观察的情况。在本例中,将在俯视下晶体管部70和二极管部80的排列方向称为x轴,将在半导体基板的正面与x轴垂直的方向称为y轴,将与半导体基板的正面垂直的方向称为z轴。

[0043]

晶体管部70和二极管部80可以分别在延伸方向上具有长度。即,晶体管部70的y轴方向上的长度大于x轴方向上的宽度。同样地,二极管部80的y轴方向上的长度大于x轴方向

上的宽度。晶体管部70和二极管部80的延伸方向与后述的各沟槽部的长度方向可以相同。

[0044]

二极管部80在半导体基板的背面具有n 型的阴极区。在本说明书中,将设置有阴极区的区域称为二极管部80。即,二极管部80是在俯视下与阴极区重叠的区域。另一方面,晶体管部70在半导体基板的背面具有p 型的集电区。

[0045]

本例的半导体装置100具备设置在半导体基板的正面侧的内部的栅极沟槽部40、虚设沟槽部30、阱区11、发射区12、基区14以及抽出区15。栅极沟槽部40和虚设沟槽部30分别是沟槽部的一例。

[0046]

另外,本例的半导体装置100在半导体基板的正面的上方具备栅极金属层50和发射极52。栅极金属层50和发射极52彼此分离而设置。

[0047]

虽然在发射极52与半导体基板的正面之间、以及栅极金属层50与半导体基板的正面之间设置有层间绝缘膜,但是在图1a中省略。在本例的层间绝缘膜,接触孔49、接触孔54、接触孔56以及接触孔58贯通该层间绝缘膜而设置。在图1a中,对各个接触孔标注斜线的阴影。

[0048]

发射极52设置于栅极沟槽部40、虚设沟槽部30、阱区11、发射区12、基区14以及抽出区15的上方。发射极52通过接触孔54而与半导体基板的正面的发射区12、基区14以及抽出区15电连接。

[0049]

发射极52通过接触孔56或接触孔58而与虚设沟槽部30内的虚设导电部电连接。在发射极52与虚设导电部之间可以设置有由掺杂了杂质的多晶硅等导电性材料形成的连接部25。连接部25分别设置在绝缘膜上。在绝缘膜的上表面设置有bpsg(boro phospho silicate glass:硼磷硅玻璃)等层间绝缘膜和发射极52。

[0050]

栅极金属层50通过接触孔49而与栅极流道48电连接。栅极流道48可以由掺杂了杂质的多晶硅等形成。栅极流道48在半导体基板的正面与栅极沟槽部40内的栅极导电部电连接。栅极金属层50不与虚设沟槽部30内的虚设导电部和发射极52电连接。

[0051]

栅极流道48与发射极52可以通过层间绝缘膜和氧化膜等绝缘物而电分离。本例的栅极流道48从接触孔49的下方设置到栅极沟槽部40的前端部。在栅极沟槽部40的前端部,栅极导电部在半导体基板的正面露出,并与栅极流道48连接。

[0052]

发射极52和栅极金属层50由包含金属的导电性材料形成。例如,发射极52和栅极金属层50由铝或以铝为主要成分的合金(铝-硅、铝-硅-铜等)形成。这些各电极可以在由铝等形成的区域的下层具有由钛或钛化合物等形成的阻挡金属。

[0053]

各电极也可以在接触孔内具有由钨等形成的插塞。插塞可以埋入接触孔内,也可以在与半导体基板接触的一侧设置阻挡金属并且以与阻挡金属接触的方式埋入钨而形成。

[0054]

阱区11与栅极流道48和虚设沟槽部30重叠而设置。本例的阱区11相对于接触孔54的y轴方向上的端向栅极流道48侧分离而设置。另外,阱区11以覆盖虚设沟槽部30的方式设置。阱区11是掺杂浓度比基区14的掺杂浓度高的第二导电型的区域。

[0055]

本例的基区14是p-型,阱区11是p 型。另外,阱区11从半导体基板的正面起,形成到比基区14的下端更深且比栅极沟槽部40和虚设沟槽部30更深的位置。

[0056]

晶体管部70和二极管部80分别具有沿排列方向(x轴方向)排列有多个的沟槽部。本例的晶体管部70沿x轴方向具有一个以上的栅极沟槽部40、以及一个以上的虚设沟槽部30。本例的二极管部80沿x轴方向具有多个虚设沟槽部30。在本例的二极管部80不设置栅极

沟槽部40。

[0057]

本例的栅极沟槽部40可以具有沿着与排列方向垂直的延伸方向(y轴方向)而延伸的两个直线部分39(沿着y轴方向呈直线状的沟槽的部分)、以及连接两个直线部分39的前端部41。

[0058]

前端部41的至少一部分在俯视下可以设置为曲线状。如后所述,前端部41将两个直线部分39的y轴方向上的端部彼此与栅极流道48连接。

[0059]

虚设沟槽部30可以具有沿延伸方向延伸的直线形状,也可以与栅极沟槽部40同样地具有直线部分29和前端部31。图1a所示的半导体装置100包括不具有前端部31的直线形状的虚设沟槽部30、以及具有前端部31的虚设沟槽部30这两者。

[0060]

栅极沟槽部40和虚设沟槽部30的y轴方向上的端部在俯视下设置于阱区11。即,在各沟槽部的y轴方向的端部,各沟槽部的深度方向(z轴方向)上的底部被阱区11覆盖。由此,能够缓解各沟槽部的该底部处的电场集中。

[0061]

图1b是示出图1a的a-a'截面的图。a-a'截面是包括栅极沟槽部40和虚设沟槽部30并且通过抽出区15和基区14的xz面。本例的半导体装置100在a-a'截面具有基板10、层间绝缘膜38、发射极52以及集电极24。

[0062]

在x轴方向上,在相邻的沟槽部之间设置有台面部。台面部是指在基板10的内部被沟槽部夹持的区域。作为一例,台面部的深度位置是距基板10的正面21到沟槽部的下端为止的位置。

[0063]

本例的台面部被在x轴方向上相邻的沟槽部夹持,并且在基板10的正面21沿着沟槽部在y轴方向上延伸而设置。如后所述,在本例中,在晶体管部70设置有台面部60,在二极管部80设置有台面部61。在本说明书中,在简称为台面部的情况下,分别指台面部60和台面部61。

[0064]

在各台面部设置有基区14。在晶体管部70的各台面部,在俯视下被基区14夹持的区域可以设置有第一导电型的发射区12和第二导电型的抽出区15中的至少一者。如图1a所示,发射区12是n 型,抽出区15是p 型。发射区12和抽出区15在z轴方向上,可以设置在基区14与基板10的正面21之间。

[0065]

晶体管部70的台面部具有在基板10的正面21露出的发射区12。在本例中,在晶体管部70的台面部设置有在基板10的正面21露出的发射区12和抽出区15。

[0066]

如后所述,若对栅极沟槽部40的栅极导电部施加栅极电压,则在z轴方向上,在设置于发射区12与漂移区之间的基区14形成有因n 型的反型层而成的沟道。抽出区15能够抽出从p 型的集电区22流向基板10的正面21侧的空穴电流,因此能够抑制闩锁。

[0067]

晶体管部70的台面部中的发射区12和抽出区15分别从x轴方向上的一个沟槽部设置到另一个沟槽部。作为一例,台面部的发射区12和抽出区15沿着y轴方向而交替地配置。

[0068]

在其他的例子中,晶体管部70的台面部中的发射区12和抽出区15也可以沿y轴方向而设置为条纹状。例如,在与沟槽部接触的区域设置有发射区12,在被发射区12夹持的区域设置有抽出区15。

[0069]

其中,在晶体管部70,在与二极管部80相邻的台面部不设置发射区12,而在俯视下被基区14夹持的区域设置有在基板10的正面21露出的抽出区15。

[0070]

在二极管部80的台面部不设置发射区12。在二极管部80的台面部可以设置有在基

板10的正面21露出的基区14。基区14可以配置在二极管部80的整个台面部。

[0071]

在各台面部的上方设置有接触孔54。接触孔54在俯视下配置于在延伸方向(y轴方向)上被基区14夹持的区域。本例的接触孔54设置在抽出区15、基区14以及发射区12这些各区域的上方。接触孔54可以在台面部的排列方向(x轴方向)上配置在各个台面部的中央。

[0072]

在二极管部80,在与基板10的背面23相邻的区域设置有n 型的阴极区82。在基板10的背面23,在不设置阴极区82的区域可以设置有p 型的集电区22。在图1a中,利用虚线来表示阴极区82与集电区22的边界。

[0073]

阴极区82在y轴方向上与阱区11分离而配置。由此,通过确保掺杂浓度比较高且形成到深的位置的p型的阱区11与阴极区82之间的距离,从而能够抑制来自阱区11的空穴注入,并且能够降低反向恢复损耗。

[0074]

本例的阴极区82的y轴方向上的端部被配置为,比接触孔54的y轴方向上的端部更离开阱区11。在其他的例子中,阴极区82的y轴方向上的端部也可以配置在阱区11与接触孔54之间。

[0075]

基板10可以是硅基板,也可以是碳化硅基板,还可以是氮化镓等氮化物半导体基板等。本例的基板10是硅基板。

[0076]

基板10具有第一导电型的漂移区18。本例的漂移区18是n-型。漂移区18可以是在基板10中未设置其他掺杂区域而残留的区域。

[0077]

在漂移区18的上方,可以在z轴方向上设置有一个以上的蓄积区16。蓄积区16是比漂移区18更高浓度地蓄积了与漂移区18相同的掺杂剂的区域。蓄积区16是掺杂浓度比漂移区18的掺杂浓度高的n型。通过设置蓄积区16,从而从晶体管部70的p-型的基区14到沟槽部的底部,提高来自基板10的背面侧的空穴的蓄积量。由此,能够提高基于电子的载流子的注入促进效果(ie效果),并能够降低导通电压。

[0078]

层间绝缘膜38设置在基板10的正面21。层间绝缘膜38是添加有硼或磷等杂质的硅酸盐玻璃等绝缘膜。层间绝缘膜38可以与正面21接触,在层间绝缘膜38与正面21之间也可以设置有氧化膜等其他膜。在层间绝缘膜38设置有在图1a中说明的接触孔54。

[0079]

发射极52设置在基板10的正面21和层间绝缘膜38的上表面。发射极52由包含金属的材料形成。发射极52通过层间绝缘膜38的接触孔54而与基板10的正面21电连接。

[0080]

在接触孔54的内部也可以设置有钨(w)等接触插塞。插塞设置在接触孔54中的分别与抽出区15、基区14以及发射区12接触的区域。

[0081]

在设置有插塞的接触孔的底部(z轴正侧的端部)形成有插塞区17。插塞区17是掺杂浓度比抽出区15的掺杂浓度高的第二导电型的区域。本例的插塞区17是p 型。由此,改善了阻挡金属与抽出区15之间的接触电阻。另外,插塞区17的厚度(z轴方向距离)为大致0.5μm以下,并且是在俯视下比抽出区15小的区域。

[0082]

插塞区17在晶体管部70的动作中通过改善接触电阻而使闩锁耐量提高。另一方面,在二极管部80的动作中,在没有插塞区的情况下阻挡金属与基区14之间的接触电阻高,导通损耗、开关损耗上升,但是通过设置插塞区17,抑制导通损耗和开关损耗的上升。

[0083]

集电极24设置于基板10的背面23。集电极24由包含金属的材料形成。

[0084]

在晶体管部70,在x轴方向上相邻的沟槽部之间设置有台面部60。在台面部60,在基区14的上方,与正面21接触而设置有发射区12和抽出区15中的至少一者。发射区12的掺

杂浓度比漂移区18的掺杂浓度高。

[0085]

在本例中,在晶体管部70的台面部60,在基板10的正面21露出的发射区12和抽出区15沿y轴方向交替地配置。应予说明,因为图1b所示的a-a'截面沿x轴方向通过配置有抽出区15的位置,所以没有示出发射区12。

[0086]

其中,在二极管部80侧的台面部60不设置发射区12,而设置有在基板10的正面21露出的抽出区15。

[0087]

在二极管部80,在相邻的沟槽部之间设置有台面部61。在台面部61设置有在正面21露出的基区14。二极管部80的基区14作为阳极而动作。

[0088]

在漂移区18的下方可以设置有第一导电型的缓冲区20。本例的缓冲区20是n型。缓冲区20的掺杂浓度比漂移区18的掺杂浓度高。缓冲区20可以作为防止从基区14的背面侧扩展的耗尽层到达集电区22和阴极区82的场截止层而起作用。

[0089]

在晶体管部70,在缓冲区20的下方设置有集电区22。在二极管部80,在缓冲区20的下方设置有阴极区82。集电区22和阴极区82可以设置为相同的深度。集电区22和阴极区82可以在基板10的背面23接触而设置。二极管部80在晶体管部70关断时,可以作为使反向导通的回流电流流通的续流二极管(fwd)而起作用。

[0090]

在基板10设置有栅极沟槽部40和虚设沟槽部30。栅极沟槽部40和虚设沟槽部30被设置为,从正面21贯通基区14和蓄积区16而到达漂移区18。

[0091]

沟槽部贯通掺杂区域并不限于以形成掺杂区域之后形成沟槽部的顺序进行制造。在形成了沟槽部后在沟槽部之间形成掺杂区域的情况也包括在沟槽部贯通掺杂区的情况中。

[0092]

栅极沟槽部40具有设置于正面21的栅极沟槽、栅极绝缘膜42以及栅极导电部44。栅极绝缘膜42覆盖栅极沟槽的内壁而设置。栅极绝缘膜42可以使栅极沟槽的内壁的半导体氧化或氮化而形成。栅极导电部44在栅极沟槽的内部设置在比栅极绝缘膜42更靠内侧的位置。栅极导电部44的上表面可以位于与基板10的正面21相同的xy平面内。栅极绝缘膜42将栅极导电部44与基板10绝缘。栅极导电部44由掺杂有杂质的多晶硅等半导体形成。

[0093]

栅极导电部44可以在z轴方向上设置到比基区14更深的位置。栅极沟槽部40在正面21被层间绝缘膜38覆盖。若对栅极导电部44施加栅极电压,则在z轴方向上设置于发射区12与漂移区18之间的基区14,在与栅极沟槽部40接触的界面的表层形成有因电子的反型层而成的沟道。

[0094]

虚设沟槽部30在xz截面可以具有与栅极沟槽部40相同的结构。虚设沟槽部30具有设置在基板10的正面21的虚设沟槽、虚设绝缘膜32以及虚设导电部34。

[0095]

虚设绝缘膜32覆盖虚设沟槽的内壁而设置。虚设绝缘膜32可以通过使虚设沟槽的内壁的半导体氧化或氮化而形成。虚设导电部34在虚设沟槽的内部设置在比虚设绝缘膜32更靠内侧的位置。虚设导电部34的上表面可以位于与正面21相同的xy平面内。虚设绝缘膜32将虚设导电部34与基板10绝缘。虚设导电部34可以由与栅极导电部44相同的材料形成。

[0096]

本例的栅极沟槽部40和虚设沟槽部30在基板10的正面21被层间绝缘膜38覆盖。应予说明,栅极沟槽部40和虚设沟槽部30的z轴方向上的底部可以是向下侧凸起的曲面状(在截面中为曲线状)。

[0097]

在漂移区18,在基板10的正面21侧,从晶体管部70的至少一部分遍及二极管部80

而设置有包含寿命控制剂的寿命控制区85。在晶体管部70中,将不具有寿命控制区85的区域称为晶体管区72,将具有寿命控制区85的区域称为边界区74。晶体管区72是在俯视半导体基板时与二极管部80分离的区域。边界区74是在俯视半导体基板时位于晶体管区72与二极管部80之间的区域。

[0098]

可以从基板10的正面21或背面23照射质子或氦,寿命控制区85在从基板10的正面21朝向背面23的方向上形成得比沟槽部的底部深。寿命控制剂通过例如将氦或质子注入到预定的深度位置,从而在基板10的内部形成晶体缺陷。在本例中,寿命控制区以掺杂浓度为1

×e10

cm-3

以上且1

×e13

cm-3

以下的掺杂量形成。

[0099]

作为一例,在从基板10的正面21照射质子或氦的情况下,利用金属或抗蚀掩模来遮挡不形成寿命控制区85的区域,对晶体管部70和二极管部80照射质子或氦。质子或氦没有照射到被掩模遮挡的区域。

[0100]

在图1b中,利用

“×”

的记号来表示寿命控制区85的z轴方向上的位置。寿命控制区85的z轴方向上的位置是寿命控制剂的浓度分布的z轴方向上的峰位置。

[0101]

寿命控制区85的z轴方向上的位置可以与阱区11的背面的z轴方向上的位置相等,寿命控制区86的z轴方向上的位置也可以比阱区11的背面的z轴方向上的位置更靠下方。

[0102]

寿命控制区85的x轴负侧的端部k在俯视下成为晶体管部70的晶体管区72与边界区74之间的边界。

[0103]

若二极管部80导通,则电子电流从阴极区82流向作为阳极层而动作的基区14。若电子电流到达基区14,则发生电导率调制,并从阳极层流有空穴电流。其中,由于基区14也设置于晶体管部70,所以产生从阴极区82朝向晶体管部70的基区14扩散的电子电流。

[0104]

因此,不仅从二极管部80的基区14产生朝向阴极区82的空穴电流,也从晶体管部70的基区14产生朝向阴极区82的空穴电流。此外,利用朝向晶体管部70扩散的电子电流,促进来自晶体管部70的抽出区15的空穴注入。

[0105]

抽出区15的硼的掺杂浓度比基区14的硼的掺杂浓度高两个数量级,因此通过来自抽出区15的空穴注入而使基板10的空穴密度上升。由此,在二极管部80关断时直到空穴消失为止消耗时间,因此反向恢复峰电流变大,反向恢复损耗变大。

[0106]

本例的寿命控制区85在关断时促进在基区14产生的空穴与从阴极区82注入的电子的复合。如此,寿命控制区85通过促进关断时的载流子消失,抑制反向恢复时的峰电流,从而降低反向恢复损耗。

[0107]

本例的寿命控制区85从二极管部80遍及边界区74而设置,因此与仅在二极管部80设置寿命控制区的情况相比,寿命控制区85的端部k与阴极区82之间的距离长。因此,能够更加促进在边界区74的基区14产生的空穴电流与从阴极区82流入的电子的复合,能够抑制二极管部80在反向恢复时的峰电流。

[0108]

其中,在设置了寿命控制区85的区域中,由于从基板10的正面21照射的质子或氦,所以对沟槽氧化膜造成损伤,界面态变化。

[0109]

在被照射了质子或氦的栅极沟槽部40中,在向栅极导电部44施加栅极电压时,在栅极沟槽部40的栅极绝缘膜42残留有损伤,隧穿电流增大。因此,在边界区74,与晶体管区72相比阈值电压降低。由此,因为在关断时电流容易集中于边界区74,所以半导体装置100容易因闩锁而被破坏。

[0110]

本例的边界区74具有抑制在施加栅极电压时产生的隧穿电流的电流抑制结构。在一个例子中,边界区74具有作为电流抑制结构的虚设沟槽部30来代替栅极沟槽部40的一部分。在一个例子中,在边界区74,作为虚设沟槽部30的数量相对于栅极沟槽部40的数量的比率的虚设比率大于1。另外,边界区74中的虚设比率可以高于晶体管区72中的虚设比率。

[0111]

如此,本例的边界区74具有改变栅极沟槽部40与虚设沟槽部30的虚设比率的电流抑制结构,从而在维持作为晶体管部70的功能的同时,抑制隧穿电流的增加。另一方面,通过使边界区74中的电子电流的比例降低,从而能够使边界区74的阈值电压变得比晶体管部70的阈值电压高。

[0112]

因此,能够通过使电子电流的比例降低从而抑制因隧穿电流的增加而引起的边界区74的阈值电压的降低。另外,在边界区74中,通过使电流密度降低,从而能够抑制边界区74的阈值电压的降低,并且能够抑制整个晶体管部70的阈值电压的降低或偏差。

[0113]

此外,漂移区18可以在基板10的背面23侧遍及整个晶体管部70和整个二极管部80而具有寿命控制区86。寿命控制区86可以通过从基板10的背面23照射质子或氦而形成。

[0114]

在从基板10的背面23照射氦或者质子的情况下,氦或质子不通过沟槽氧化膜,沟槽氧化膜的界面顺序不变化。另外,由于从基板10的背面23到寿命控制区86的深度方向位置为止的距离短,所以能够通过低能量状态的照射来形成寿命控制区86。

[0115]

如此,本例的半导体装置100除寿命控制区85以外还具有寿命控制区86,因此能够促进关断时的载流子消失。例如,寿命控制区85能够抑制反向恢复时的峰电流,寿命控制区86能够加快电流的切断,因此能够进一步降低反向恢复损耗。

[0116]

图1c是本实施方式的实施例一的半导体装置100的局部俯视图。图1c将晶体管部70中的晶体管区72呈现于中心。

[0117]

在晶体管区72,虚设沟槽部30可以设置在栅极沟槽部40的各直线部分39之间。在各直线部分39之间可以设置有一条虚设沟槽部30,也可以设置有多条虚设沟槽部30。

[0118]

另外,在各直线部分39之间,也可以不设置虚设沟槽部30而可以设置栅极沟槽部40。通过这样的结构,与在边界区74全部设为虚设沟槽部30相比,能够增大来自发射区12的电子电流,因此导通电压降低。

[0119]

在本例的晶体管区72,一条栅极沟槽部40与两条虚设沟槽部30在x轴方向上交替地配置。应予说明,在图1c中,虽然在晶体管区72的边界区74侧配置有虚设沟槽部30,但是也可以配置有栅极沟槽部40。

[0120]

在图1c所示的例子中,在晶体管区72中,在两条栅极沟槽部40的直线部分39之间配置有两条虚设沟槽部30的直线部分29。通过前端部41将两个直线部分39的y轴方向上的端部彼此与栅极流道48连接,从而使栅极金属层50作为针对栅极沟槽部40的栅电极而起作用。另一方面,通过将前端部41设为曲线状,从而比终止于直线部分39的情况更能够缓解端部处的电场集中。

[0121]

图1d是本实施方式的实施例一的半导体装置100的局部俯视图。图1d将晶体管部70中的边界区74呈现于中心。

[0122]

边界区74具有设置于漂移区18的寿命控制区85。在本例的边界区74,一条栅极沟槽部40和五条虚设沟槽部30在x轴方向上交替地配置。在边界区74,作为虚设沟槽部30的数量相对于栅极沟槽部40的数量的比率的虚设比率大于1。

[0123]

在图1d所示的例子中,在边界区74,从边界区74与晶体管区72的边界朝向x轴正侧,依次配置一条栅极沟槽部40和五条虚设沟槽部30。

[0124]

在图1d所示的例子中,在边界区74,在两条栅极沟槽部40的直线部分39之间配置有五条虚设沟槽部30的直线部分29。通过前端部41将两个直线部分39的y轴方向上的端部彼此与栅极流道48连接,从而使栅极金属层50作为针对栅极沟槽部40的栅电极而起作用。另一方面,通过将前端部41设为曲线状,从而比终止于直线部分39的情况更能够缓解端部处的电场集中。

[0125]

在本例的晶体管区72中,一条栅极沟槽部40与两条虚设沟槽部30在x轴方向上交替地配置的情况,相对于此,在边界区74,一条栅极沟槽部40与五条虚设沟槽部30在x轴方向上交替地配置。如此,边界区74中的虚设比率高于晶体管区72中的虚设比率。

[0126]

即,本例的晶体管部70在晶体管区72与边界区74使虚设比率变化。边界区74具有作为电流抑制结构的虚设沟槽部30来代替栅极沟槽部40,通过使所述边界区74的虚设比率变得高于晶体管区72的虚设比率,从而能够减少电子电流流通的比例。因此,能够使边界区74的阈值电压变得高于晶体管部70的阈值电压,并且能够抑制因隧穿电流的增加而导致的阈值电压的降低。如此,能够抑制因寿命控制区85引起的阈值降低的影响。

[0127]

边界区74的x轴方向上的宽度可以是50μm以上且150μm以下。或者,边界区74的x轴方向上的宽度可以是100μm以上且150μm以下。另外,边界区74的面积可以是晶体管区72的面积的3倍以上。

[0128]

如此,由于具有寿命控制区85的边界区74具有电流抑制结构,所以能够抑制因寿命控制区85引起的阈值降低的影响。

[0129]

图1e是本实施方式的实施例一的半导体装置100的局部俯视图。图1e示出边界区74中的栅极沟槽部40和虚设沟槽部30的配置的变型。

[0130]

在图1e所示的例子中,在晶体管区72,一条栅极沟槽部40与两条虚设沟槽部30在x轴方向上交替地配置,在边界区74,一条栅极沟槽部40与五条虚设沟槽部30在x轴方向上交替地配置,与图1d所示的例子相同。其中,在本例的边界区74,从边界区74与晶体管区72的边界朝向x轴正侧,依次配置五条虚设沟槽部30与一条栅极沟槽部40。

[0131]

在本例中,在边界区74,作为虚设沟槽部30的数量相对于栅极沟槽部40的数量的比率的虚设比率也大于1。另外,边界区74中的虚设比率高于晶体管区72中的虚设比率。

[0132]

如此,由于边界区74具有电流抑制结构,所以能够得到抑制因寿命控制区85而引起的阈值降低的影响的效果,并且能够在不受配置的顺序或规则性约束的情况下高自由度地配置栅极沟槽部40和虚设沟槽部30。

[0133]

应予说明,本例的边界区74的宽度和面积的范围与图1d所示的例子相同,因此在此省略说明。

[0134]

图2是示出栅极电压vge与电流之间的关系的图表。在图2中,横轴表示对栅极沟槽部40的栅极导电部44施加的栅极电压vge[v],纵轴表示在施加栅极电压vge时产生的电流[a]。作为用于计算的条件,在30a额定电压品的半导体装置100中,在从晶体管部70与二极管部80之间的边界向晶体管部70侧到100μm为止的范围,从基板10的正面21侧照射氦,形成寿命控制区85。

[0135]

另外,将晶体管区72和边界区74的面积比设为1:3,计算出栅极电压vge与电流之

间的关系。在此,在晶体管区72中电流22.5ma的栅极电压vge成为阈值电压,在边界区74中电流7.5ma时的栅极电压vge成为阈值电压。

[0136]

在图2中,实线表示整个晶体管部70中的电流,单点划线表示晶体管区72中的电流,虚线表示边界区74中的电流。计算的结果是,整个晶体管部70中的阈值电压为6.2v,晶体管区72中的阈值电压为6.52v,边界区74中的阈值电压为5.92v。

[0137]

在上述计算条件下得到了如下结果:与晶体管区72中的阈值电压相比,在整个晶体管部70中阈值电压降低0.3v,在边界区74中阈值电压降低0.6v。

[0138]

边界区74中的电流密度相对于晶体管区72中的电流密度大致为9倍。如此,若将晶体管区72中的虚设比率设为1倍,则将边界区74中的虚设比率设为1倍以上且9倍以下,从而能够在防止电流密度的上升,并且抑制阈值电压的降低。

[0139]

[实施例二]

[0140]

图3是实施例二的半导体装置200的局部俯视图。在此,对与半导体装置100共同的要素标注相同的符号,并省略说明。图3将晶体管部70中的边界区74呈现于中心。

[0141]

在半导体装置200的边界区74,在两条栅极沟槽部40的直线部分39之间配置有两条虚设沟槽部30的直线部分29。即,在半导体装置200的边界区74,与晶体管区72同样地,一条栅极沟槽部40和两条虚设沟槽部30在x轴方向上交替地配置。

[0142]

晶体管区72和边界区74具有在基板10的正面21露出的发射区12和抽出区15。在晶体管区72,发射区12和抽出区15在y轴方向上交替地配置,但是在边界区74,发射区12的一部分被剔除。即,边界区74中的发射区12的比率低于晶体管区72中的发射区12的比率。

[0143]

本例的边界区74设置有抽出区15来代替发射区12的一部分,或者使基区14在基板10的正面21露出。可以设置为,在发射区12被剔除的区域与发射区12相邻的情况下,配置抽出区15,在发射区12被剔除的区域不与发射区12相邻的情况下,使基区14在基板10的正面21露出。

[0144]

在边界区74,对于一部分栅极沟槽部40而言,从相邻的台面部60剔除发射区12而不与发射区12接触。这样的栅极沟槽部40成为即使与栅极金属层50连接,也在施加栅极电压时不流通电流的所谓的有效(active)虚设沟槽,作为电流抑制结构而起作用。

[0145]

本例的边界区74由于具有作为电流抑制结构的有效虚设沟槽,所以能够得到与半导体装置100的边界区74同样的效果。在本例的边界区74,有效虚设沟槽的数量可以比栅极沟槽部40的数量多。另外,在本例的边界区74,可以提高虚设沟槽部30的数量与有效虚设沟槽的数量的总数相对于栅极沟槽部40的数量的比率。

[0146]

如此,在半导体装置200中,通过使边界区74中的发射区12的比率降低,从而能够降低从发射区12流通的电子电流密度,并能够得到与在边界区74中减少了栅极沟槽部40的数量的半导体装置100同样的效果。

[0147]

应予说明,在半导体装置200中,在边界区74,与晶体管区72同样地,在x轴方向上交替地配置一条栅极沟槽部40与两条虚设沟槽部30,但是不限于此。也可以与半导体装置100同样地,在半导体装置200的边界区74,将一条栅极沟槽部40与五条虚设沟槽部30在x轴方向上交替地配置,也可以设为不同的虚设比率。

[0148]

以上,虽然利用实施方式对本发明进行了说明,但是本发明的技术范围不限于上述实施方式所记载的范围。对本领域技术人员来说,在上述实施方式中能够追加多种变更

或改良是显而易见的。根据权利要求书所的记载可知,追加了这样的变更或改良的方式也能够包括在本发明的技术范围内。

[0149]

应当注意,权利要求书、说明书及附图中示出的装置、系统、程序及方法中的动作、过程、步骤和阶段等各处理的执行顺序只要未特别明示“早于”、“预先”等,另外,未在后续处理中使用之前的处理结果,则可以以任意顺序来实现。关于权利要求书、说明书及附图中的动作流程,即使为方便起见使用“首先”、“接下来”等进行了说明,也并不意味着必须以该顺序来实施。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。