半导体装置

1.本技术是申请日为2016年3月17日、发明名称为“固态图像捕获元件与电子设备”的申请号为201680015741.4的专利申请的分案申请。

技术领域

2.本公开涉及一种固态图像捕获元件以及电子设备,且更具体地涉及一种能够通过使用中空区域减少电容的固态图像捕获元件以及电子设备。

背景技术:

3.在互补金属氧化物半导体(cmos)图像传感器中,当像素的微型化继续发展时,光电二极管的开口面积减小,且敏感度降低。进一步地,像素晶体管的尺寸减小,且随机噪声变得恶化。结果,信噪比(s/n)降低且图像质量变劣。

4.因此,已提出通过减小浮置扩散(fd)的寄生电容和提高电荷-电压转换效率来提高信噪比。

5.fd的寄生电容包括fd的扩散电容、通过fd配线连接到放大晶体管的栅电极的电容、fd配线的电容、以及任何其他电容。能通过降低fd的n型杂质的浓度来减小fd的扩散电容。然而,在这种情况下,存在对于接触故障的担忧。

6.能通过减小放大晶体管的尺寸来减小放大晶体管的栅电极的电容。然而,当减小放大晶体管的尺寸时,随机噪声更为恶化。

7.进一步地,能通过设计配线布局来在一定程度上减小fd配线的电容。然而,因为fd需要连接到放大晶体管,基于像素的共享系统,该配线布局是受限的。因此,通过设计配线布局来减小fd配线的电容是困难的。

8.因此,已提出通过将配线层的整个周边变为低介电常数膜(例如,参考ptl 1)来减小fd配线的电容的方法。

9.[引文清单]

[0010]

[专利文献]

[0011]

[ptl 1]

[0012]

jp 2009-231501 a

技术实现要素:

[0013]

[技术问题]

[0014]

作为一种减小电容的方法,希望不同于ptl 1中所述方法的方法。

[0015]

已考虑这样的情形来进行本公开,且使得通过使用中空区域来减小电容成为可能。

[0016]

[问题的解决方案]

[0017]

根据本公开的一个方面的固态图像捕获元件是这样的一种固态图像捕获元件,其中,连接到浮置扩散节点(floating diffusion)的fd配线与该fd配线以外的配线之间的区

域的至少一部分为中空区域。

[0018]

根据本公开的一个方面的电子设备与本公开的该一个方面的固态图像捕获元件对应。

[0019]

根据本公开的一个方面,连接到浮置扩散节点的fd配线与该fd配线以外的配线之间的区域的至少一部分为中空区域。

[0020]

[本发明的有益效果]

[0021]

根据本公开的一个方面,能够减小电容。进一步地,根据本公开的一个方面,能够使用中空区域减小电容。

[0022]

本公开中所述的有利效果未必是有限的,且可以是本公开中所述的任何效果。

附图说明

[0023]

[图1]

[0024]

图1为示出作为根据本公开的第一实施方式的固态图像捕获元件的cmos图像传感器的配置实例的示意图。

[0025]

[图2]

[0026]

图2为示出在图1的像素区域中二维排布的像素中的一个像素的电路配置实例的示意图。

[0027]

[图3]

[0028]

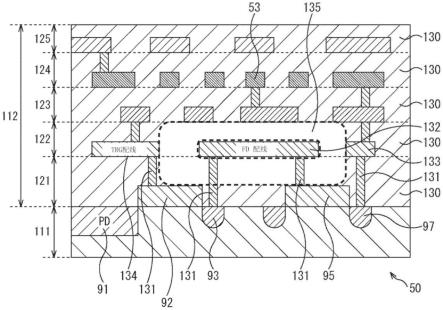

图3为示出cmos图像传感器的第一结构实例的示意图。

[0029]

[图4]

[0030]

图4为示出cmos图像传感器的第二结构实例的示意图。

[0031]

[图5]

[0032]

图5为示出cmos图像传感器的第三结构实例的示意图。

[0033]

[图6]

[0034]

图6为示出cmos图像传感器的第四结构实例的示意图。

[0035]

[图7]

[0036]

图7为示出根据本公开的第二实施方式的cmos图像传感器的像素的电路配置实例的示意图。

[0037]

[图8]

[0038]

图8为示出根据第三实施方式的cmos图像传感器的各部分布局的实例的视图。

[0039]

[图9]

[0040]

图9为从配线层侧来看图8中的像素区域的第一结构实例的平面图。

[0041]

[图10]

[0042]

图10包括沿图9中的a-a’切割而成的剖视图以及沿图9中的b-b’切割而成的剖视图。

[0043]

[图11]

[0044]

图11为用于说明制造图9和图10中的半导体基底的方法的示意图。

[0045]

[图12]

[0046]

图12为用于说明制造图9和图10中的半导体基底的方法的示意图。

[0047]

[图13]

[0048]

图13为用于说明制造图9和图10中的半导体基底的方法的示意图。

[0049]

[图14]

[0050]

图14为用于说明制造图9和图10中的半导体基底的方法的示意图。

[0051]

[图15]

[0052]

图15为沿图9中的a-a’切割而成的图8中像素区域的第二结构实例的剖视图。

[0053]

[图16]

[0054]

图16为用于说明制造图15中的半导体基底的方法的示意图。

[0055]

[图17]

[0056]

图17为用于说明制造图15中的半导体基底的方法的示意图。

[0057]

[图18]

[0058]

图18为用于说明制造图15中的半导体基底的方法的示意图。

[0059]

[图19]

[0060]

图19为用于说明制造图15中的半导体基底的方法的示意图。

[0061]

[图20]

[0062]

图20为沿图9中的a-a’切割而成的图8中像素区域的其他第二结构实例的剖视图。

[0063]

[图21]

[0064]

图21为沿图9中的a-a’切割而成的图8中像素区域的第三结构实例的剖视图。

[0065]

[图22]

[0066]

图22为用于说明制造图21中的半导体基底的方法的示意图。

[0067]

[图23]

[0068]

图23为用于说明制造图21中的半导体基底的方法的示意图。

[0069]

[图24]

[0070]

图24为示出fd配线与半导体基底之间的中空区域的其他结构实例的示意图。

[0071]

[图25]

[0072]

图25为用于说明制造图8中的cmos图像传感器的第一方法的示意图。

[0073]

[图26]

[0074]

图26为用于说明制造图8中的cmos图像传感器的第一方法的示意图。

[0075]

[图27]

[0076]

图27为用于说明制造图8中的cmos图像传感器的第一方法的示意图。

[0077]

[图28]

[0078]

图28为用于说明制造图8中的cmos图像传感器的第二方法的示意图。

[0079]

[图29]

[0080]

图29为用于说明制造图8中的cmos图像传感器的第二方法的示意图。

[0081]

[图30]

[0082]

图30为用于说明制造图8中的cmos图像传感器的第二方法的示意图。

[0083]

[图31]

[0084]

图31为用于说明制造图8中的cmos图像传感器的第二方法的示意图。

[0085]

[图32]

[0086]

图32为示出硅通孔(tsv)周围的中空区域的其他结构实例的示意图。

[0087]

[图33]

[0088]

图33为用于说明根据第四实施方式的cmos图像传感器的中空区域的排布的平面图。

[0089]

[图34]

[0090]

图34为示出图33中fd配线周围的中空区域的其他形状的实例的示意图。

[0091]

[图35]

[0092]

图35为示出在tsv周围形成的中空区域的形状实例的平面图。

[0093]

[图36]

[0094]

图36为示出根据本公开的作为电子设备的图像捕获设备的配置实例的框图。

[0095]

[图37]

[0096]

图37为示出上述cmos图像传感器的使用实例的示意图。

具体实施方式

[0097]

以下,将说明用于实施本发明的模式(以下称为实施方式)。将按以下次序进行该说明。

[0098]

1.第一实施方式:cmos图像传感器(图1至图6)

[0099]

2.第二实施方式:cmos图像传感器(图7)

[0100]

3.第三实施方式:cmos图像传感器(图8至图32)

[0101]

4.第四实施方式:cmos图像传感器(图33至图35)

[0102]

5.第五实施方式:电子设备(图36)

[0103]

6.cmos图像传感器的使用实例(图37)

[0104]

《第一实施方式》

[0105]

(根据第一实施方式的cmos图像传感器的配置实例)

[0106]

图1为示出作为根据本公开的第一实施方式的固态图像捕获元件的cmos图像传感器的配置实例的示意图。

[0107]

cmos图像传感器50包括像素区域51、像素驱动线52、垂直信号线53、垂直驱动单元54、列处理器55、水平驱动单元56、系统控制器57、信号处理器58、以及存储器单元59,它们全都形成于未示出的半导体基底(芯片)(如硅基底)上。

[0108]

cmos图像传感器50的像素区域51包括二维地排列成阵列形状的像素,每个像素具有光电转换元件,该元件生成与入射光量对应的电荷量的电荷,且将这些电荷累积在该光电转换元件内,使得该cmos图像传感器50进行图像捕获。进一步地,在像素区域51中,对于呈现阵列形状的像素,为每个行形成像素驱动线52,且为每个列形成垂直信号线53。

[0109]

垂直驱动单元54包括移位寄存器、地址解码器、或任何其他单元,且以行为单位驱动像素区域51的每个像素。像素驱动线52的一端连接到与垂直驱动单元54的每个行对应的未示出的输出端。尽管未示出垂直驱动单元54的详细配置,垂直驱动单元54具有读出扫描系统与清除扫描两个扫描系统。

[0110]

读出扫描系统顺序地选择各行,以便以行为单位从每个像素读取像素信号,并从与所选行的像素驱动线52连接的输出端输出所选的信号。以这种布置,将读出扫描系统选

择的行的像素读取为像素信号,这些信号是累积在光电转换元件中的电荷的电信号。读出扫描系统将像素信号提供给垂直信号线53。

[0111]

清除扫描系统开启从连接到每个行的像素驱动线52的输出端输出的重置信号,以清除(重置)来自光电转换元件的不必要电荷。通过清除扫描系统的扫描,为每个行顺序地进行了所谓的电子快门操作。在这种情况下,电子快门操作时丢弃光电转换元件的电荷以及开始新的曝光(开始累积电荷)的操作。

[0112]

列处理器55包括用于像素区域51的每个列的信号处理电路。列处理器55的每个信号处理电路对通过垂直信号线53从所选行的每个像素输出的像素信号进行诸如模拟/数字(a/d)转换处理的信号处理。在该信号处理之后,列处理器55临时地保存这些像素信号。

[0113]

水平驱动单元56包括移位寄存器、地址解码器、或任何其他单元,且顺序地选择列处理器55的信号处理电路。基于水平驱动单元56的有选择扫描,由列处理器55的每个信号处理电路处理的像素信号顺序地输出到信号处理器58。

[0114]

系统控制器57包括时序发生器或生成各种时序信号的任何其他单元。基于由时序发生器生成的各时序信号,系统控制器57控制垂直驱动单元54、列处理器55、以及水平驱动单元56。

[0115]

信号处理器58对从列处理器55输出的像素信号进行各种信号处理。此时,当必要时,信号处理器58将信号处理的中间结果存储在存储器单元59中,且在必要的时刻参考该存储器单元59。在该信号处理之后,信号处理器58输出像素信号。

[0116]

存储器单元59包括动态随机存取存储器(dram)或静态随机存取存储器(sram)。

[0117]

(像素的电路配置实例)

[0118]

图2为示出在图1的像素区域中二维排布的像素中的一个像素的电路配置实例的示意图。

[0119]

像素90具有作为光电转换元件的光电二极管91、传输晶体管92、fd 93、重置晶体管94、放大晶体管95、以及选择晶体管96。

[0120]

光电二极管91根据所接收的光量生成电荷,且累积电荷。光电二极管91的阳极端子接地,且具有经由传输晶体管92连接到fd 93的阴极端。

[0121]

传输晶体管92的栅极端子连接到为像素90形成的像素驱动线52中的线,用于提供传输信号。当由传输信号开启时,传输晶体管92读出由光电二极管91生成的电荷,并将该电荷传输给fd 93。

[0122]

fd 93保持从光电二极管91读取的电荷。重置晶体管94的栅极端子连接到为像素90形成的像素驱动线52中的线,用于提供重置信号。当由该重置信号开启时,重置晶体管94将fd 93中累积的电荷排出至电势vdd的电源97,且重置fd 93的电势。

[0123]

放大晶体管95的栅极端子连接到fd 93,且放大晶体管95通过使用电源97将与fd 93的电势对应的像素信号输出。

[0124]

选择晶体管96的栅极端子连接到为像素90形成的像素驱动线52中的线,用于提供选择信号。当由选择信号开启时,选择晶体管96将从放大晶体管95输出的像素信号经由垂直信号线53提供给图1中的列处理器55。

[0125]

可以在多个像素90间共用fd 93。

[0126]

(cmos图像传感器的第一结构实例)

[0127]

图3为示出cmos图像传感器50的第一结构实例的示意图。

[0128]

如图3中所示,cmos图像传感器50包括堆叠在诸如硅基底的半导体基底111上的配线层112。配线层112包括例如5个配线层121至125。

[0129]

在半导体基底111上,形成光电二极管91、fd 93、电源97等等。在半导体基底111上光电二极管91与fd 93之间,形成传输晶体管92。放大晶体管95连接到电源97。进一步地,在配线层124中,形成垂直信号线53。

[0130]

通过形成于配线层121之中的通孔131,放大晶体管95连接到形成于配线层122中的fd配线132。同时,通过形成于配线层121之中的通孔131,fd 93连接到fd配线132。以这种布置,通过通孔131与fd配线132,放大晶体管95与fd 93相连接。

[0131]

通过形成于配线层121之中的通孔131,电源97连接到形成于配线层122之中的配线133。通过形成于配线层121之中的通孔131,传输晶体管92连接到形成于配线层122之中的trg配线134。

[0132]

在配线层121至125的未形成配线的区域中,形成诸如sio膜的配线层间膜130。然而,在图3的实例中,fd配线132周围的区域(该区域包括fd配线132与相邻配线133之间的以及fd配线132与相邻trg配线134之间的整个区域,配线133与trg配线134形成于fd配线132以外的配线层122之中)为中空区域135。fd配线132与中空区域135相互接触。

[0133]

当配线层间膜130为sio膜时,中空区域(空气)135的介电常数为配线层间膜130的1/4倍。因此,通过形成中空区域135,fd配线132的电容减少到为形成中空区域135的情况下fd配线132的电容的约1/4。

[0134]

进一步地,因为配线层间膜130形成于配线层122中的中空区域135以外的区域之中,与在整个配线层122中均未形成配线层间膜130的情形相比,机械强度较高。

[0135]

(cmos图像传感器的第二结构实例)

[0136]

图4为示出cmos图像传感器50的第二结构实例的示意图。

[0137]

在图4所示的配置中,为与图3中部件相同的那些部件标以相同的附图标记。在合适的情况下,省略重复说明。

[0138]

图4中的cmos图像传感器50的结构与图3中的结构的不同在于形成了中空区域201至206,而非中空区域135。

[0139]

在图4的实例中,在fd配线132周围的区域(包括fd配线132与配线133之间的以及fd配线132与trg配线134之间的整个区域)中,形成中空区域201至206,以不与fd配线132、配线133以及trg配线134接触。

[0140]

(cmos图像传感器的第三结构实例)

[0141]

图5为示出cmos图像传感器50的第三结构实例的示意图。

[0142]

在图5所示的配置中,为与图3中部件相同的那些部件标以相同的附图标记。在合适的情况下,省略重复说明。

[0143]

图5中的cmos图像传感器50的结构与图3中的结构的不同在于形成了中空区域221而非中空区域135。

[0144]

在图5的实例中,fd配线132周围的区域(仅包括fd配线132与配线133之间的区域,不包括fd配线132与配线133之间的以及fd配线与trg配线134之间的整个区域)为中空区域221。

[0145]

也即,因为fd配线132处理模拟信号,因而与处理数字信号的诸如垂直信号线53的配线相比,fd配线132对噪声抵抗力弱。因此,希望减小因连接到电源97而成为噪声源的配线133与配线132之间的电容。然而,在有些情况下,保持trg配线134与fd配线132之间的电容更好。

[0146]

因此,在图5的实例中,将fd配线周围的区域(仅包括fd配线132与相邻配线133之间的区域以及fd配线132与相邻的trg配线134之间的区域中的fd配线132与配线133之间的区域)设为中空区域221。也即,在fd配线132与相邻配线133之间的区域以及fd配线132与相邻的trg配线134之间的区域之中,fd配线132与trg配线134之间区域以外的那个区域成为了中空区域221。

[0147]

结果,能够抑制通过fd配线132与成为噪声源的配线133之间的电容的噪声传播。进一步地,能够保持trg配线134与fd配线132之间的电容。

[0148]

如图5中所示,中空区域221可以与fd配线132以及配线133接触,或可以不与fd配线132以及配线133相接触。

[0149]

(cmos图像传感器的第四结构实例)

[0150]

图6为示出cmos图像传感器50的第四结构实例的示意图。

[0151]

在图6中所示的配置中,为与图3中部件相同的那些部件标以相同的附图标记。在合适的情况下,省略重复说明。

[0152]

图6中的cmos图像传感器50的结构与图3中的结构的不同在于除中空区域135之外,还形成中空区域241。

[0153]

在图6的实例中,垂直信号线53周围的整个区域为中空区域241。

[0154]

也即,当垂直信号线53的数目大时,可以进行高速驱动,但是配线密度增加了,且垂直信号线53的电容增加了。结果,响应劣化了,像素信号的变化增加了,且捕获的图像的图像质量劣化了。因此,在图6的实例中,垂直信号线53周围的整个区域作为中空区域241。以这种布置,可以减小垂直信号线53的电容。结果,通过抑制高速驱动期间像素信号的变化,可以提高所捕获图像的图像质量。

[0155]

在图6的实例中,尽管垂直信号线53周围的整个区域为中空区域241,仅垂直信号线53周围的一部分区域可以是中空区域241。进一步地,可以形成中空区域201至206或中空区域221而非中空区域135。

[0156]

进一步地,如图6中所示,中空区域241可以与或不与邻近垂直信号线53的配线接触。

[0157]

如上所述,在cmos图像传感器50中,fd配线132与配线133之间的以及fd配线132与trg配线134之间的区域的至少一部分为中空区域135(201至206,或221)。因此,可以减小fd配线132的电容,且可以提高电荷-电压转换效率,而无需改变配线布局。

[0158]

进一步地,因为无需改变配线布局,可以将任何系统用作共享cmos图像传感器50的像素的系统。

[0159]

在配线层121至125的区域中,不同于配线以及中空区域135(201至206、221和/或241),可以形成低介电常数膜而非配线层间膜130。

[0160]

《第二实施方式》

[0161]

(根据第二实施方式的cmos图像传感器的像素的电路配置实例)

[0162]

除二维排布在像素区域51中的每个像素的电路配置以及清除扫描系统的操作以外,根据本公开的第二实施方式的作为固态图像捕获元件的cmos图像传感器的配置与图1中所示的cmos图像传感器的配置相同。因此,以下,将仅描述每个像素的电路配置以及清除扫描系统的操作。将通过使用图1中的附图标记描述不同于cmos图像传感器的像素的配置元件。

[0163]

图7为示出根据本公开的第二实施方式的cmos图像传感器的像素的电路配置实例的示意图。

[0164]

在图7所示的配置中,为与图3中部件相同的那些部件标以相同的附图标记。在合适的情况下,省略重复说明。

[0165]

图7中的像素300的电路配置不同于图2中的像素90的电路配置,在于提供了fd301与302,而非fd93,且提供了重置晶体管303和304而非重置晶体管fd94。通过在像素300的重置晶体管304的开启与关闭状态之间切换,可以在高电荷-电压转换效率模式与低电荷-电压转换效率模式之间切换成像模式。

[0166]

具体地,在像素300中,放大晶体管95的栅极端子连接到fd301。在电源97与fd301之间,重置晶体管303与重置晶体管304经由fd302串联。

[0167]

相应行中的像素驱动线52中的不同线路连接到重置晶体管303的栅极端子与重置晶体管304的栅极端子。不同重置信号经由不同线路提供给这些栅极端子。将要提供给重置晶体管303的重置信号由垂直驱动单元54的清除扫描系统开启,以从清除来自光电二极管91的不必要的电荷。

[0168]

当图像捕获模式为低电荷-电压转换效率模式时,将要提供给重置晶体管304的重置信号总是由清除扫描系统维持在开启状态。因此,在这种情况下,当开启提供给重置晶体管303的重置信号时,fd301的电势变为电源97的电势vdd,且像素300的fd的电容仅变为fd301的电容。因而,电荷-电压转换效率变高了。

[0169]

另一方面,当图像捕获模式为低电荷-电压转换效率模式时,将要提供给重置晶体管304的重置信号总是由清除扫描系统维持在关闭状态。因此,在这种情况下,当将要提供给重置晶体管303的重置信号开启时,fd302的电势变为电源97的电势vdd,且像素300的fd的电容变为fd301与fd302的电容之和。因而,电荷-电压转换效率变低了。

[0170]

在如上所述配置的像素300中,基于fd301的电容与fd301和fd302的电容之和的比例来确定高电荷-电压转换效率模式下电荷-电压转换效率与低电荷-电压转换效率模式下电荷-电压转换效率之比(以下称为模式比)。fd301的电容与fd302的电容分别对未示出而连接到fd301的fd配线的电容与未示出而连接到fd302的fd配线的电容给出贡献。

[0171]

因此,在像素300中,为获得希望的模式比,在例如个自地连接到fd301与fd302的两条fd配线中的连接到fd301的fd配线周围形成与中空区域135(201至206或221)类似的中空区域。

[0172]

也即,如上所述,通过在fd配线周围形成中空区域,与其中未形成中空区域的情形相比,可以减小fd配线的电容。因此,形成中空区域,使得连接到fd301的fd配线的电容成为与fd301的电容对应的fd配线的电容,该fd配线的电容基于fd302的电容以及希望的模式比来确定。

[0173]

可以仅在连接到fd302的fd配线周围形成该中空区域,或是可以在连接到fd301与

fd302的两条fd配线周围形成该中空区域。进一步地,可以在多个像素300之间共享fd301与fd302。

[0174]

如上所述,在根据第二实施方式的cmos图像传感器中,形成了fd301与fd302的两个fd。fd配线连接到fd301与fd302。在这些fd配线中的至少一条周围形成中空区域。以这种布置,与周围未形成中空区域的fd配线的电容相比,周围形成中空区域的fd配线的电容被减小。结果,可以将模式比设定为希望的比例。

[0175]

另一方面,当在连接到fd301与fd302的fd配线周围未形成该中空区域时,需要通过配线布局来调整模式比。然而,当像素300小时,配线布局的自由度低。进一步地,基于像素300的共享系统,存在关于配线布局的限制。因此,通过配线布局调整模式比是困难的。

[0176]

《第三实施方式》

[0177]

(cmos图像传感器的各部分的布局实例)

[0178]

根据本公开的第三实施方式的作为固态图像捕获元件的cmos图像传感器的配置与图1中所示的cmos图像传感器50的配置相同。因此,省略对该配置的说明。进一步地,在随后的附图中,为与cmos图像传感器50的那些部件相同的部件标以相同的附图标记。在合适的情况下,省略重复说明。

[0179]

图8为示出根据第三实施方式的cmos图像传感器的各部分的布局实例的视图。

[0180]

根据图8中的cmos图像传感器320,在半导体基底322上堆叠半导体基底321。在半导体基底321上设置像素区域51,且在半导体基底322上设置控制电路331与逻辑电路332。在半导体基底321与322中的每一个上堆叠一个或多个配线层。半导体基底321堆叠在半导体基底322上,使得配线层接合在一起。

[0181]

例如,控制电路331为包括垂直驱动单元54、列处理器55、水平驱动单元56、以及系统控制器57的电路。例如,逻辑电路332为包括信号处理器58与存储器单元59的电路。

[0182]

在这种情况下,cmos图像传感器320的半导体基底的层数为2,但是可以是1或3或更多。进一步地,可以在其上设置有像素区域51的半导体基底321上形成控制电路331。

[0183]

(半导体基底321的第一结构实例)

[0184]

图9为从配线层侧来看图8中的像素区域51的第一结构实例的平面图。图10包括沿图9中的a-a’切割而成的剖视图以及沿图9中的b-b’切割而成的剖视图。为方便说明,图9示出半导体基底321以及仅仅一个最下方的配线层,且图10示出半导体基底321以及仅仅两个最下方的配线层。

[0185]

如图9和10中所示,在cmos图像传感器320中,在水平方向上相邻的两个像素90共享fd93。如图10中所示,在像素区域51的最下方的配线层351中,形成fd配线361,其用于在fd93与放大晶体管95的栅极之间连接重置晶体管94的源极。

[0186]

如图10中所示,fd配线361通过通孔361a连接到fd93,通过通孔361b连接到形成在半导体基底321上的重置晶体管94的源极,以及通过通孔361c连接到放大晶体管95的栅极。

[0187]

进一步地,如图9中所示,传输晶体管92的栅极连接有trg配线362,该trg配线362为配置像素驱动线52的一条配线。进一步地,如图10中所示,在配线层351上的配线层352中形成各种配线363。

[0188]

如图9和10中,在配线层351中,在fd配线361与其他未示出的配线之间,形成多个(在图10中的实例为4个)中空区域(气隙)364a。进一步地,在具有不同电势的fd配线361与

半导体基底321之间,形成了多个(图10实例中为6)中空区域364b。进一步地,在配线层352的fd配线361上方的区域中,形成多个中空区域364c。

[0189]

如上所述,在fd配线361与半导体基底321的其他配线或电极之间形成中空区域364a至364c。以这种布置,减小了fd配线361与其他配线或电极之间的介电常数,且减小了fd配线361的电容。结果,提高了电荷-电压转换效率。

[0190]

进一步地,形成于fd配线与其他配线之间的中空区域不是由一个中空区域而是由多个中空区域364a进行配置。因此,即使当增加fd配线361与其他配线之间的距离来减小fd配线361的电容,也可以将一个中空区域的尺寸做小。结果,可以容易地形成该中空区域。

[0191]

在配线层351和配线层352中,在未形成诸如fd配线361、trg配线362、和配线363、中空区域364a至364c、以及诸如传输晶体管92的晶体管的区域中,形成诸如sio膜的绝缘膜353(配线层间膜)。在第三实施方式中,绝缘膜353的材料为二氧化硅,但是不限于该材料。

[0192]

如上所述,在中空区域364a至364c之间存在绝缘膜353。因为中空区域364a至364c由绝缘膜353支持,与其中中空区域364a至364c由导体支持的情形相比,fd配线361的电容能够减小。

[0193]

(制造半导体基底321的第一结构实例的方法说明)

[0194]

图11至14为示出制造半导体基底321的方法的示意图,在该半导体基底321上堆叠有图9和图10中的配线层351和配线层352。

[0195]

首先,在图11的第一处理中,在半导体基底321上形成光电二极管91、fd93、以及配置像素90的晶体管(诸如传输晶体管92、重置晶体管94、以及放大晶体管95)。之后,在半导体基底321上形成绝缘膜353。

[0196]

在图11的第二处理中,在绝缘膜353上,通过在与fd配线361和半导体基底321之间的中空区域对应之区域以外的区域中涂布光刻胶381而形成光刻胶图案。之后,使用该光刻胶图案蚀刻绝缘膜353。结果,从未形成光刻胶381的区域(也即与中空区域364b对应的区域)除去绝缘膜353。能通过修改该光刻胶图案来控制中空区域364b的大小。

[0197]

在图12的第三处理中,剥离该光刻胶图案,且通过弱覆盖的成膜方法形成绝缘膜353。结果,形成fd配线361与半导体基底321之间的中空区域364b。在图12中的第四处理中,在绝缘膜353中,通过大马士革方法形成配线361以及通孔361a至361c,使得fd93连接到重置晶体管94的源极与放大晶体管95的栅极。

[0198]

在图13中的第五处理中,在绝缘膜353上,通过在与fd配线361和未在配线层351(其中形成fd配线361)中示出的其他配线之间的中空区域364a对应之区域以外的区域中涂布光刻胶381而形成光刻胶图案。之后,使用该光刻胶图案蚀刻绝缘膜353。结果,从未形成光刻胶381的区域(也即与中空区域364a对应的区域)除去绝缘膜353。

[0199]

在图13的第六处理中,剥离该光刻胶图案,且通过弱覆盖的成膜方法形成绝缘膜353。结果,形成了中空区域364a。在图14的第七处理中,通过大马士革方法形成配线层352的配线363。

[0200]

在图14的第八处理中,首先,以与图11中的第二处理、图12中的第三处理、以及图13中的第五和第六处理类似的方式形成fd配线361上方的中空区域364c。

[0201]

具体地,在绝缘膜353上,通过在与fd配线361上方的中空区域364c对应之区域以外的区域中涂布光刻胶381而形成光刻胶图案。之后,使用该光刻胶图案蚀刻绝缘膜353。结

果,从与中空区域364c对应的区域去除绝缘膜353。之后,剥离该光刻胶图案,且通过弱覆盖的成膜方法形成该绝缘膜353。

[0202]

图11的第二处理中的、图13的第五处理中的、以及图14的第八处理中的将要蚀刻的绝缘膜353的厚度(在垂直半导体基底321的方向上的长度),即每个中空区域364a至364c的厚度小于十分之几微米。

[0203]

如上所述,因为中空区域364a至364c上方的绝缘膜353通过弱覆盖的成膜方法形成,能够在中空区域364a至364c上方形成绝缘膜353,同时保持中空区域364a至364c的腔穴。中空区域364a至364c下方的绝缘膜353的质量可以与中空区域364a至364c上方的绝缘膜353的质量相同或不同。

[0204]

(半导体基底321的第二结构实例)

[0205]

图15为沿图9中的a-a’切割而成的图8中半导体基底321的像素区域51的第二结构实例的剖视图。为方便说明,图15示出半导体基底321以及仅仅两个最下方的配线层。

[0206]

在图15中所示的配置中,为与图10中部件相同的那些部件标以相同的附图标记。在合适的情况下,省略重复说明。

[0207]

图15中其上堆叠有配线层351与配线层352的半导体基底321的配置不同于图10中的配置,在于形成了阻挡膜401,以与fd配线361以及中空区域364a的底面接触。

[0208]

阻挡膜401为诸如sioc膜的膜,用于在通过大马士革方法形成fd配线361时阻止对绝缘膜353的蚀刻。

[0209]

(制造半导体基底321的第二结构实例的方法说明)

[0210]

图16至19为示出制造其上堆叠有图15中的配线层351与配线层362的半导体基底321的方法的示意图。

[0211]

首先,进行图11和12中的第一至第三处理,且形成fd配线361与半导体基底321之间的中空区域364b。接下来,在图16至18中的第一至第六处理中,通过大马士革方法形成fd配线361以及通孔361a至361c。

[0212]

也即,在图16的第一处理中,在其上形成有中空区域364b的半导体基底321上形成绝缘膜353。之后,平面化绝缘膜353。

[0213]

在图16的第二处理中,在绝缘膜353上形成阻挡膜401。在图17的第三处理中,在阻挡膜401上,(堆叠)形成具有预定厚度的绝缘膜353。

[0214]

在图17的第四处理中,蚀刻与阻挡膜401下方的绝缘膜353的通孔361a至361c对应的区域,且蚀刻与阻挡膜401上方的绝缘膜353的fd配线361对应的区域。对阻挡膜401上方的绝缘膜353的蚀刻被阻挡膜401阻止。也即,阻挡膜401上方的绝缘膜353的蚀刻区域的底面与阻挡膜401的上表面接触。

[0215]

在图18的第五处理中,在最上层的绝缘膜353上形成铜(cu)膜402。在图18的第六处理中,去除不必要的处于绝缘膜353上方的铜402。结果,形成fd配线361以及通孔361a至361c。

[0216]

接下来,在图19的第七处理中,在绝缘膜353上,通过在与fd配线361和未在配线层351(其中形成fd配线361)中示出的其他配线之间的中空区域364a对应之区域以外的区域中涂布光刻胶381而形成光刻胶图案。之后,使用该光刻胶图案蚀刻绝缘膜353,以通过阻挡膜401阻止该蚀刻。结果,从未形成光刻胶381的区域(也即与中空区域364a对应的区域)除

去绝缘膜353。

[0217]

之后,进行图13和图14中的第六至第八处理,且形成中空区域364a与中空区域364c。

[0218]

以上述布置,所有中空区域364a的底面与阻挡膜401的上表面接触。也即,所有中空区域364a的底面的厚度方向上的位置是相同的。因此,减小了中空区域364a的深度(垂直半导体基底的方向上的长度)的变化。结果,减小了fd配线361的电容的变化。

[0219]

在图19的第七处理中,在对绝缘膜353的蚀刻被阻挡膜401阻止后,可以进一步进行蚀刻,如图20中所示。

[0220]

(半导体基底321的第三结构实例)

[0221]

图21为沿图9中的a-a’切割而成的图8中半导体基底321的像素区域51的第三结构实例的剖视图。为方便说明,图21示出半导体基底321以及仅仅两个最下方的配线层。

[0222]

在图21中所示的配置中,为与图10中部件相同的那些部件标以相同的附图标记。在合适的情况下,省略重复说明。

[0223]

图21中其上堆叠有配线层351与配线层352的半导体基底321的配置不同于图10中的配置,在于四个连续的中空区域364a的下部连接在一起,且中空区域364a的上部周围的绝缘膜为绝缘膜421,其材料不同于绝缘膜353的材料。

[0224]

例如,绝缘膜421的材料为sin。

[0225]

(制造半导体基底321的第三结构实例的方法说明)

[0226]

图22和23为示出制造其上堆叠有图21中的配线层351和配线层352的方法的示意图。

[0227]

首先,进行图11和12中的第一至第三处理,且形成fd配线361与半导体基底321之间的中空区域364b。接下来,在图22的第一处理中,在绝缘膜353上形成绝缘膜421。之后,在绝缘膜353和绝缘膜421中,形成fd配线361与通孔361a至361c,以便通过大马士革方法与fd93接触。

[0228]

接下来,在图22的第二处理中,在绝缘膜421上,通过在与中空区域364a对应之区域以外的区域中涂布光刻胶381而形成光刻胶图案。

[0229]

之后,使用该光刻胶图案蚀刻绝缘膜353和绝缘膜421。结果,从其中未形成光刻胶381的区域(也即与中空区域364a对应的区域)中去除绝缘膜353与绝缘膜421。

[0230]

在图23的第三处理中,在绝缘膜353的蚀刻速率变得大于绝缘膜421的蚀刻速率的条件下进行对绝缘膜353和绝缘膜421的各向同性蚀刻。结果,仅蚀刻绝缘膜353,且四个中空区域364a的下部连接在一起。

[0231]

在图23的第四处理中,剥离光刻胶图案,且通过弱覆盖的成膜方法形成绝缘膜353。在这种情况下,尽管中空区域364a的下部具有大的尺寸,上部具有小的尺寸。因此,在绝缘膜353的材料到达该下部之前,中空区域364a闭合。结果,保持了中空区域364a的腔穴。之后,进行图14中的第七和第八处理,且形成中空区域364c。

[0232]

如图24中所示,以与应用于中空区域364a的方式类似的方式,可以在中空区域364b的上部周围形成绝缘膜421,且中空区域364b的下部可以连接在一起。进一步地,中空区域364a至364c中的每一个的下部的尺寸可以大于中空区域364a至364c中的每一个的上部的尺寸,且中空区域364a至364c的各个下部不连接在一起。

452的区域周围的区域中涂布光刻胶381,形成光刻胶图案。然后,使用该光刻胶图案蚀刻半导体基底321、绝缘膜451、以及绝缘膜353。以这种布置,从其中未形成光刻胶381的区域(即其中将形成tsv 452的区域周围的区域)去除半导体基底321、绝缘膜451与绝缘膜353。

[0247]

在图30的第三处理中,剥离光刻胶图案,且通过弱覆盖的成膜方法形成绝缘膜451。结果,在其中要形成tsv 452的区域周围的区域中形成穿透半导体基底321的中空区域432。

[0248]

在图31的第四处理中,蚀刻其中将要形成tsv 452的绝缘膜451、半导体基底321、绝缘膜353、以及绝缘膜445的区域,且形成tsv 452。

[0249]

如图32中所示,在第三处理中,在形成绝缘膜451时,可以将绝缘膜451埋在半导体基底321中的中空区域432中。进一步地,通过一个或两个通孔,tsv 452可以将配线层444的配线440连接到配线层351的配线363。

[0250]

如上所述,通过在tsv 452周围形成中空区域432,可以减小tsv 452与半导体基底321的电势部分(例如gnd)之间的电容。

[0251]

在第三实施方式中,中空区域364a至364c以及中空区域432的数目可以是等于1或更多的任何数目。中空区域364a至364c以及中空区域432可以具有其中未通过弱覆盖的成膜方法形成绝缘膜的任何形状。

[0252]

《第四实施方式》

[0253]

(像素区域中中空区域的布置说明)

[0254]

除第四实施方式中的cmos图像传感器具有在2个(水平)

×

2个(垂直)像素90间共享的fd 93以及中空区域364a至364c与中空区域432的布置和形状不同之外,根据本公开的第四实施方式的作为固态图像捕获元件的cmos图像传感器的配置和结构与cmos图像传感器320的配置和结构相同。

[0255]

因此,以下仅说明中空区域364a至364c以及中空区域432的布置以及形状。进一步地,在之后的附图中,为与cmos图像传感器320的部件相同的那些部件标以相同的附图标记。在合适的情况下,省略重复说明。

[0256]

图33为用于说明根据第四实施方式的cmos图像传感器的像素区域51中的中空区域的布置的平面图。图33为从布线层431所在的一侧来看的、其上堆叠有配线层351、配线层352以及配线层431的半导体基底321的像素区域51的平面图。

[0257]

图33中的a仅示出半导体基底321和配线层351,且图33中的b仅示出半导体基底321和配线层431。

[0258]

如图33的a中所示,在根据第四实施方式的cmos图像传感器中,在同一配线层351中,在fd配线361和诸如配线471的其他配线之间形成中空区域472。以这种布置,减小配线层351中fd配线361与其他配线之间的介电常数。结果,提高了电荷-电压转换效率。

[0259]

进一步地,如图33中的b中所示,在配线层431中,中空区域474在同一配线层431中的垂直信号线53与诸如配线473的其他配线之间形成。以这种布置,减小了配线层431中垂直信号线53和其他配线之间的介电常数,且减小了垂直信号线53的电容。结果,能够防止像素信号的读取方面的延迟。

[0260]

在图33中的a实例中,在fd配线361与其他配线之间形成两个中空区域472。中空区域472的数目可以是等于或大于一的任何数目。类似地,形成于垂直信号线53与其他配线之

间的中空区域474的数目可以是等于或大于一的任何数目。

[0261]

在图33的实例中,当从配线层431上方来看时,中空区域472与中空区域474中的每一个呈矩形(条带形)。然而,中空区域472与中空区域474中的每一个可以具有任何形状。

[0262]

(像素区域中中空区域的形状实例)

[0263]

图34为从配线层351所在的一侧来看其上堆叠有配线层352的半导体基底321的像素区域51的平面图,其示出了中空区域472的形状的其他实例。

[0264]

如图34中的a中所示,当从配线层351上方来看时,中空区域472中的每一个可以呈圆形(孔形),或例如图34中的b中所示,可以呈网状(网形)。

[0265]

尽管未示出,中空区域474中的每一个可以与中空区域472的形状相同。

[0266]

(非像素区域中中空区域形状实例)

[0267]

图35为从绝缘膜451上方来看根据第四实施方式的cmos图像传感器的平面图,其示出在并非cmos图像传感器的像素区域51的tsv 452周围形成的每个中空区域432的形状实例。

[0268]

如图35中的a中所示,当从绝缘膜451上方来看时,每个中空区域432可以呈现为矩形的环状,或例如图35中的b中所示,可以呈圆形的环状。进一步地,如图35中的c中所示,每个中空区域432可以呈直线形(条带形)。

[0269]

在图35中的a和c的实例中,在tsv 452周围形成的中空区域432的数目为二,且在图35中的b的实例中数目为一。然而,中空区域432的数目不限于这些数目,且可以是任何数目。

[0270]

中空区域432、中空区域472、以及中空区域474的形状不限于图34和图35中示出的形状,只要该中空区域具有这样的形状:其中绝缘膜未通过弱覆盖的成膜方法形成。

[0271]

进一步地,在第四实施方式中,可以以与第三实施方式中的方式类似的方式在fd配线361的下和上部中形成中空区域。

[0272]

进一步地,在第三实施方式中,可以以与第四实施方式中的方式类似的方式在垂直信号线53的周围形成中空区域。在第三和第四实施方式中,其中形成中空区域的区域可以在不同于fd配线361和垂直信号线53的、希望减小其电容的配线周围形成。

[0273]

在第三和第四实施方式中,可以在半导体基底322中形成中空区域。

[0274]

《第五实施方式》

[0275]

(根据一个实施方式的图像捕获设备的配置实例)

[0276]

图36为示出根据本公开的一个实施方式中作为电子设备的图像捕获设备的配置实例的框图。

[0277]

图36中的图像捕获设备1000为摄像机、数字静止相机等。图像捕获设备1000包括镜头组1001、固态图像捕获元件1002、数字信号处理(dsp)电路1003、帧存储器1004、显示单元1005、记录单元1006、操作单元1007、以及电源单元1008。dsp电路1003、帧存储器1004、显示单元1005、记录单元1006、操作单元1007、以及电源单元1008经由总线1009相互连接。

[0278]

镜头组1001捕获从被摄体射入的光(图像光),且在固态图像捕获元件1002的图像捕获表面上形成图像。固态图像捕获元件1002包括上述cmos图像传感器。固态图像捕获元件1002将通过镜头组1001在图像捕获表面上形成图像的那个数量(以像素为单位)的入射光转换成电信号,且将该电信号提供给dsp电路1003作为像素信号。

[0279]

dsp电路1003对从固态图像捕获元件1002提供的该像素信号进行预定的图像处理,将以帧为单位的该处理后的图像信号提供给帧存储器1004,且将该图像信号临时地存储在帧存储器1004中。

[0280]

显示单元1005包括例如平板型显示设备(诸如液晶面板或有机电致发光(el)面板),且基于临时存储在帧存储器1004中的以帧为单位的像素信号显示图像。

[0281]

记录单元1006包括数字多功能盘(dvd)、闪存等,其读出临时存储在帧存储器1004中的以帧为单位的像素信号,且记录该像素信号。

[0282]

在用户的操作下,操作单元1007发出关于图像捕获设备1000的各种功能的操作指令。电源单元1008适当地供电给dsp电路1003、帧存储器1004、显示单元1005、记录单元1006、以及操作单元1007。

[0283]

应用本技术的电子设备可以是在图像捕获单元(光电转换单元)中使用cmos图像传感器的设备。除图像捕获设备1000外,该技术可以应用于具有图像捕获功能的便携式终端设备以及在图像读取单元中使用cmos图像传感器的复印机。

[0284]

(cmos图像传感器的使用实例)

[0285]

图37为示出以上cmos图像传感器的使用实例的示意图。

[0286]

例如,如上所述,可以将上述的cmos图像传感器用于各种情形,如用于感测可见光、红外光、紫外光、x射线光。

[0287]-一种被提供用于捕获供观看的图像的设备,诸如数字相机、以及具有相机功能的移动设备。

[0288]-一种被提供用于交通的设备,诸如对车辆的前方、后方、周围和内部进行拍照以用于诸如自动停止的安全驾驶以及用于识别驾驶员状态的车载传感器,监视行驶中的车辆和道路的监视相机,以及测量车辆之间距离的距离测量传感器。

[0289]-一种被提供用于诸如电视机、电冰箱、空调的家用电器的设备,用于对用户的姿势拍照,以根据该姿势操作家用电器。

[0290]-一种被提供用于医疗和保健的设备,诸如通过接收红外光进行血管造影的内窥镜以及设备。

[0291]-一种被提供用于安全的设备,诸如用于防止犯罪的监视相机和用于人员身份验证的相机。

[0292]-一种被提供用于化妆用途的设备,诸如捕获皮肤图像的皮肤测量设备以及捕获头皮图像的显微镜。

[0293]-一种被提供用于运动的设备,诸如用于运动应用的运动摄像机和可穿戴相机。

[0294]-一种被提供用于农业的设备,诸如用于监视田地与作物的状态的相机。

[0295]

本说明书中描述的效果是说明性的且不是有限的。存在其他效果。

[0296]

进一步地,不欲将本公开的实施方式限于上述的实施方式,且在不背离本公开的范围的情况下,各种更改是可能的。

[0297]

本公开也可以应用于电荷耦合器件(ccd)图像传感器,而不限于cmos图像传感器。

[0298]

也可以如下配置本公开。

[0299]

(1)

[0300]

一种固态图像捕获元件,其中,连接至浮置扩散节点的浮置扩散配线与所述浮置

扩散配线以外的配线之间的区域的至少一部分为中空区域。

[0301]

(2)

[0302]

根据(1)的固态图像捕获元件,其中,所述浮置扩散配线与所述中空区域相互接触。

[0303]

(3)

[0304]

根据(1)的固态图像捕获元件,其中,所述浮置扩散配线与所述中空区域未相互接触。

[0305]

(4)

[0306]

根据以上(1)至(3)中之一的固态图像捕获元件,其中,所述中空区域为所述浮置扩散配线与所述浮置扩散配线以外的所述配线之间的区域中所述浮置扩散配线与连接到传输晶体管的trg配线之间区域以外的区域。

[0307]

(5)

[0308]

根据以上(1)至(4)中之一的固态图像捕获元件,其中,垂直信号线的周围的至少一部分为中空区域。

[0309]

(6)

[0310]

根据以上(1)至(5)中之一的固态图像捕获元件,其中,所述浮置扩散配线为个自地连接到多个浮置扩散节点的多条浮置扩散配线中的一条。

[0311]

(7)

[0312]

根据以上(1)的固态图像捕获元件,其中,所述中空区域的数目为多个。

[0313]

(8)

[0314]

根据以上(1)或(7)的固态图像捕获元件,其中,在所述浮置扩散配线与所述浮置扩散配线以外的所述配线之间的区域中的所述中空区域以外的区域中形成绝缘膜。

[0315]

(9)

[0316]

根据以上(8)的固态图像捕获元件,其中,在所述中空区域的上部周围形成的绝缘膜的材料和在所述中空区域的下部周围形成的绝缘膜的材料是不同的。

[0317]

(10)

[0318]

根据以上(9)的固态图像捕获元件,其中,所述中空区域的下部的尺寸大于所述上部的尺寸。

[0319]

(11)

[0320]

根据以上(10)的固态图像捕获元件,其中,所述中空区域的数目为多个,且所述多个中空区域的下部连接在一起,以及它们的上部连接在一起。

[0321]

(12)

[0322]

根据以上的(1)与(7)至(11)中之一的固态图像捕获元件,其中,所述浮置扩散配线与跟所述浮置扩散配线接触的半导体基底之间的区域的至少一部分为中空区域。

[0323]

(13)

[0324]

根据以上的(1)与(7)至(11)中之一的固态图像捕获元件,包括:

[0325]

第一半导体基底,其上堆叠有所述浮置扩散配线、所述浮置扩散配线以外的所述配线、以及其中形成所述中空区域的配线层;

[0326]

第二半导体基底,其接合到所述第一半导体基底;以及

[0327]

连接部分,其将所述第一半导体基底电连接到所述第二半导体基底,其中,在所述配线层的所述连接部分周围形成中空区域。

[0328]

(14)

[0329]

根据以上(13)的固态图像捕获元件,其中,在所述配线层的所述连接部分周围形成的所述中空区域穿透所述第一半导体基底。

[0330]

(15)

[0331]

一种电子设备,包括:

[0332]

固态图像捕获元件,其中,连接至浮置扩散节点的浮置扩散配线与所述浮置扩散配线以外的配线之间的区域的至少一部分为中空区域。

[0333]

(16)

[0334]

一种固态图像捕获元件,包括:

[0335]

第一半导体基底;

[0336]

第二半导体基底,其接合到所述第一半导体基底;以及

[0337]

连接部分,其将所述第一半导体基底电连接到所述第二半导体基底,其中,在堆叠于所述第一半导体基底上的配线层的所述连接部分周围形成中空区域。

[0338]

[参考符号列表]

[0339]

50cmos图像传感器,53垂直信号线,92传输晶体管,93fd,132fd配线,133配线,134trg配线,135、201至206、221、241中空区域,301、302fd,320cmos图像传感器,321、322半导体基底,351、352配线层,353绝缘膜,361fd配线,364a至364c中空区域,421绝缘膜,432中空区域,452tsv,1000图像捕获设备,1002固态图像捕获元件。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。