1.本揭示案实施例是有关于半导体装置及其制造方法,尤其是半导体装置具有接面电路以垂直堆叠半导体装置内的晶粒。

背景技术:

2.由于各种电子元件(如晶体管、二极管、电阻器、电容器等)的集成密度不断提高,因此半导体产业持续地成长。在大多数情况下,集成密度的提高来自于最小特征尺寸的连续减小,这允许更多的元件整合至特定面积中。

3.除更小的电子元件外,元件封装的改善旨在提供更小的半导体封装,借此比先前的封装使用更少的面积。半导体封装类型包括四方扁平封装(quad flat pack,qfp)、接脚格栅阵列(pin grid array,pga)、球栅阵列(ball grid array,bga)、倒装晶片(flip chip,fc)、三维集成电路(three-dimensional integrated circuit,3dic)、晶圆级封装(wafer level package,wlp)、封装堆叠(package on package,pop)、晶片上系统(system on chip,soc)或集成电路上系统(system on integrated circuit,soic)装置。

4.其中一些三维装置(例如,3dic、soc、soic)是通过将晶片置放于半导体晶圆层级上的晶片上方来制备的。由于堆叠晶片可缩短晶片之间的互连长度,所以这样的三维装置可改善的集成密度及提供其他优势,例如更快的速度及更高的频宽。然而,仍有许多与三维装置相关的挑战亟待解决。

技术实现要素:

5.根据本揭示案的一个实施例,一种半导体装置包括第一半导体晶粒以及第二半导体晶粒,其中第二半导体晶粒包括接合至第一半导体晶粒的侧表面,使得第二半导体晶粒垂直于第一半导体晶粒。半导体装置还包括接面电路,用于将第一半导体晶粒连接至第二半导体晶粒。

6.根据本揭示案的另一实施例,一种接面电路包括接合沟槽,其具有第一表面及与第一表面相对的第二表面,以及第一末端及与第一末端相对的第二末端。接面电路还包括接合衬垫,形成于接合沟槽的第一表面上及接合沟槽的第一末端处,其中接合衬垫配置以电性耦合接面电路与第二晶粒。接面电路还包括接合通孔,形成于接合沟槽的第二表面上及接合沟槽的第二末端处,其中接合通孔配置以电性耦合接面电路与第一晶粒。

7.根据本揭示案的又一实施例,一种制造半导体装置的方法包括形成第一半导体晶粒、形成第二半导体晶粒且在第二半导体晶粒的侧表面上形成接合层、在接合层中形成接面电路、以及将接合层接合至第一半导体晶粒使得第二半导体晶粒垂直于第一半导体晶粒,且接面电路将第一半导体晶粒连接至第二半导体晶粒。

附图说明

8.阅读以下实施方法时搭配附图以清楚理解本揭示案的观点。应注意的是,根据业

界的标准做法,各种特征并未按照比例绘制。事实上,为了能清楚地讨论,各种特征的尺寸可能任意地放大或缩小。

9.图1根据本揭示案的各种实施例绘示半导体晶粒的垂直截面图;

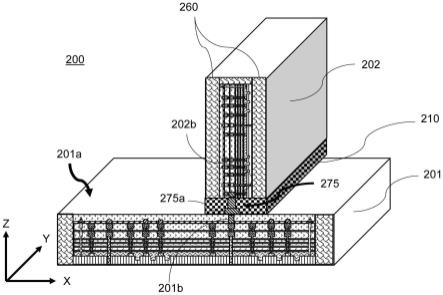

10.图2根据本揭示案的各种实施例绘示半导体封装的透视图;

11.图3a至图3c根据本揭示案的各种实施例绘示形成半导体封装的方法中的各种操作;

12.图4根据本揭示案的各种实施例绘示半导体晶粒群组(例如,垂直半导体晶粒堆叠)的垂直截面图;

13.图5根据本揭示案的各种实施例绘示堆叠半导体晶粒群组(例如,垂直半导体晶粒堆叠);

14.图6根据本揭示案的各种实施例绘示半导体装置;

15.图7a至图7d根据本揭示案的各种实施例绘示形成半导体装置的方法的各种操作;

16.图8根据本揭示案的各种实施例绘示形成半导体装置的方法的流程图;

17.图9根据本揭示案的各种实施例绘示使用4个例示性接面电路(例如,接合层金属走线)的位置及配置;

18.图10a至图10d根据各种实施例绘示例示性接面电路(例如,接合层金属走线)中的每一者的平面图(x及y方向)及垂直截面图(x及z方向);

19.图11根据本揭示案的各种实施例绘示接面电路(例如,接合层金属走线)的透视图;

20.图12根据本揭示案的各种实施例绘示半导体装置的分解图;

21.图13根据本揭示案的各种实施例绘示制造半导体装置的方法的流程图;

22.图14a至图14i根据本揭示案的各种实施例绘示形成接面电路的例示性方法中可能包括的各种操作;

23.图15根据本揭示案的各种实施例绘示形成接面电路的方法的流程图。

24.【符号说明】

25.100:半导体晶粒

26.108:半导体基板

27.112:层间介电质(interlayer dielectric,ild)

28.114:金属间介电质(intermetal dielectric,imd)

29.114a、114b、114c、114d、114e:imd层

30.115:蚀刻终止层及密封层

31.116:金属特征

32.119:钝化层

33.122:栅极

34.124:密封环

35.150:基板穿孔(through substrate via,tsv)

36.150b、150c、150d:导电通孔

37.200:半导体装置

38.201:第一半导体晶粒

39.201a:第一界面表面

40.201b:第一触点

41.202:第二半导体晶粒

42.202a:第二界面表面

43.202b:第二触点

44.210:接合层

45.260:介电封装层

46.275:接面电路

47.275a:接合衬垫

48.300a、300b、300c、300d:半导体晶粒

49.310:接合层

50.310a、310b、310c、310d:接合层

51.312:层间介电质

52.314:金属间介电质

53.326:金属衬垫

54.335a、335b、353c:导电通孔

55.340:导电通孔

56.350:半导体晶粒群组

57.350a、350b:半导体晶粒群组

58.359:保护层

59.360:介电封装层

60.375:接面电路

61.375-1、375-2、375-3、375-4:接面电路

62.375a:接合衬垫

63.375b:接合沟槽

64.375c:接合通孔

65.399:载具

66.400:堆叠半导体晶粒群组

67.460:介电封装层

68.498:载具接合层

69.499:载具

70.500:半导体装置

71.501:第一半导体晶粒

72.501a:第一界面表面

73.501b:第一触点

74.502:第二半导体晶粒

75.502a:第二界面表面

76.502b:第二触点

77.502b-1:钨触点

78.502b-2:铜沟槽

79.502b-3:组合钨触点/铜沟槽

80.502b-4:组合铜沟槽/通孔/沟槽

81.502b-5:铜通孔

82.502b-6:组合铜沟槽/通孔

83.502b-7:铝衬垫

84.502b-8:组合铝衬垫/铜沟槽

85.502b-9:组合接合金属/铝衬垫

86.510:接合层

87.510a:第一接合层

88.510b:第二接合层

89.510c:第三接合层

90.511a:第一蚀刻终止层

91.511b:第二蚀刻终止层

92.512:第一孔

93.513:第二孔

94.514:第三孔

95.586:电触点

96.614:非金属区域

97.650a:无金属区域

98.650b:无金属区域

99.800:半导体装置

100.801:第一半导体晶粒

101.801a:第一界面表面

102.801b:第一触点

103.802:第二半导体晶粒

104.802a:第二界面表面

105.802b:第二触点

106.810:接合层

107.891~897:步骤

108.1310~1340:步骤

109.1510~1560:步骤

110.x、y、z:方向

具体实施方式

111.以下的揭示内容提供许多不同的实施例或范例,以展示本揭示案的不同特征。以下将揭示本揭示案各部件及其排列方式的特定范例,用以简化本揭示案叙述。当然,这些特定范例并非用于限定本揭示案。例如,若是本揭示案以下的发明内容叙述了将形成第一结构于第二结构之上或上方,即表示其包括了所形成的第一及第二结构是直接接触的实施

例,亦包括了尚可将附加的结构形成于上述第一及第二结构之间,则第一及第二结构为未直接接触的实施例。为了能清楚地讨论,各种特征的尺寸可能任意地放大或缩小。

112.再者,为了方便描述附图中一元件或特征部件与另一(些)元件或特征部件的关系,可使用空间相关用语,例如“在...之下”、“下方”、“下部”、“上方”、“上部”及例如此类用语。除了附图所绘示的方位外,空间相关用语亦涵盖使用或操作中的装置的不同方位。当装置被转向不同方位时(例如,旋转90度或者其他方位),则其中所使用的空间相关形容词亦将依转向后的方位来解释。

113.半导体晶粒可含有一或多个集成电路,例如记忆体、处理器(多个)、或其他半导体元件(多个)中的至少一者有关。可在晶圆上形成数个这样的晶粒,接着将其切出(dice out)(即,单体化(singulate))并自晶圆移除。根据一或多个实施例,晶圆以及由此移除的一或多个半导体晶粒可包括硅、锗、绝缘体上硅(silicon on insulator,soi)、或一或多个磊晶层中的至少一者。

114.可使用锯(例如金刚石锯)自晶圆切割出半导体晶粒。晶粒附接膜(die attach film,daf)可用于在切粒及移除制程期间保持半导体晶粒之间的相对位置。锯沿晶圆上的划线切割,以自晶圆移除半导体晶粒,并将半导体晶粒彼此分离。

115.已知合格晶粒(known good die)可置放于例如玻璃基板或其他材料的载具上。满足一或多个品质度量而因此被称为已知合格晶粒的半导体晶粒置放于载具上。通过将已知合格晶粒置放于载具上可减轻良率的降低,这是因为形成于已知合格晶粒上的半导体配置不太可能进行形成于缺陷晶粒上所导致的相关操作。

116.相较于最初形成于晶圆上的半导体晶粒,当半导体晶粒置放于载具上时,个别半导体晶粒之间的空间或距离量可增加。当置放已知合格晶粒于载具上时可调整半导体晶粒之间的空间或距离,使得并非所有来自晶圆的半导体晶粒都被转移至载具上。半导体晶粒之间的额外空间可提供更大的使用面积以用于电性连接半导体晶粒,因此可作为扇出封装(fan-out packaging)。

117.已知合格晶粒可嵌入载具上的材料(例如模塑料(molding compound))中。模塑料可形成于半导体晶粒上方及周围。可移除模塑料的顶部部分以暴露出半导体晶粒的顶表面。当移除模塑料以暴露出半导体晶粒的顶表面时,导电垫(有时称为互连件)可显露出来。半导体晶粒之间的额外区域可允许增大数目的输入/输出(input/output,i/o)信号线自半导体晶粒的互连件扇出。除其他外,增大的i/o信号导线数目可使各个半导体晶粒的引脚数(pin count)增加,从而允许自各个半导体晶粒达到更多的电性连接、功能等。半导体晶粒之间的额外区域可允许在半导体晶粒之间的模塑料上方形成被动装置,例如电感器及电容器,这可降低基板信号损耗,其中当被动装置更靠近半导体基板或更靠近形成于基板上的其他元件时,则可能发生基板信号损耗。

118.半导体装置,例如集成晶片上系统(system on integrated chip,soic)装置、基板上晶圆(wafer on substrate,cowos)装置及晶圆上晶片(chip on wafer,cow)装置,可包括数个半导体晶粒在其中。

119.通常,晶粒至晶粒(例如,晶片至晶片)堆叠技术(例如,soic、基板上晶圆上晶片(chip on wafer on substrate,cowos)、整合扇出(integrated fan out,info)等)可将半导体晶粒水平堆叠于彼此顶部上。当堆叠多层半导体晶粒时,顶部及底部半导体晶粒不能

直接连接。基板穿孔(through substrate via,tsv)可用于连接顶部半导体晶粒与底部半导体晶粒,但这可在半导体晶粒之间引入额外电阻。举例而言,当形成数个半导体晶粒的半导体堆叠时,最顶(即,非相邻)半导体晶粒可能需要经过形成于数个中介半导体晶粒内的一系列tsv来传递电信号,以到达最底半导体晶粒。经过这些额外的tsv可导致电阻提升。

120.在本揭示案的一些实施例中,半导体晶粒可垂直堆叠,以使垂直集成晶片系统(system of integrated chip,soic)装置具有创新的垂直soic界面设计,从而实现高密度多晶粒连接。垂直soic装置可包括接面电路,其用于连接半导体晶粒的混合接合(例如,混合接合接触电路、接面电路导线、铜导线等)。垂直soic装置的优点可包括:(1)增加连接在一起的半导体晶粒(例如,晶片)数目;以及(2)降低半导体晶粒之间的电阻。接面电路可使每个垂直堆叠的半导体晶粒直接连接至连接晶粒。此外,连接晶粒可在堆叠中的非相邻半导体晶粒之间提供更直接的连接。因此,可减小总电阻。

121.在一些实施例中,具有第二半导体晶粒的半导体晶粒群组(例如,顶部晶粒垂直晶片组)可垂直堆叠于第一半导体晶粒(例如,底部半导体晶粒)上。半导体晶粒群组中一或多个第二半导体晶粒可直接耦合至第一半导体晶粒(例如,底部半导体晶粒)。因此,可增加堆叠半导体晶粒的数目,同时不增加不同半导体晶粒之间的电阻。

122.半导体晶粒群组中第二半导体晶粒可经由接面电路处的接合(例如,混合接合)垂直连接至第一半导体晶粒。在接面电路处,第二半导体晶粒的任何层(例如,金属层)可连接至第一半导体晶粒。在一些实施例中,可在第二半导体晶粒的第二界面表面上形成接合层,并用于拉出铜(cu)导线。

123.在一些实施例中,半导体晶粒群组的底部界面表面(例如,连接表面)可包括单层金属,或在一些实施例中可包括两层或两层以上的金属材料,以做为第二触点。举例而言,钨(w)触点、cu(im/tm)、al(例如,al衬垫)、tin/tan(例如,阻障层)可单独使用或组合使用。

124.在一些实施例中,可在无金属区域(例如,硅、金属间介电质(intermetal dielectric,imd)等)中形成接合重分布层(例如,接合层金属走线、电路延伸等),并用来当作接面电路(例如,混合接合面)。接合重分布层(redistribution layer,rdl)可用来改善接合区域。接合rdl可包括例如连接至半导体晶粒群组中第二界面表面的接合通孔、接合衬垫(以接触第一半导体晶粒)、及用于将接合通孔连接至接合衬垫的接合沟槽。

125.参考附图,图1根据本揭示案的一或多个实施例绘示半导体晶粒100,其中半导体晶粒100可在半导体封装中且半导体封装具有多晶粒堆叠。半导体晶粒100可包括半导体基板108(例如,硅基板)。层间介电质(interlayer dielectric,ild)112可形成于半导体基板108上,且金属间介电质(intermetal dielectric,imd)114可形成于ild 112上方。ild 112及imd 114可包括例如无掺杂硅玻璃(undoped silicon glass,usg)、氟硅玻璃(fluorosilicate glass,fsg)等。imd 114可包括数个imd层114a至114e,其可由各种蚀刻终止层及密封层115分离。蚀刻终止层及密封层115可包括例如sic、sin等。其他适合蚀刻终止材料可在预期的揭示范畴内。

126.金属特征116可形成于imd 114中。金属特征116可包括例如各种导电金属通孔,其可形成于各种导电金属接线之间并与各种导电金属接线接触。金属接线可形成于imd 114的不同层上。金属特征116可由铜、铜合金、铝、铝合金、或其一些组合物形成。可用于金属特征116的其他适合导电金属材料在预期的揭示范畴内。最上imd层114e及金属特征116的上

表面可平坦化为共面,且钝化层119可形成于最上层的imd层114e及金属特征116的经平坦化表面上。钝化层119可包括例如氧化硅(例如,si

x

oy)、氮化硅(si

x

ny)、苯并环丁烯(bcb)聚合物、聚酰亚胺(pi)、聚苯并口咢唑(pbo)或其组合物,且可通过例如旋转涂布、化学气相沉积(chemical vapor deposition,cvd)或类似者的适合制程形成。

127.一或多个半导体晶体管装置的一或多个栅极122可形成于半导体基板108上。金属特征116可电性连接至栅极122。一或多个密封环124亦可形成于imd114中。形成的密封环124可围绕半导体晶粒100的功能电路区域。密封环124可与金属特征116电性隔离,并可为半导体晶粒100的特征提供保护,让半导体晶粒100在制程中期间不受可能存在的水、化学品、残留物、及/或污染物的影响。密封环124可由导电材料(例如,金属材料)形成,更具体而言,可由与金属特征116相同的材料、在同一时间、且通过与金属特征116相同的制程形成。在其他实施例中,密封环124可由不同于形成金属特征116的材料的导电材料形成。

128.半导体晶粒100亦可包括一或多个导电基板穿孔(through substrate via,tsv)150,其中导电tsv150可连接至金属特征116中的一或多者。导电tsv 150可自金属特征116延伸穿过imd 114、ild 112、及半导体基板108。导电tsv 150可包括例如铜、金、银、铝或这些金属中的两者或两者以上的合金,例如铝铜(alcu)合金。用于tsv 150的其他导电金属材料可在预期的揭示范畴内。

129.半导体晶粒100可例如附接至基板(未显示)。基板可包括半导体晶圆或载具基板,且可包括例如硅基材料,例如玻璃或氧化硅、氧化铝、陶瓷材料、或其组合物。基板可包括平面顶表面,半导体晶粒100的半导体基板108可附着于其上。

130.可在半导体晶粒100上形成介电封装层360,以封装半导体晶粒100的至少一部分。介电封装层360可包括例如二氧化硅。或者,介电封装层360可包括无掺杂硅玻璃(usg)、氟硅玻璃(fsg)、sic、sion、sin、sicn、低k膜、极低k(extreme low-k,elk)膜、磷硅玻璃(psg)及四乙氧基硅烷(teos)。用于介电封装层360的其他介电材料在预期的揭示范畴内。

131.半导体晶粒100可为半导体晶粒堆叠中的一部分。举例而言,可在半导体晶粒100上形成接合层310(例如,接合结构),并使用接合层310将半导体晶粒100接合至半导体晶粒堆叠中的另一个半导体晶粒。接合层310的材料及形成方法可类似于ild 112的材料及形成方法。导电通孔340可形成于接合层310中且接触(例如,直接或间接地)半导体晶粒100中的金属特征116。导电通孔340可由与金属特征116及/或导电tsv 150相同的材料形成。在其他实施例中,导电通孔340可由不同于金属特征116及/或tsv 150的导电材料形成。

132.图2根据本揭示案的各种实施例的绘示半导体装置200的透视图。半导体装置200可包括垂直soic,其中垂直soic使用接面电路(例如,混合接合接触电路)将第二半导体晶粒(例如,顶部半导体晶粒)连接至第一半导体晶粒(例如,底部半导体晶粒)。

133.具体而言,半导体装置200可包括第一半导体晶粒201(例如,底部半导体晶粒)及第二半导体晶粒202(例如,顶部半导体晶粒)。第二半导体晶粒202的侧表面可接合至第一半导体晶粒201,使得第二半导体晶粒202垂直于第一半导体晶粒201。术语“垂直”可理解为指“在分层方向上垂直”。即,第二半导体晶粒202的分层方向(例如,形成层的方向)(例如,图2中的x方向)可垂直于第一半导体晶粒201的分层方向(例如,图2中的z方向)。

134.第一半导体晶粒201及第二半导体晶粒202中的每一者可具有类似于图1中半导体晶粒100的结构的结构。因此,举例而言,第一半导体晶粒201及第二半导体晶粒202中的每

一者可包括金属特征116、密封环124、介电封装层360等。介电封装层260亦可形成于第二半导体晶粒202上,以便封装第二半导体晶粒202。介电封装层260可类似于图1中的介电封装层360。

135.半导体装置200亦可包括接面电路275,其用于连接第一半导体晶粒201与第二半导体晶粒202。第一半导体晶粒201可包括第一界面表面201a,其包括第一触点201b,而第二半导体晶粒202可包括第二界面表面202a(见图3b),其形成于第二半导体晶粒202的侧表面中且包括第二触点202b。接面电路275可包括金属层,其中金属层将第一触点201b连接至第二触点202b。第一触点201b及第二触点202b中的每一者可包括例如金属触点、金属接合衬垫、金属沟槽、金属阻障层及金属通孔中的一或多者。此外,第一触点201b及第二触点202b中的每一者可由铜、铜合金、铝、铝合金、或其一些组合物形成。用于第一触点201b及第二触点202b的其他适合导电金属材料在预期的揭示范畴内。

136.半导体装置200亦可包括接合层210,其用于将第二半导体晶粒202接合至第一半导体晶粒201。接面电路275可形成于接合层210中。接面电路275可包括例如形成于接合层210中的接合重分布层(redistribution layer,rdl)电路。接面电路275可包括接合衬垫275a,其接触第一半导体晶粒201的第一界面表面201a中的第一触点201b。接面电路275(例如,接合rdl电路)可由铜、铜合金、铝、铝合金、或其一些组合物形成。用于接面电路275的其他适合导电金属材料在预期的揭示范畴内。

137.图3a至图3c根据本揭示案的各种实施例绘示形成半导体装置200的方法的各种操作。在图3a中,可沿图3a中的虚线对第二半导体晶粒202进行平坦化,例如化学机械研磨(chemical mechanical polishing,cmp),借此在第二半导体晶粒202的侧表面中形成第二界面表面202a。应注意,可有其他方式来形成第二界面表面202a,例如沿图3a中的虚线对第二半导体晶粒202进行切割或切粒。沿图3a中的虚线的平坦化操作可导致移除介电封装层360及密封环124(见图1)的至少一部分、以及介电封装层260的一部分。

138.如图3b中所示,第二界面表面202a的形成(例如,通过对图3a中的第二半导体晶粒202进行平坦化)可导致在第二界面表面202a处形成(例如,暴露出)第二触点202b。第二触点202b可包括例如第二半导体晶粒202中已通过平坦化制程曝光的金属特征116。

139.如图3c中所示,可在第二界面表面202a上形成接合层210,用于将第二半导体晶粒202接合至第一半导体晶粒201。接合层210可类似于上文图1中描述的接合层310。

140.接面电路275可形成于接合层210中。接面电路275可包括例如形成于接合层210中的接合重分布层(redistribution layer,rdl)电路。接面电路275(例如,接合rdl电路)可包括接合衬垫275a,其接触第一半导体晶粒201的第一界面表面201a中的第一触点201b。具体而言,接面电路275可包括形成于接合层210的一或多个子层中的一或多个金属(例如,铜)布线层。

141.在接合层210中形成接面电路275的方法可类似于在半导体装置100的imd 114中形成金属特征116的方法。举例而言,在接合层210为多层接合层的实施例中,可在第二界面表面202a上沉积第一介电层且可在第一介电层中蚀刻第一孔。金属填充材料随后可沉积于第一介电层上以填充第一孔,接着可平坦化金属填充材料的表面。接着可在第一介电层上沉积第二介电层且可在第二介电层中蚀刻第二孔,以便接触形成于第一介电层中的金属填充材料(例如,接合通孔)。接着可在第二介电层上沉积金属填充材料,且接着可平坦化金属

填充材料的表面。可根据需要在第二介电层上形成额外介电层(带有金属),以完成接面电路275。

142.接合层210可包括沉积于第二界面表面202a上的接合材料。适合的接合材料可包括氧化硅或接合聚合物,例如环氧树脂、聚酰亚胺(pi)、苯并环丁烯(bcb)、及聚苯并口咢唑(pbo)。其他适合接合材料可在预期的揭示范畴内。具有接合衬垫275a的接面电路275可由与金属特征116相同的材料形成的导电特征。举例而言,接面电路275可包括钨(w)、铜(cu)、铜合金、铝(al)、铝合金、或其组合物、或类似物。用于连接接合衬垫的其他适合导电金属材料在预期的揭示范畴内。可通过使用混合接合制程将接合层210及接面电路275接合至第二界面表面202a。因此,接面电路275可熔合至第二界面表面202a中的第二触点202b(例如,暴露出的金属特征116),且接合层210可接合至介电封装层260及位于第二半导体晶粒202下方的介电层。

143.如图3c中进一步所示,第二半导体晶粒202可配置于第一半导体晶粒201上方,使得接合衬垫275a可与第一触点201b对准,接着第二半导体晶粒202降低至第一半导体晶粒201上,以便接合衬垫275a接触第一触点201b。接着可加热接合层210以使接合层210接合至第一半导体晶粒201的第一界面表面201a。

144.图4根据本揭示案的各种实施例绘示半导体晶粒群组350(例如,垂直半导体晶粒堆叠)。半导体晶粒群组350可包括数个堆叠半导体晶粒300a~300d。各个半导体晶粒300a~300d的元件可类似于上文参考图1描述的半导体晶粒100的元件。在一些实施例中,半导体晶粒群组350可以是垂直soic多晶粒堆叠,其可包括具有不同功能的不同半导体晶粒。堆叠半导体晶粒300a~300d可例如独立地选自特殊应用集成电路(application-specific integrated circuit,asic)晶片、模拟晶片、感测器晶片、无线及射频晶片、电压调整器晶片、记忆体晶片、或类似者。堆叠半导体晶粒300a~300d可使用混合接合制程彼此接合,混合接合制程可包括介电-介电接合制程、聚合物-聚合物接合制程、及/或金属-金属接合制程。

145.举例而言,半导体晶粒群组350可通过以下步骤形成:在载具399(例如,硅晶圆、蓝宝石晶圆、或任何其他适合载具,例如玻璃或塑料载具)(未显示)上形成(例如,配置)半导体晶粒300a、接着将半导体晶粒300b堆叠于半导体晶粒300a上使得半导体晶粒300b中的导电通孔150b接触接合层310a中的导电通孔335a。因此,半导体晶粒300b可接合至接合层310a。接着可将半导体晶粒300c堆叠于半导体晶粒300b上,使得半导体晶粒300c中的导电通孔150c接触接合层310b中的导电通孔335b,且半导体晶粒300c可接合至接合层310b。接着可将半导体晶粒300d堆叠于半导体晶粒300c上,使得半导体晶粒300d中的导电通孔150d接触接合层310c中的导电通孔335c,且半导体晶粒300d可接合至接合层310c。保护层359(例如,介电材料,例如氧化硅、氮化硅、氧氮化硅、或类似物)可沉积于半导体晶粒300d上。金属凸块(未显示)接着可连接至接合层310d中的金属衬垫326。

146.除了半导体晶粒群组350以外,亦可在载具上形成其他半导体晶粒群组。具体而言,可使用相同的制造制程形成(例如,同时形成)数个半导体晶粒群组350,因此可包括类似的元件。或者,多个半导体晶粒群组可形成于分开的载具上,且可包括不同的元件。

147.图5根据各种实施例绘示堆叠半导体晶粒群组400(例如,垂直半导体晶粒堆叠)。堆叠半导体晶粒群组400可包括数个半导体晶粒群组350a、350b,其中各者在结构及功能上

可类似于图4中的半导体晶粒群组350。

148.如图5中所示,数个半导体晶粒群组350a、350b可自载具399移除,然后旋转90

°

,并通过载具接合层498接合至另一载具499。具体而言,数个半导体晶粒群组350a、350b的一侧可接合至载具499,使得数个半导体晶粒群组350a、350b可垂直配置于载具499上。在一些实施例中,载具接合层498可以是垂直熔合凸块或类似物。

149.接着,数个半导体晶粒群组350a、350b可由介电封装层460封装,其可类似于图1中的介电封装层360。介电封装层460可使用任何适合的沉积方法沉积,且可包括任何适合的介电材料,例如氧化硅、氮化硅、或类似物。其他适合介电材料在预期的揭示范畴内。

150.图6根据各种实施例绘示半导体装置500。半导体装置500可包括垂直soic多晶粒堆叠,其可包括具有不同功能的不同晶粒。

151.半导体装置500可包括接合至第一半导体晶粒501(例如,底部半导体晶粒)的堆叠半导体晶粒群组400(在移除载具499及载具接合层498之后)。具体而言,堆叠半导体晶粒群组400的侧表面可接合至第一半导体晶粒501,使得数个半导体晶粒群组350a、350b垂直于第一半导体晶粒501。数个半导体晶粒群组350a、350b中的每一者可包括数个半导体晶粒。堆叠半导体晶粒群组400可配置于第一半导体晶粒501上,使得数个半导体晶粒群组350a、350b的侧表面(例如,多个半导体晶粒群组350a、350b中的半导体晶粒的侧表面)接合至第一半导体晶粒501。

152.半导体装置500亦可包括接面电路375,可使用接面电路375以将第一半导体晶粒501连接至数个半导体晶粒中的第二半导体晶粒502的。第一半导体晶粒501可在结构及功能上类似于上述半导体晶粒100。

153.半导体装置500亦可包括用于将堆叠半导体晶粒群组400接合至第一半导体晶粒501的接合层510(例如,接合结构)。接合层510可最初形成于堆叠半导体晶粒群组400的侧表面上,且一或多个接面电路375(例如,重分布层(redistribution layer,rdl)电路)形成于接合层510中。接面电路375可将第一半导体晶粒501电性连接至堆叠半导体晶粒群组400中的一或多个第二半导体晶粒502。具体而言,在堆叠半导体晶粒群组400中半导体晶粒中的每一者可作为第二半导体晶粒502通过特定的接面电路375连接至第一半导体晶粒501,如图6中所示。

154.图7a至图7d根据各种实施例绘示制造半导体装置500的方法。

155.如图7a中所示,可对图5中所示的堆叠半导体晶粒群组400执行平坦化制程,例如化学机械平坦化(chemical mechanical planarization,cmp)。具体而言,可在堆叠半导体晶粒群组400中数个半导体晶粒群组350a、350b及介电封装层460上执行平坦化。在平坦化中,可研磨数个半导体晶粒群组350a、350b以移除介电封装层360及密封环124(见图1)的至少一部分、以及介电封装层260的一部分。在平坦化之后,金属特征116可暴露于数个半导体晶粒群组350a、350b的暴露侧表面的表面上。

156.如图7b中所示,第二半导体晶粒502的第二界面表面502a可形成于数个半导体晶粒群组350a、350b的侧表面中,这些侧表面通过平坦化堆叠半导体晶粒群组400而形成。应注意,可有其他方式来形成第二界面表面502a,例如通过切割、切粒等。

157.如图7b中所示,第二半导体晶粒502的第二界面表面502a可包括层间介电质312、金属间介电质314及接合层310。此外,可在第二界面表面502a处形成(例如,暴露出)一或多

个第二触点502b。第二触点502b可包括例如钨触点502b-1、铜沟槽502b-2、组合钨触点/铜沟槽502b-3、组合铜沟槽/通孔/沟槽502b-4、铜通孔502b-5、组合铜沟槽/通孔502b-6、铝衬垫502b-7、组合铝衬垫/铜沟槽502b-8、以及组合接合金属/铝衬垫502b-9。

158.如图7c中所示,可在通过图7a中的平坦化制程形成的堆叠半导体晶粒群组400的平坦化侧表面上形成接合层510。接合层510可类似于上文图1中描述的接合层310。具体而言,用于接合层510的适合接合材料可包括氧化硅或接合聚合物,例如环氧树脂、聚酰亚胺(pi)、苯并环丁烯(bcb)、及聚苯并口咢唑(pbo)。其他适合接合材料可在预期的揭示范畴内。可形成接合层510以便将堆叠半导体晶粒群组400中的数个半导体晶粒群组350a、350b接合至第一半导体晶粒501。

159.接合层510可在其中形成接面电路375,其可包括一或多个金属层,用于将第二半导体晶粒502的第二界面表面502a中的第二触点502b连接至第一半导体晶粒501的第一界面表面501a中的第一触点501b。接面电路375可包括例如形成于接合层510中的接合重分布层(redistribution layer,rdl)电路,且接面电路375(例如,接合rdl电路)可包括接合衬垫375a。接面电路375可包括形成于接合层510的一或多个子层中的一或多个金属(例如,铜)布线层。具体而言,接面电路的布线层可由与金属特征116相同的材料形成,且可包括钨(w)、铜(cu)、铜合金、铝(al)、铝合金、或其组合物、或类似物。

160.如图7d中所示,第一半导体晶粒501可配置位于堆叠半导体晶粒群组400上方,以便第一触点501b可与接合衬垫375a对准,且第一半导体晶粒501可降低至堆叠半导体晶粒群组400上,以便第一触点501b接触接合衬垫375a。接着可使用任何适合接合制程(例如混合接合制程)将接合层510接合至第一半导体晶粒501的第一界面表面501a。

161.接着可将第一半导体晶粒501的半导体基板薄化,以暴露出第一半导体晶粒501中的一或多个金属特征(例如,通孔、互连件等)。可在第一半导体晶粒501中暴露的金属特征上形成介电层及电触点586,例如焊料凸块。接着可移除载具499以形成图6中所示的完整半导体装置500。

162.图8根据一或多个实施例提供形成半导体装置500的方法的流程图。方法可包括接合堆叠半导体晶粒以形成半导体晶粒群组(图4)的步骤891、旋转数个半导体晶粒群组并将其接合至载具(图5)的步骤892、在数个半导体晶粒群组周围形成(例如,通过沉积)介电封装层以形成堆叠半导体晶粒群组(图5)的步骤893、平坦化/研磨堆叠半导体晶粒群组(图7a)的步骤894、沉积接合层及具有接合衬垫的接面电路(图7b及图7c)的步骤895、将第一半导体晶粒接合至堆叠半导体晶粒群组(图7d)的步骤896、及在第一半导体晶粒的一或多个金属特征(例如通孔、互连件等)上形成一或多个电触点(例如,焊料凸块)(图7d)的步骤897。

163.图9根据各种实施例绘示使用4个例示性接面电路375-1至375-4(例如,接合层金属走线)的位置及配置。如图9中所示,接面电路375-1可包括连接至第二触点502b-8(例如,组合铝衬垫/铜沟槽)的接合通孔375c、形成于第二界面表面的无金属区域650a(例如,硅区域)上方的接合衬垫375a、及将接合通孔375c连接至接合衬垫375a的接合沟槽375b。接面电路375-2可包括连接至第二触点502b-8(例如,组合铝衬垫/铜沟槽)的接合通孔375c、形成于非金属区域614(例如,金属间介电质(intermetal dielectric,imd))上方的接合衬垫375a、及将接合通孔375c连接至接合衬垫375a的接合沟槽375b。接面电路375-3可包括连接

至第二触点502b-6(例如,组合铜沟槽/通孔)的接合通孔375c、形成于第二界面表面的无金属区域650b(例如,硅区域)上方的接合衬垫375a、及将接合通孔375c连接至接合衬垫375a的接合沟槽375b。接面电路375-4可包括连接至第二触点502b-6的接合通孔375c(例如,组合铜沟槽/通孔)、形成于非金属区域614(例如,imd)上方的接合衬垫375a、及将接合通孔375c连接至接合衬垫375a的接合沟槽375b。在接面电路375-1、375-2、375-3、及375-4中的每一者中,接合沟槽375b可在第一方向(例如,x方向)上纵向延伸。接合沟槽375b在第一方向上的长度可大于接合衬垫375a在第一方向上的长度。如图9(以及下文的图10a至图10d)中所示,在接面电路375-1、375-2、375-3、及375-4中的每一者中,接合沟槽375b在第一方向上的长度可大于接合通孔375c在第一方向上的长度。此外,接合衬垫375a在第一方向上的长度可大于接合通孔375c在第一方向上的长度。接合沟槽375b在垂直于第一方向(例如,x方向)的第二方向(例如,y方向)上的宽度可小于接合衬垫375a在第二方向上的宽度,且可大于接合通孔375c在第二方向上的宽度。此外,接合衬垫375a在第二方向上的宽度可大于接合通孔375c在第二方向上的宽度。接合沟槽375b在垂直于第一方向(例如,x方向)及第二方向(例如,y方向)的第三方向(例如,z方向)上的厚度可与接合通孔375c及接合衬垫375a的厚度基本上相同。

164.图10a至图10d根据各种实施例绘示例示性接面电路375-1至375-4(例如,接合层金属走线)中的每一者的半透明平面图(x及y方向)以及相应垂直截面图(x及z方向)。具体而言,图10a的垂直截面图图示分别在形成于第二界面表面502a上的接合层510(例如,多层接合层)的第一接合层510a、第二接合层510b及第三接合层510c中形成的接面电路375-1的接合衬垫375a、接合沟槽375b及接合通孔375c。图10b的垂直截面图图示分别在形成于第二界面表面502a上的接合层510的第一接合层510a、第二接合层510b及第三接合层510c中形成的接面电路375-2的接合衬垫375a、接合沟槽375b及接合通孔375c。图10c的垂直截面图图示分别在形成于第二界面表面502a上的接合层510的第一接合层510a、第二接合层510b及第三接合层510c中形成的接面电路375-3的接合衬垫375a、接合沟槽375b及接合通孔375c。图10d的垂直截面图图示分别在形成于第二界面表面502a上的接合层510的第一接合层510a、第二接合层510b及第三接合层510c中形成的接面电路375-4的接合衬垫375a、接合沟槽375b及接合通孔375c。参考图10a至图10d,第一平面(例如,x-y平面)中的接合通孔375c的横截面形状可基本上为圆形,而接合沟槽375b及接合衬垫375a的横截面形状可基本上为矩形。然而,接合衬垫375a、接合沟槽375b及接合通孔375c的额外横截面形状在预期的揭示范畴内。

165.图11根据各种实施例绘示接面电路375(例如,接合层金属走线)的透视图。图11中接面电路375的配置仅用于说明目的而并不意欲为限制性的。接合衬垫375a、接合沟槽375b及接合通孔375c中的每一者的高度(例如,z方向上的厚度)可基本上等于形成接面电路375的接合层的介电层的高度。

166.图12根据各种实施例绘示半导体装置800的分解图。如图12中所示,半导体装置800包括形成于第一半导体晶粒801的第一界面表面801a上的数个第一触点801b、及形成于堆叠半导体晶粒群组400中的数个第二半导体晶粒802。半导体装置800亦包括数个接面电路375,接面电路375形成于接合层810中且将数个第二半导体晶粒802中的第二触点(未显示)连接至数个第一触点801b。

167.应注意,尽管图7b可参考半导体装置500进行描述,但图7b可同样适用于半导体装置200及半导体装置800。因此,举例而言,第二界面表面202a及第二界面表面802a可具有与图7b中所述的第二界面表面502a相同的配置。此外,尽管有时可参考半导体装置500来描述图9至图11,但图9至图11可同样适用于半导体装置200及半导体装置800。因此,举例而言,在半导体装置200及半导体装置800中,接面电路375的配置以及接面电路375相对于第二界面表面202a及802a的位置可与上文在图9至图11中所描述的相同。

168.图13根据各种实施例绘示制造半导体装置200、500、800的方法的流程图。方法的步骤1310包括形成第一半导体晶粒201、501、801。步骤1320包括形成第二半导体晶粒202、502、802以及在第二半导体晶粒202、502、802的侧表面上形成接合层210、510、810。步骤1330包括在接合层210、510、810中形成接面电路275、375。步骤1340包括将接合层210、510、810接合至第一半导体晶粒201、501、801,使得第二半导体晶粒202、502、802垂直于第一半导体晶粒201、501、801,且接面电路275、375将第一半导体晶粒201、501、801连接至第二半导体晶粒202、502,802。

169.图14a至图14i根据各种实施例绘示形成接面电路275、375的方法中的各种操作及可能形成的中间结构。图14a图示中间结构,其中第一接合层510a可形成于第二界面表面502a上。第一接合层510a可包括例如氧化硅或接合聚合物,例如环氧树脂、聚酰亚胺(pi)、苯并环丁烯(bcb)、及聚苯并口咢唑(pbo)。其他适合接合层材料可在预期的揭示范畴内。第一接合层510a可例如通过化学气相沉积(chemical vapor deposition,cvd)、电浆增强cvd(plasma-enhanced cvd,pecvd)、低压化学气相沉积(low pressure chemical vapor deposition,lpcvd)、物理气相沉积(physical vapor deposition,pvd)或原子层沉积(atomic layer deposition,ald)形成。

170.可在第一接合层510a上形成可选的第一蚀刻终止层511a。第一蚀刻终止层511a可包括例如sic、sin等。其他适合蚀刻终止材料可在预期的揭示范畴内。第一蚀刻终止层511a亦可例如通过化学气相沉积(chemical vapor deposition,cvd)、电浆增强cvd(plasma-enhanced cvd,pecvd)、低压化学气相沉积(low pressure chemical vapor deposition,lpcvd)、物理气相沉积(physical vapor deposition,pvd)或原子层沉积(atomic layer deposition,ald)形成。

171.图14b根据各种实施例绘示中间结构,包括形成第一孔512在第一接合层510a及第一蚀刻终止层511a中。第一孔512可形成于第二界面表面502a中的组合铝衬垫/铜沟槽502b-8(例如,第二触点502b)上方。尽管这个实例可包括组合铝衬垫/铜沟槽502b-8,但在图14a至图14i的方法中可使用任何第二触点(例如,图7b中的第二触点502b-1至502b-9中的任意者)。

172.举例而言,第一孔512可具有z方向上的圆形截面,且圆形截面可具有小于组合铝衬垫/铜沟槽502b-8的大小(例如,x方向上的长度及y方向上的长度)的直径。因此,在平面图中,第一孔512可完全在组合铝衬垫/铜沟槽502b-8的表面的外周边内。亦即,平面图中组合铝衬垫/铜沟槽502b-8的表面积可大于第一孔512的横截面面积(例如,见图9中的接面电路375-1)。

173.第一孔512可例如通过使用光学微影制程形成。光学微影制程可包括在第一蚀刻终止层511a上形成经图案化光阻遮罩(未显示)、及穿过光阻遮罩中的开口来蚀刻(例如,湿

式蚀刻、干式蚀刻等)经曝光第一蚀刻终止层511a及第一接合层510a,借此暴露出组合铝衬垫/铜沟槽502b-8的表面。随后可通过灰化、溶解光阻遮罩或在蚀刻制程期间消耗光阻遮罩来移除光阻遮罩。

174.图14c根据各种实施例绘示中间结构,包括形成接合通孔375c于第一孔512中。接合通孔375c可包括金属材料,其可包括例如钨(w)、铜(cu)、铜合金、铝(al)、铝合金、或其组合物、或类似物。用于接合通孔375c的其他适合导电金属材料在预期的揭示范畴内。举例而言,可通过在第一蚀刻终止层511a上形成金属材料以使其填充第一孔512来形成接合通孔375c。金属材料可经由沉积制程形成于第一孔512中,或可在第一孔512中生长。金属材料可例如通过化学气相沉积(chemical vapor deposition,cvd)、电浆增强cvd(plasma-enhanced cvd,pecvd)、低压化学气相沉积(low pressure chemical vapor deposition,lpcvd)、物理气相沉积(physical vapor deposition,pvd)或原子层沉积(atomic layer deposition,ald)来沉积。接着可执行例如化学机械研磨(chemical mechanical polishing,cmp)的平坦化步骤,以便自第一蚀刻终止层511a的表面移除金属材料,且使得接合通孔375c的表面与第一蚀刻终止层511a的表面基本上共面。

175.图14d图示一中间结构,其中第二接合层510b已形成于第一蚀刻终止层511a上(或者,若第一蚀刻终止层511a不存在,则形成于第一接合层510a上)。第二接合层510b可包括例如氧化硅或接合聚合物,例如环氧树脂、聚酰亚胺(pi)、苯并环丁烯(bcb)、及聚苯并口咢唑(pbo)。其他适合接合层材料可在预期的揭示范畴内。第二接合层510b可例如通过化学气相沉积(chemical vapor deposition,cvd)、电浆增强cvd(plasma-enhanced cvd,pecvd)、低压化学气相沉积(low pressure chemical vapor deposition,lpcvd)、物理气相沉积(physical vapor deposition,pvd)或原子层沉积(atomic layer deposition,ald)形成。

176.可选的第二蚀刻终止层511b可形成于第二接合层510b上。第二蚀刻终止层511b可包括例如sic、sin等。其他适合蚀刻终止材料可在预期的揭示范畴内。第二蚀刻终止层511b亦可例如通过化学气相沉积(chemical vapor deposition,cvd)、电浆增强cvd(plasma-enhanced cvd,pecvd)、低压化学气相沉积(low pressure chemical vapor deposition,lpcvd)、物理气相沉积(physical vapor deposition,pvd)或原子层沉积(atomic layer deposition,ald)形成。

177.图14e根据各种实施例绘示中间结构,包括形成第二孔513于第二接合层510b及第二蚀刻终止层511b中。第二孔513可形成于接合通孔375c上方,且可具有例如在z方向上的矩形截面,且矩形截面在y方向上的宽度及在x方向上的长度的各者可大于接合通孔375c的直径。因此,在平面图中,接触通孔375c的表面可完全在第二孔513表面的外周边内(例如,见图9中的接面电路375-1)。

178.第二孔513可例如通过使用光学微影制程形成。光学微影制程可包括在第二蚀刻终止层511b上形成经图案化光阻遮罩(未显示),并穿过光阻遮罩中的开口来蚀刻(例如,湿式蚀刻、干式蚀刻等)经曝光第二蚀刻终止层511b及第二接合层510b,借此暴露出接合通孔375c的表面。随后可通过灰化、溶解光阻遮罩或在蚀刻制程期间消耗光阻遮罩来移除光阻遮罩。

179.图14f根据各种实施例绘示中间结构,包括形成接合沟槽375b于第二孔513中。接合沟槽375b可包括金属材料,其可包括例如钨(w)、铜(cu)、铜合金、铝(al)、铝合金、或其组

合物、或类似物。用于接合沟槽375b的其他适合导电金属材料在预期的揭示范畴内。举例而言,可通过在第二蚀刻终止层511b上沉积金属材料以使其填充第二孔513来形成接合沟槽375b。金属材料可例如通过化学气相沉积(chemical vapor deposition,cvd)、电浆增强cvd(plasma-enhanced cvd,pecvd)、低压化学气相沉积(low pressure chemical vapor deposition,lpcvd)、物理气相沉积(physical vapor deposition,pvd)或原子层沉积(atomic layer deposition,ald)来沉积。接着可执行例如化学机械研磨(chemical mechanical polishing,cmp)的平坦化步骤,以便自第二蚀刻终止层511b的表面移除金属材料,且使得接合沟槽375b的表面与第二蚀刻终止层511b的表面基本上共面。

180.图14g图示一中间结构,其中第三接合层510c已形成于第二蚀刻终止层511b上(或者,若第二蚀刻终止层511b不存在,则形成于第二接合层510b上)。第三接合层510c可包括例如氧化硅或接合聚合物,例如环氧树脂、聚酰亚胺(pi)、苯并环丁烯(bcb)、及聚苯并口咢唑(pbo)。其他适合接合层材料可在预期的揭示范畴内。第三接合层510c可例如通过化学气相沉积(chemical vapor deposition,cvd)、电浆增强cvd(plasma-enhanced cvd,pecvd)、低压化学气相沉积(low pressure chemical vapor deposition,lpcvd)、物理气相沉积(physical vapor deposition,pvd)或原子层沉积(atomic layer deposition,ald)形成。第三接合层510c的上表面可用作与第一半导体晶粒501接合的界面(例如,见图7d)。

181.图14h根据各种实施例绘示中间结构,包括形成第三孔514于第三接合层510c中。第三孔514可形成于接合沟槽375b上方,且可具有例如z方向上的矩形截面。矩形截面在y方向上的宽度可大于接合沟槽375b的宽度,而x方向上的长度可小于接合沟槽375b的长度(例如,见图9中的接面电路375-1)。

182.第三孔514可例如通过使用光学微影制程形成。光学微影制程可包括在第三接合层510c上形成经图案化光阻遮罩(未显示),并穿过光阻遮罩中的开口来蚀刻(例如,湿式蚀刻、干式蚀刻等)经曝光第三接合层510c,借此暴露出接合沟槽375b的表面。随后可通过灰化、溶解光阻遮罩或在蚀刻制程期间消耗光阻遮罩来移除光阻遮罩。

183.图14i根据各种实施例绘示中间结构,包括形成于第三孔514中的接合衬垫375a。接合衬垫375a可包括金属材料,其可包括例如钨(w)、铜(cu)、铜合金、铝(al)、铝合金、或其组合物、或类似物。用于接合衬垫375a的其他适合导电金属材料在预期的揭示范畴内。举例而言,可通过在第三接合层510c上沉积金属材料以使其填充第三孔514来形成接合衬垫375a。金属材料可例如通过化学气相沉积(chemical vapor deposition,cvd)、电浆增强cvd(plasma-enhanced cvd,pecvd)、低压化学气相沉积(low pressure chemical vapor deposition,lpcvd)、物理气相沉积(physical vapor deposition,pvd)或原子层沉积(atomic layer deposition,ald)来沉积。接着可执行例如化学机械研磨(chemical mechanical polishing,cmp)的平坦化步骤,以便自第三接合层510c的上表面移除金属材料,从而使接合衬垫375a的表面与第三接合层510c的表面基本上共面。

184.在形成接面电路275、375之后,包括第一接合层510a、第二接合层510b及第三接合层510c的接合层510、以及接面电路375可接着通过使用混合接合制程接合至第二界面表面502a。因此,接面电路375可熔合至第二界面表面502a中的组合铝衬垫/铜沟槽502b-8(例如,第二触点502b),且接合层510可接合至介电封装层460及第二半导体晶粒502下方的介电层。

185.图15根据各种实施例绘示形成接面电路275、375的方法的流程图。方法包括在第二界面表面上形成第一接合层、且在第一接合层中形成第一孔以暴露出第二界面表面中的第二触点的步骤1510;在第一孔中沉积金属材料以形成接合通孔、且平坦化金属材料的步骤1520;在第一接合层上形成第二接合层、且在第二接合层中形成第二孔以暴露出接合通孔的表面的步骤1530;在第二孔中沉积金属材料以形成接合沟槽、且平坦化金属材料的步骤1540;在第二接合层上形成第三接合层、且在第三接合层中形成第三孔以暴露出接合沟槽的表面的步骤1550;在第三孔中沉积金属材料以形成接合衬垫、且平坦化金属材料的步骤1560。

186.参考图1至图15,在各种实施例中,提供半导体装置200、500、800,其中半导体装置200、500、800可包括第一半导体晶粒201、501、801。半导体装置200、500、800还可包括第二半导体晶粒202、502、802,第二半导体晶粒202、502、802包括接合至第一半导体晶粒201、501、801的侧表面,使得第二半导体晶粒202、502、802可垂直于第一半导体晶粒201、501、801的侧表面。半导体装置200、500、800还可包括接面电路275、375,用于将第一半导体晶粒201、501、801连接至第二半导体晶粒202、502、802。

187.在一个实施例中,第一半导体晶粒201、501、801可包括第一界面表面201a、501a、801a,其中第一界面表面201a、501a、801a包括第一触点201b、501b、801b;第二半导体晶粒202、502、802可包括第二界面表面202a、502a、802a,其中第二界面表面202a、502a、802a形成于侧表面中且包括第二触点202b、502b、802b;以及接面电路275、375可包括金属层,其中金属层将第一触点201b、501b、801b连接至第二触点202b、502b、802b。在一个实施例中,第二触点202b、502b、802b可包括金属触点、金属接合衬垫、金属沟槽、金属阻障层及金属通孔中的至少一者。在一个实施例中,半导体装置200、500、800可进一步包括接合层210、510、810,用于将第二半导体晶粒202、502、802接合至第一半导体晶粒201、501、801,接面电路275、375形成于接合层210、510、810中。在一个实施例中,接面电路275、375可包括接合重分布层电路,接合重分布层电路可形成于接合层210、510、810中。在一个实施例中,接面电路275、375可包括接合衬垫275a、375a,接合衬垫275a、375a接触第一半导体晶粒201、501、801的第一界面表面201a、501a、801a中的第一触点201b、501b、801b。

188.参考图1至图15,可提供半导体装置200、500、800,其中半导体装置200、500、800可包括第一半导体晶粒201、501、801以及数个半导体晶粒群组350a、350b,其中数个半导体晶粒群组350a、350b可堆叠在一起并接合至第一半导体晶粒201、501、801的侧表面,使得数个半导体晶粒群组350a、350b垂直于第一半导体晶粒201、501、801,数个半导体晶粒群组350a、350b中的每一者具有堆叠在一起的数个半导体晶粒300a~300d、用于将数个半导体晶粒300a~300d接合在一起的接合结构310、及形成于接合结构310中的用于电性耦合数个半导体晶粒300a~300d的导电通孔150b、150c、150d、及用于将第一半导体晶粒201、501、801连接至数个半导体晶粒300a~300d中的第二半导体晶粒202、502、802的的接面电路275、375。

189.在一个实施例中,第一半导体晶粒201、501、801可包括第一界面表面201a、501a、801a,第一界面表面201a、501a、801a包括第一触点201b、501b、801b;第二半导体晶粒202、502、802可包括第二界面表面202a、502a、802a,第二界面表面202a、502a、802a形成于数个半导体晶粒群组350a、350b的侧表面中且具有第二触点202b、502b、802b;且接面电路275、

375可包括将第一触点201b、501b、801b连接至第二触点202b、502b、802b的金属层。在一个实施例中,第二触点202b、502b、802b可包括金属触点、金属接合衬垫、金属沟槽、金属阻障层及金属通孔中的至少一者。在一个实施例中,半导体装置200、500、800可包括接合层210、510、810,用于将数个半导体晶粒群组350a、350b接合至第一半导体晶粒201、501、801;形成于接合层210、510、810中的接面电路275、375。在一个实施例中,接面电路275、375可包括接合重分布层电路,其中接合重分布层电路可形成于接合层210、510、810中。在一个实施例中,接面电路275、375可包括用于接触第一半导体晶粒201、501、801的第一界面表面201a、501a、801a中的第一触点201b、501b、801b的接合衬垫275a、375a。在一个实施例中,接合衬垫275a、375a可形成于第二半导体晶粒202、502、802的第二界面表面202a、502a、802a的无金属区域中。在一个实施例中,接面电路可进一步包括用于接触第二触点202b、502b、802b的接合通孔375c及用于将接合通孔375c连接至接合衬垫275a、375a的接合沟槽375b。在一个实施例中,接合层210、510、810可包括数个层,且可在数个层的分离层中形成接合通孔375c、接合沟槽375b及接合衬垫275a、375a。

190.参考图1至图15,可提供接面电路275、375。接面电路375可包括接合沟槽375b,其包括第一表面及与第一表面相对的第二表面,以及第一末端及与第一末端相对的第二末端。接面电路375还可包括接合衬垫375a,其形成于接合沟槽375b的第一表面上及接合沟槽375b的第一末端处,其中接合衬垫375a配置以电性耦合接面电路375与第二晶粒202、502、802。接面电路375还可包括接合通孔375c,其形成于接合沟槽375b的第二表面上及接合沟槽375b的第二末端处,其中接合通孔375c配置以电性耦合接面电路375与第一晶粒201、501、801。

191.在一实施例中,接合沟槽375b可在第一方向上纵向延伸,且接合沟槽375b在第一方向上的长度大于接合衬垫375a在第一方向上的长度。在一个实施例中,接合沟槽375b在第一方向上的长度大于接合通孔375c在第一方向上的长度。在一实施例中,接合衬垫375a在第一方向上的长度大于接合通孔375c在第一方向上的长度。在一实施例中,接合沟槽375b在垂直于第一方向的第二方向上的宽度小于接合衬垫375a在第二方向上的宽度。在一实施例中,接合沟槽375b在第二方向上的宽度大于接合通孔375c在第二方向上的宽度。在一实施例中,接合衬垫375a在第二方向上的宽度大于接合通孔375c在第二方向上的宽度。在一实施例中,接合沟槽375b在垂直于第一方向及第二方向的第三方向上的厚度与接合衬垫375a在第三方向上的厚度基本上相同。在一实施例中,接合沟槽375b在第三方向上的厚度与接合通孔375c在第三方向上的厚度基本上相同。在一实施例中,接合衬垫375a在第三方向上的厚度与接合通孔375c在第三方向上的厚度基本上相同。在一实施例中,接合通孔375c在第一平面中可包括基本上圆形截面,且接合沟槽375b及接合衬垫375a中的每一者在第一平面中包含基本上矩形截面。在一实施例中,接合沟槽375b、接合衬垫375a及接合通孔375c中的每一者可包括铜、铜合金、铝及铝合金中的至少一者。在一实施例中,接合沟槽375b、接合衬垫375a及接合通孔375c可包括接合重分布层电路的金属线路层。

192.参考图1至图15,可提供一种制造半导体装置200、500、800的方法,其中方法可包括以下操作:形成第一半导体晶粒201、501、801,形成第二半导体晶粒202、502、802,以及在第二半导体晶粒202、502、802的侧表面上形成接合层210、510,810,在接合层210、510、810中形成接面电路275、375,将接合层210、510、810接合至第一半导体晶粒201、501、801,使得

第二半导体晶粒202、502、802垂直于第一半导体晶粒201、501、801,且接面电路275、375将第一半导体晶粒201、501、801连接至第二半导体晶粒202、502、802。在一个实施例中,形成第一半导体晶粒201、501、801包括形成第一半导体晶粒201、501、801以包括第一界面表面201a、501a、801a,其包括第一触点201b、501b、801b;形成第二半导体晶粒202、502、802包括形成第二半导体晶粒202、502,802以包括第二界面表面202a、502a、802a,其形成于侧表面中且包括第二触点202b、502b、802b;以及形成接面电路275、375包括形成将第一触点201b、501b、801b连接至第二触点202b、502b、802b的金属层。在一个实施例中,形成第二半导体晶粒202、502、802包括形成第二触点202b、502b、802b以包括金属触点、金属接合衬垫、金属沟槽、金属阻障层及金属通孔中的至少一者。在一个实施例中,形成接面电路275、375包括在接合层210、510、810中形成接合重分布层电路。在一个实施例中,形成接面电路275、375包括接合衬垫275a、375a,其接触第一半导体晶粒201、501、801的第一界面表面201a、501a、801a中的第一触点201b、501b、801b。

193.以上概略说明了本揭示案数个实施例的特征,使所属技术领域内具有通常知识者对于本揭示案可更为容易理解。任何所属技术领域内具有通常知识者应了解到本揭示案可轻易作为其他结构或制程的变更或设计基础,以进行相同于本揭示案实施例的目的及/或获得相同的优点。任何所属技术领域内具有通常知识者亦可理解与上述等同的结构并未脱离本揭示案的精神及保护范围内,且可在不脱离本揭示案的精神及范围内,可作更动、替代与修改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。