技术特征:

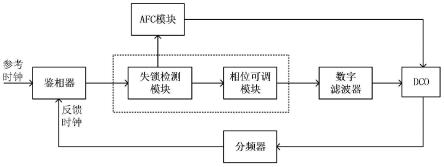

1.一种相位可调的adpll电路,其特征在于,包括鉴相器、失锁检测模块、相位可调模块、数字滤波器、dco、afc模块和分频器;其中,所述鉴相器、所述失锁检测模块、所述相位可调模块、所述数字滤波器和所述dco依次相连,所述失锁检测模块、所述afc和所述dco组成环路,所述dco、所述分频器和所述鉴相器组成环路;所述鉴相器用于提取参考时钟与反馈时钟之间的相位误差;所述失锁检测模块判断环路是否实现锁定;所述相位可调模块用于调整所述鉴相器输出的相位误差;所述数字滤波器用于滤除相位误差中的高频分量;所述dco产生与频率控制字相对应的时钟信号;所述afc模块用于自动频率校准;所述分频器将所述dco产生的时钟信号进行分频,产生反馈时钟至所述鉴相器。2.如权利要求1所述的相位可调的adpll电路,其特征在于,所述失锁检测模块包括d触发器、判断电路、模128计数器、二选一数据选择器mux1;由8位整数、32位小数构成的相位差信号pd[39:0]首先经过d触发器对其进行采样,得到采样信号pd_q[39:0];然后取其整数位pd_q[39:32]输入到判断电路,若pd_q[39:32]大于2,所述判断电路输出值为1的控制信号flag_afc到所述afc模块,表明相位差信号需转到afc模块进行处理;若pd_q[39:32]不大于2,所述判断电路输出值为0的控制信号flag_afc到afc模块,表明相位差信号无需转到afc模块进行处理;若pd_q[39:32]不等于0,所述判断电路输出值为0的计数器清零信号flag_clr至模128计数器,对所述模128计数器进行清零;若pd_q[39:32]等于0,所述判断电路输出值为1的计数器清零信号flag_clr至模128计数器,所述模128计数器正常计数;若模128计数器计满128个周期,则输出值为1的锁定信号lock,表明环路已经锁定,同时lock信号控制二选一数据选择器mux1选择数字地信号gnd作为所述模128计数器的时钟输入。3.如权利要求2所述的相位可调的adpll电路,其特征在于,所述判断电路由数值比较器1和数值比较器2构成;采样信号的整数位pd_q[39:32]分别连接数值比较器1和数值比较器2的一端,所述数值比较器1的另一端连接固定数值8'h2,数值比较器1的输出端输出控制信号flag_afc,连接到所述afc模块;数值比较器2的另一端连接固定数值8'h0,数值比较器2的输出端输出计数器清零信号flag_clr,连接到所述模128计数器的清零端clr。4.如权利要求3所述的相位可调的adpll电路,其特征在于,所述d触发器的数据端d连接相位差信号pd[39:0],时钟端clk连接全局时钟ckr,复位端reset连接复位信号reset,输出端q输出至所述判断电路;所述模128计数器的清零端clr连接数值比较器2的输出端,所述模128计数器的时钟端clk连接二选一数据选择器mux1的输出端,进位端c输出锁定信号lock,分别连接到二选一数据选择器mux1的控制端和二选一数据选择器mux2的控制端;所述二选一数据选择器mux1的数据端d0连接全局时钟ckr,数据端d1连接数字地信号gnd,输出端连接所述模128计数器的时钟端clk,控制端连接所述模128计数器的进位端c。5.如权利要求4所述的相位可调的adpll电路,其特征在于,所述相位可调模块包括二选一数据选择器mux2、加法器和四选一数据选择器mux3;经过所述d触发器采样得到的采样信号pd_q[39:0]同时会输入到所述相位可调模块进行处理,由四选一数据选择器mux3的控

制信号s1s0从输入的四路数据中选出一路数据与采样信号pd_q[39:0]进行相加,得到的和信号输入到二选一数据选择器mux2的d1端;二选一数据选择器mux2的d0端为采样信号pd_q[39:0],二选一数据选择器mux2的控制信号为锁定信号lock,当lock值为1时选择d1端的数据输出,即为调整后的相位差信号pd_adj[39:0]。6.如权利要求5所述的相位可调的adpll电路,其特征在于,所述四选一数据选择器mux3的数据端d00连接固定数值40'h1,数据端d01连接固定数值40'h2,数据端d10连接固定数值40'h4,数据端d11连接固定数值40'h8,输出端连接到加法器的一端,控制端s1、s0分别连接控制信号s1、s0;所述加法器的一个输入端连接d触发器的输出端q,另一个输入端连接四选一数据选择器mux3的输出端,所述加法器的输出端连接二选一数据选择器mux2的数据端d1;所述二选一数据选择器mux2的数据端d0连接d触发器的输出端q,数据端d1连接加法器的输出端,输出端输出调整后的相位差信号pd_adj[39:0],控制端连接模128计数器的进位端c。

技术总结

本发明公开一种相位可调的ADPLL电路,属于数字电路领域,包括鉴相器、失锁检测模块、相位可调模块、数字滤波器、DCO、AFC模块和分频器;其中,所述鉴相器、所述失锁检测模块、所述相位可调模块、所述数字滤波器和所述DCO依次相连,所述失锁检测模块、所述AFC和所述DCO组成环路,所述DCO、所述分频器和是鉴相器组成环路。本发明通过在鉴相器后添加失锁检测模块和相位可调模块,所述失锁检测模块用于产生锁定信号Lock,所述相位可调模块用于产生调整后的相位差信号PD_adj,实现了在ADPLL内部环路中进行相位可调以及对环路是否锁定的监测,而且本发明的电路结构简单,容易实现,可复用性高。可复用性高。可复用性高。

技术研发人员:杨俊浩 沈剑 张礼怿 张沁枫 薛颜 苏小波 蒋颖丹

受保护的技术使用者:中国电子科技集团公司第五十八研究所

技术研发日:2022.05.12

技术公布日:2022/7/29

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。