一种相位可调的adpll电路

技术领域

1.本发明涉及数字电路技术领域,特别涉及一种相位可调的adpll电路。

背景技术:

2.锁相环(phase-locked loop,pll)是一个具有反馈机制的电路。在pll中,振荡器的输出与参考信号比较,根据比较的差值,对振荡器进行校准。理想情况下,当锁相环锁定时,振荡器输出频率与预期振荡频率相同,并且与参考信号的相位误差维持在设定的范围之内。随着数字电路技术的发展,锁相环正朝着数字化、通用化和集成化的方向发展,adpll(all-digital phase-locked loop,全数字锁相环)已发展为一个新的研究对象。全数字锁相环使用数字电路实现模拟电路的功能,与模拟锁相环相比,全数字锁相环可移植性强且可编程,而且其相位和频率调节更容易实现,可以简化高性能的接收机。

3.adpll是否实现时钟频率的锁定需要通过时钟判断模块进行判定,通过对输出时钟状态的判断可以确定芯片是否可以开始稳定工作,以及实际运行的性能。失锁检测电路作为时钟判断模块,其输出通常作为其他模块和子系统的使能控制信号。例如,当判断输出时钟频率不符合要求时,失锁检测电路通过使能控制信号通知自动频率校准(afc)模块进行处理;当判断输出时钟频率符合要求时,失锁检测电路通过锁定信号通知相位可调模块进行处理。

4.专利cn200410082395.0将锁相环中鉴相器电路输出的相差判别信号用于pll频率锁定判断电路,监测相位的滑动情况,并将出现周期性的相位差滑动作为失锁的判决条件,用来确定锁相环频率是否锁定。此电路可以处理相位突变造成的短暂失锁,但电路结构复杂,使用的元件较多;专利cn202111084728.3提供一种数字控制振荡器,可以实现动态相位选择,但相位调节模块需要同dco一起设计,增加了dco的设计难度,且电路结构复杂,可复用性不高。

技术实现要素:

5.本发明的目的在于提供一种相位可调的adpll电路,以解决背景技术中的问题。

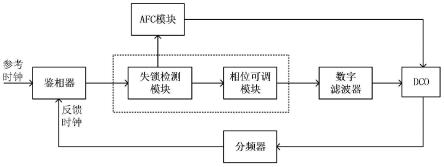

6.为解决上述技术问题,本发明提供了一种相位可调的adpll电路,包括鉴相器、失锁检测模块、相位可调模块、数字滤波器、dco、afc模块和分频器;其中,

7.所述鉴相器、所述失锁检测模块、所述相位可调模块、所述数字滤波器和所述dco依次相连,所述失锁检测模块、所述afc和所述dco组成环路,所述dco、所述分频器和所述鉴相器组成环路;

8.所述鉴相器用于提取参考时钟与反馈时钟之间的相位误差;

9.所述失锁检测模块判断环路是否实现锁定;

10.所述相位可调模块用于调整所述鉴相器输出的相位误差;所述数字滤波器用于滤除相位误差中的高频分量;

11.所述dco产生与频率控制字相对应的时钟信号;

12.所述afc模块用于自动频率校准;

13.所述分频器将所述dco产生的时钟信号进行分频,产生反馈时钟至所述鉴相器。

14.在发明的一种实施方式中,所述失锁检测模块包括d触发器、判断电路、模128计数器、二选一数据选择器mux1;

15.由8位整数、32位小数构成的相位差信号pd[39:0]首先经过d触发器对其进行采样,得到采样信号pd_q[39:0];然后取其整数位pd_q[39:32]输入到判断电路,若pd_q[39:32]大于2,所述判断电路输出值为1的控制信号flag_afc到所述afc模块,表明相位差信号需转到afc模块进行处理;若pd_q[39:32]不大于2,所述判断电路输出值为0的控制信号flag_afc到afc模块,表明相位差信号无需转到afc模块进行处理;若pd_q[39:32]不等于0,所述判断电路输出值为0的计数器清零信号flag_clr至模128计数器,对所述模128计数器进行清零;若pd_q[39:32]等于0,所述判断电路输出值为1的计数器清零信号flag_clr至模128计数器,所述模128计数器正常计数;若模128计数器计满128个周期,则输出值为1的锁定信号lock,表明环路已经锁定,同时lock信号控制二选一数据选择器mux1选择数字地信号gnd作为所述模128计数器的时钟输入。

[0016]

在发明的一种实施方式中,所述判断电路由数值比较器1和数值比较器2构成;采样信号的整数位pd_q[39:32]分别连接数值比较器1和数值比较器2的一端,所述数值比较器1的另一端连接固定数值8'h2,数值比较器1的输出端输出控制信号flag_afc,连接到所述afc模块;数值比较器2的另一端连接固定数值8'h0,数值比较器2的输出端输出计数器清零信号flag_clr,连接到所述模128计数器的清零端clr。

[0017]

在发明的一种实施方式中,所述d触发器的数据端d连接相位差信号pd[39:0],时钟端clk连接全局时钟ckr,复位端reset连接复位信号reset,输出端q输出至所述判断电路;所述模128计数器的清零端clr连接数值比较器2的输出端,所述模128计数器的时钟端clk连接二选一数据选择器mux1的输出端,进位端c输出锁定信号lock,分别连接到二选一数据选择器mux1的控制端和二选一数据选择器mux2的控制端;所述二选一数据选择器mux1的数据端d0连接全局时钟ckr,数据端d1连接数字地信号gnd,输出端连接所述模128计数器的时钟端clk,控制端连接所述模128计数器的进位端c。

[0018]

在发明的一种实施方式中,所述相位可调模块包括二选一数据选择器mux2、加法器和四选一数据选择器mux3;经过所述d触发器采样得到的采样信号pd_q[39:0]同时会输入到所述相位可调模块进行处理,由四选一数据选择器mux3的控制信号s1s0从输入的四路数据中选出一路数据与采样信号pd_q[39:0]进行相加,得到的和信号输入到二选一数据选择器mux2的d1端;二选一数据选择器mux2的d0端为采样信号pd_q[39:0],二选一数据选择器mux2的控制信号为锁定信号lock,当lock值为1时选择d1端的数据输出,即为调整后的相位差信号pd_adj[39:0]。

[0019]

在发明的一种实施方式中,所述四选一数据选择器mux3的数据端d00连接固定数值40'h1,数据端d01连接固定数值40'h2,数据端d10连接固定数值40'h4,数据端d11连接固定数值40'h8,输出端连接到加法器的一端,控制端s1、s0分别连接控制信号s1、s0;

[0020]

所述加法器的一个输入端连接d触发器的输出端q,另一个输入端连接四选一数据选择器mux3的输出端,所述加法器的输出端连接二选一数据选择器mux2的数据端d1;

[0021]

所述二选一数据选择器mux2的数据端d0连接d触发器的输出端q,数据端d1连接加

法器的输出端,输出端输出调整后的相位差信号pd_adj[39:0],控制端连接模128计数器的进位端c。

[0022]

在本发明提供的一种相位可调的adpll电路中,通过在鉴相器后添加失锁检测模块和相位可调模块,所述失锁检测模块用于产生锁定信号lock,所述相位可调模块用于产生调整后的相位差信号pd_adj,实现了在adpll内部环路中进行相位可调以及对环路是否锁定的监测,而且本发明的电路结构简单,容易实现,可复用性高。

附图说明

[0023]

图1是本发明提供的一种相位可调的adpll电路原理结构示意图;

[0024]

图2是相位可调的adpll电路中失锁检测模块的电路结构图;

[0025]

图3是失锁检测模块中判断电路的结构示意图;

[0026]

图4是相位可调的adpll电路中相位可调模块的电路结构图;

[0027]

图5是失锁检测模块和相位可调模块的完整电路结构图。

具体实施方式

[0028]

以下结合附图和具体实施例对本发明提出的一种相位可调的adpll电路作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

[0029]

本发明的一种相位可调的adpll电路,其原理结构如图1所示,包括鉴相器、失锁检测模块、相位可调模块、数字滤波器、dco(数控振荡器)、afc(自动频率校准模块)和分频器;其中所述鉴相器、所述失锁检测模块、所述相位可调模块、所述数字滤波器和所述dco依次相连,所述失锁检测模块、所述afc和所述dco组成环路,所述dco、所述分频器和所述鉴相器组成环路。所述鉴相器用于提取参考时钟与反馈时钟之间的相位误差;所述失锁检测模块判断环路是否实现锁定;所述相位可调模块用于调整所述鉴相器输出的相位误差;所述数字滤波器用于滤除相位误差中的高频分量;所述dco产生与频率控制字相对应的时钟信号;所述afc模块用于自动频率校准;所述分频器将所述dco产生的时钟信号进行分频,产生反馈时钟至所述鉴相器。

[0030]

所述失锁检测模块用于产生锁定信号lock,其结构如图2所示,包括d触发器、判断电路、模128计数器、二选一数据选择器mux1。所述d触发器的数据端d连接相位差信号pd[39:0],时钟端clk连接全局时钟ckr,复位端reset连接复位信号reset,输出端q输出至所述判断电路。由8位整数32位小数构成的相位差信号pd[39:0]首先经过d触发器对其进行采样,得到采样信号pd_q[39:0];然后取其整数位pd_q[39:32]输入到判断电路,若pd_q[39:32]大于2,所述判断电路输出值为1的控制信号flag_afc到所述afc模块,表明相位差信号需转到afc模块进行处理;若pd_q[39:32]不大于2,则输出值为0的控制信号flag_afc到afc模块,表明相位差信号无需转到afc模块进行处理;若pd_q[39:32]不等于0,同时的,所述判断电路输出值为0的计数器清零信号flag_clr至模128计数器,对所述模128计数器进行清零,若pd_q[39:32]等于0,则输出值为1的计数器清零信号flag_clr至模128计数器,所述模128计数器正常计数;若模128计数器计满128个周期,则输出值为1的锁定信号lock,表明环

路已经锁定,同时lock信号控制二选一数据选择器mux1选择数字地信号gnd作为所述模128计数器的时钟输入。

[0031]

如图3所示,所述判断电路由数值比较器1和数值比较器2构成,用于产生控制信号flag_afc和计数器清零信号flag_clr。采样信号的整数位pd_q[39:32]分别连接数值比较器1和数值比较器2的一端,所述数值比较器1的另一端连接固定数值8'h2,数值比较器1的输出端输出控制信号flag_afc,连接到所述afc模块;数值比较器2的另一端连接固定数值8'h0,数值比较器2的输出端输出计数器清零信号flag_clr,连接到所述模128计数器的清零端clr。

[0032]

所述相位可调模块用于产生调整后的相位差信号pd_adj;其结构如图4所示,包括二选一数据选择器mux2、加法器和四选一数据选择器mux3。经过所述d触发器采样得到的采样信号pd_q[39:0]同时会输入到所述相位可调模块进行处理,由四选一数据选择器mux3的控制信号s1s0从输入的四路数据中选出一路数据与采样信号pd_q[39:0]进行相加,得到的和信号输入到二选一数据选择器mux2的d1端,二选一数据选择器mux2的d0端为采样信号pd_q[39:0],二选一数据选择器mux2的控制信号为锁定信号lock,当lock值为1时选择d1端的数据输出,即为调整后的相位差信号pd_adj[39:0]。

[0033]

请继续参阅图2,所述模128计数器的清零端clr连接数值比较器2的输出端,所述模128计数器的时钟端clk连接二选一数据选择器mux1的输出端,进位端c输出锁定信号lock,分别连接到二选一数据选择器mux1的控制端和二选一数据选择器mux2的控制端。所述二选一数据选择器mux1的数据端d0连接全局时钟ckr,数据端d1连接数字地信号gnd,输出端连接所述模128计数器的时钟端clk,控制端连接所述模128计数器的进位端c。

[0034]

请继续参阅图4,所述四选一数据选择器mux3的数据端d00连接固定数值40'h1,数据端d01连接固定数值40'h2,数据端d10连接固定数值40'h4,数据端d11连接固定数值40'h8,输出端连接到加法器的一端,控制端s1、s0分别连接控制信号s1、s0。所述加法器的一个输入端连接d触发器的输出端q,另一个输入端连接四选一数据选择器mux3的输出端,所述加法器输出端连接二选一数据选择器mux2的数据端d1。所述二选一数据选择器mux2的数据端d0连接d触发器的输出端q,数据端d1连接加法器的输出端,输出端输出调整后的相位差信号pd_adj[39:0],控制端连接模128计数器的进位端c。

[0035]

综上所述,本发明提供的adpll电路的内部环路中包括失锁检测模块和相位可调模块,如图5所示,实现了对环路是否锁定的监测和相位可调:失锁检测模块通过对输入的相位差信号进行判断,若输入的相位差值较大,表明环路失锁,需要转到afc模块进行校准;若差值较小,则模128计数器开始计数,直到计满128个周期,输出锁定信号,表明环路锁定。同时相位可调模块通过控制信号对输入的相位差信号进行处理,只有当环路锁定时才输出调整后的相位差信号。

[0036]

上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。