一种增强型n沟道和p沟道gan器件集成结构

技术领域

1.本发明主要涉及氮化镓功率半导体集成技术领域,具体来说,是一种增强型n沟道和p沟道gan器件集成结构。

背景技术:

2.宽带隙半导体电子器件可用于要求高工作电压/速度和低功率损耗以及耐受恶劣工作条件的任务中。在这种器件中,宽能带隙抑制了从价带到导带的自发电子跃迁,这种跃迁可能被高电场、高温和高能粒子的环境能量激活。这使得器件能够在各种极端情况下保持其电气特性。氮化镓是一种关键的宽带隙半导体,最流行的器件结构是基于平面异质结的高电子迁移率晶体管(hemt)。氮化镓hemt在二维电子气(2deg)通道中提供高电子迁移率和小终端电容,使其特别适合高频/高功率密度应用,如射频功率放大器和紧凑型功率转换器/电源。

3.使用硅兼容工艺设备在大硅衬底上制造的氮化镓hemt已经被开发用于电力电子,这导致了具有高电压阻断能力增强模式操作以及长期操作中的优异稳定性和可靠性的电力开关器件的发展。作为功率开关器件,分立氮化镓hemt已被用于调节几十安培的电流,并阻挡高达约1kv(千伏)的高电压。这些核心器件需要外围电路作为驱动、控制、检测和保护模块。单片集成有利于创建更多的片上功能、增强鲁棒性并促进整个功率转换系统的小型化。氮化镓hemt具有平面配置,其中所有三个器件端(源极、栅极和漏极)都位于顶部表面上。这种配置有利于高密度集成,这种集成导致了集成栅极驱动器的氮化镓功率开关的商业发展。然而,所有这些氮化镓集成电路都是基于以电子作为多数载流子的n沟道器件。

4.氮化镓功率器件的外围电路通常由数量可观的逻辑模块组成。对于硅基逻辑电路,互补逻辑金属氧化物半导体(cmos)拓扑占主导地位,因为它为超大规模集成电路和混合信号集成电路提供了最节能的方案。尽管氮化镓基器件发展迅速并已商业化,但实际氮化镓cmos电路的开发仍充满挑战。这尤其是由于缺乏合适的集成策略来同时结合增强型n沟道器件和p沟道器件。商用p-gan栅极功率hemt平台(基于生长在硅衬底上的p-gan/algan/gan异质结)对于实现用于功率开关的逻辑控制的单片集成互补逻辑电路是有希望的,因为增强型n沟道器件是容易获得的,并且p-gan层为p沟道器件提供了引人注目的场所。通过使用栅极凹槽等处理技术,增强模式p沟道器件的性能得到了改善。尽管氮化镓中电子和空穴的大迁移率失配(几乎两个数量级)不支持氮化镓作为高速先进cmos的最佳候选,氮化镓功率开关的逻辑控制要求较低的操作速度(在100khz-10mhz范围内),这为氮化镓片上互补逻辑集成电路在“全氮化镓”片上系统功率电子解决方案中提供了一个可行的机会。

技术实现要素:

5.针对上述问题,本发明提出一种增强型n沟道和p沟道gan器件集成结构,本发明结构能够在使用传统n沟道氮化镓hemt工艺的基础上保证n沟道器件的增强型同时很好的提

高p沟道氮化镓hemt的输出电流和阈值电压。

6.本发明采用如下技术方案:

7.一种增强型n沟道和p沟道gan器件集成结构,包括:衬底,在衬底上设有铝氮成核层,在铝氮成核层上设有铝氮镓缓冲层,在铝氮镓缓冲层上设有氮化镓沟道层,在氮化镓沟道层上设有铝镓氮势垒层,在铝镓氮势垒层内设有隔离层且深及氮化镓沟道层内,所述隔离层将铝镓氮势垒层和氮化镓沟道层分割为两部分;在隔离层的一侧设有p沟道器件,所述p沟道器件包括设在隔离层一侧的铝镓氮势垒层上的第一p型氮化镓层,在第一p型氮化镓层上设有第一氮化镓隔离层,在第一氮化镓隔离层上设有第一p

型氮化镓层,在第一p

型氮化镓层上设有第一源极、第一栅极和第一漏极,所述第一栅极陷入所述第一p

型氮化镓层,在第一栅极与第一p

型氮化镓层之间设有栅极介质层;在隔离层的另一侧设有n沟道器件,所述n沟道器件包括设在隔离层另一侧的铝镓氮势垒层上的第二源极、第二p型氮化镓层和第二漏极,第二源极、第二漏极分别位于第二p型氮化镓层的两侧,在第二p型氮化镓层上方设有第二氮化镓隔离层,第二氮化镓隔离层上方设有第二p

型氮化镓层,第二p

型氮化镓层上方设有第二栅极。

8.与现有技术相比,本发明具有如下有益效果:

9.从上述技术方案可以看出,本发明主要将p-gan分成三个不同掺杂浓度的层次,保持与铝镓氮势垒层接触和与欧姆金属层接触的两层p-gan掺杂浓度较高,而这两层高浓度p-gan之间的一层p-gan保持较低的掺杂浓度;p沟道器件栅极区域铝氮插入层和栅极介质层组成栅介质叠层。可至少实现以下有益效果:

10.1,底层p型氮化镓层一方面在p沟道器件中提供导通通道,p型掺杂下提供一定浓度空穴,器件开启后增加输出电流;另一方面在n沟道器件中底层p型氮化镓层提供的空穴关断铝镓氮势垒层下方的二维电子气,保证n沟道器件的增强型。

11.2,中间氮化镓隔离层保持低的掺杂浓度,在p沟道器件中栅极区域下方的gan中空穴浓度低,更容易实现关断,在阈值一定时可通过增加栅下gan厚度,减少器件导通电阻,增加输出电流;对于n沟道器件的阈值无明显影响。

12.3,顶层p

型氮化镓层保持一个高掺杂浓度,对于p沟道器件p

型氮化镓层高掺杂利于源漏区欧姆接触的形成减小接触电阻;另外在p沟道器件导通后提供高空穴浓度从而提高器件输出电流。

13.4,栅极区域介质叠层,铝氮插入层与下方gan由于极化效应产生高浓度的二维电子气,电子气关断栅极区域的空穴气;栅极金属与铝氮插入层间有一层栅极介质层,采取高禁带宽度的介质可进一步关断栅极区域空穴气;栅极介质叠层实现提高p沟道器件的阈值电压。

14.5,可实现n沟道与p沟道氮化镓器件的cmos集成。

附图说明

15.图1所示为传统n沟道和p沟道氮化镓功率器件集成结构的示意图。

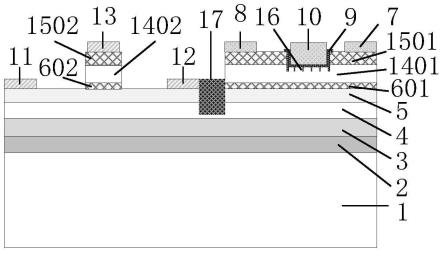

16.图2所示为本发明增强型n沟道和p沟道氮化镓功率器件集成结构的一实施例示意图。

17.图3所示为p沟道器件本发明结构一实施例与传统结构栅极区域不同p-gan厚度下

实现相同阈值数据对比图。

18.图4所示为p沟道器件本发明结构一实施例与传统结构栅极区域不同p-gan厚度得到相同阈值时的输出特性曲线对比图。

19.图5所示为p沟道器件本发明中一实施例不含铝氮插入层结构与传统结构栅极区域不同p-gan厚度下实现的相同阈值数据对比图。

20.图6所示为p沟道器件本发明中一实施例不含铝氮插入层结构与传统结构栅极区域不同p-gan厚度得到相同阈值时的输出特性曲线对比图。

21.图7所示为n沟道器件本发明结构一实施例与传统结构转移特性曲线对比图。

22.图8所示为n沟道器件本发明结构一实施例与传统结构输出特性曲线对比图。

23.图9所示为p沟道器件传统结构栅极区域与栅漏间区域能带对比图。

24.图10所示为p沟道器件本发明结构一实施例与传统结构相同阈值时栅极区域能带图。

25.图中有:衬底1,铝氮成核层2,铝镓氮缓冲层3,氮化镓沟道层4,铝镓氮势垒层5,第一p型氮化镓层601,第二p型氮化镓层602,第一源极7,第一漏极8,栅极介质层9,第一栅极10,第二源极11,第二漏极12,第二栅极13,第一氮化镓隔离层1401,第二氮化镓隔离层1402,第一p

型氮化镓层1501,第二p

型氮化镓层1502,铝氮插入层16,隔离层17。

具体实施方式

26.一种增强型n沟道和p沟道gan器件集成结构,包括:衬底1,在衬底1上设有铝氮成核层2,在铝氮成核层2上设有铝氮镓缓冲层3,在铝氮镓缓冲层3上设有氮化镓沟道层4,在氮化镓沟道层4上设有铝镓氮势垒层5,在铝镓氮势垒层5内设有隔离层17且深及氮化镓沟道层4内,所述隔离层17将铝镓氮势垒层5和氮化镓沟道层4分割为两部分;在隔离层17的一侧设有p沟道器件,所述p沟道器件包括设在隔离层17一侧的铝镓氮势垒层5上的第一p型氮化镓层601,在第一p型氮化镓层601上设有第一氮化镓隔离层1401,在第一氮化镓隔离层1401上设有第一p

型氮化镓层1501,在第一p

型氮化镓层1501上设有第一源极7、第一栅极10和第一漏极8,所述第一栅极10陷入所述第一p

型氮化镓层1501,在第一栅极10与第一p

型氮化镓层1501之间设有栅极介质层9;在隔离层17的另一侧设有n沟道器件,所述n沟道器件包括设在隔离层17另一侧的铝镓氮势垒层5上的第二源极11、第二p型氮化镓层602和第二漏极12,第二源极11、第二漏极12分别位于第二p型氮化镓层602的两侧,在第二p型氮化镓层602上方设有第二氮化镓隔离层1402,第二氮化镓隔离层1402上方设有第二p

型氮化镓层1502,第二p

型氮化镓层1502上方设有第二栅极13;其中,衬底1的材料为p型硅、蓝宝石或sic等材料,导通n沟道器件的二维电子气位于氮化镓沟道层4内,导通p沟道器件的二维空穴气位于第一p型氮化镓层601内,铝镓氮势垒层5厚度为12-25nm,铝组分为0.15-0.3;第一p型氮化镓层601和第一铝镓氮势垒层5的接触面存在二维空穴气,且位于第一p型氮化镓601内。p沟道器件栅极区域的凹槽形状、栅极介质层9与铝氮插入层16,可以确保栅极区域的二维空穴气断开,这样p沟道器件就是增强型;铝镓氮势垒层5与氮化镓沟道层4的接触面存在二维电子气,且二维电子气在氮化镓沟道层4内。第二p型氮化镓层602、第二氮化镓隔离层1402与第二p

型氮化镓层1502,确保栅极区域的二维电子气断开,这样n沟道器件就是增强型。在本实施例中,

27.第一栅极10及栅极介质层9向第一氮化镓隔离层1401延伸并进入第一氮化镓隔离层1401,并在栅极介质层9的下表面设有铝氮插入层16,所述铝氮插入层16位于第一栅极10的下方,所述栅极介质层9再延伸并包覆于铝氮插入层16的侧面。

28.第一p型氮化镓层601和第二p型氮化镓层602的厚度为10-15nm、掺杂浓度为1.0

×

10

18

/cm3~1.0

×

10

19

/cm3;第一氮化镓隔离层1401和第二氮化镓隔离层1402的厚度为30-40nm、掺杂浓度为1.0

×

10

14

/cm3~1.0

×

10

16

/cm3;第一p

型氮化镓层1501和第二p

型氮化镓层1502的厚度为20-35nm、掺杂浓度为1.0

×

10

19

/cm3~1.0

×

10

20

/cm3,掺杂剂为mg或be;所述第一氮化镓隔离层1401与第一p型氮化镓层601的厚度之和为20nm~50nm;所述铝氮插入层16厚度为5-15nm;所述栅极介质层9厚度为5-10nm,栅极介质层9材料为氧化铝、氧化硅或氮化硅。

29.下面结合附图对本发明进行进一步说明。

30.本发明的工作原理:

31.对于氮化镓材料目前一个主要的应用场景就是通过algan/gan异质结结构在异质结界面产生高浓度的二维电子气(2deg),二维电子气具有很好的高频特性,基于二维电子气设计性能优异的氮化镓电路。但设计氮化镓cmos逻辑电路缺少与n沟道器件可集成的良好p沟道器件,目前国内外研究机构的设计方案中,针对p沟道氮化镓hemt,采取以下方式实现:比如在n沟道氮化镓hemt的外延结构上通过p型氮化镓层实现,或通过氮化镓和铝镓氮异质结间的极化效应产生的二维空穴气实现,但这些方法获得的p沟道器件的电流能力都较小。小电流能力的p沟道器件将导致cmos逻辑电路设计的面积过大,性能极差;设计提高p沟道器件的输出电流是实现氮化镓cmos电路的重点。

32.本发明在传统结构的基础上,提出了一种新的结构;其中图1所示为传统结构实现氮化镓cmos逻辑电路的示意图,图2为本发明的其中一种实施例实现增强型n沟道和p沟道gan器件集成结构的示意图。本发明将传统相同掺杂浓度的一层p-gan分成三个不同掺杂浓度的层次,三层不同掺杂浓度的p-gan厚度之和与传统结构p-gan保持一致,三层p-gan的厚度按照需求分别取不同数值。保持与铝镓氮势垒层接触和与欧姆金属层接触的两层p-gan掺杂浓度较高,而这两层高浓度p-gan之间的一层p-gan保持较低的掺杂浓度,其中掺杂浓度最高的是与欧姆金属层接触的p-gan。三层p-gan的设置在兼容传统n沟道p-gan工艺上实现p沟道氮化镓器件,分别保证n沟道和p沟道器件的增强型、同时保持较高的输出电流,从而实现氮化镓cmos结构;p沟道器件栅极区域铝氮插入层和栅极介质层组成栅叠层可进一步提高p沟道器件阈值电压。

33.首先底层的p-gan厚度为8-15nm,在p沟道器件中导通状态下提供一个导通通道,导通本身存在的电离空穴与极化的二维空穴气;由于p型掺杂对二维空穴气的迁移率有一定阻碍作用,所以保持p型氮化镓层掺杂较传统掺杂略低。在n沟道器件中栅极区域含有第二p型氮化镓层,第二p型氮化镓层保持的p型掺杂作用如传统n沟道增强型高电子迁移率晶体管的p-gan层,该层可以抬升整个异质结的导带从而耗尽异质结导电沟道(氮化镓沟道层)中的2deg,保证n沟道器件的增强型。图7展示了n沟道器件本发明结构与传统结构转移特性曲线对比图,图中可以看出本发明结构的n沟道器件阈值相对传统结构没有明显降低。图8所示为n沟道器件本发明结构与传统结构输出特性曲线对比图,本发明结构的线性区曲线斜率大于传统结构,说明n沟道器件本发明结构的导通电阻较传统结构略有减小,开关速

度快。本发明结构的n沟道器件的饱和电流与传统结构基本一致。

34.其次中间的p-gan层(氮化镓隔离层)保持非常低的掺杂浓度,掺杂浓度低的p-gan中含有较少的空穴浓度。p沟道器件中栅极区域栅介质叠层的下方及左右两侧与氮化镓隔离层接触,较少的空穴浓度可以维持栅介质叠层下方的gan具有更厚的厚度时就使得栅极区域gan/algan异质结处的价带移至费米能级以下,实现器件的关断。图9中为传统结构的栅极区域与栅漏间区域的能带对比图,可以看到更厚的gan层将导致gan/algan异质结处价带明显高于费米能级,即器件为耗尽型工作模式,不利于安全工作。如图10所示的能带图,异质结处相同价带高度时本发明结构栅极区域gan更厚;如图3所示为p沟道器件本发明结构与传统结构栅极区域gan具有不同厚度实现相同阈值的数据对比图,结果进一步证明了图10的结论即同一阈值下本发明可增加栅极区域的gan厚度。p沟道器件栅极区域下方的gan厚度更厚将减小器件导通电阻,增加器件输出电流,图4所示为p沟道器件本发明结构一实施例与传统结构栅极区域不同p-gan厚度得到相同阈值时的输出特性曲线对比图,可以看到在相同仿真环境下本发明的输出电流明显大于传统结构。对于本发明的一个具体实施例,传统方法中形成p沟道器件的栅极区域是通过刻蚀栅极区域的顶部p-gan,刻蚀过程中随刻蚀深度增加将会降低下方二维空穴气的迁移率,本发明栅极下方的gan更厚即刻蚀深度较浅,可以避免刻蚀对二维空穴气迁移率的影响,从而实现增加器件输出电流。

35.而对于顶层p

型氮化镓层保持一个mg、be等p沟道掺杂剂的高掺杂浓度,高掺杂利于p沟道器件源漏区欧姆接触的形成减小接触电阻,另外在器件导通后高掺杂浓度的p

型氮化镓层提供更高空穴浓度有利于提高p沟道器件输出电流。

36.此外,对于栅极区域介质层,本发明采取铝氮插入层与传统栅介质层结合组成栅介质叠层的方式。首先铝氮插入层与下方gan由于极化效应产生高浓度的二维电子气可以消耗栅极区域p-gan中的空穴,实现提高p沟道器件的阈值电压;图5所示为p沟道器件本发明中一实施例不含铝氮插入层结构与传统结构栅极区域不同p-gan厚度下实现的相同阈值数据对比图,该实施例gan厚度分别保持与图3结构相同,对比可知铝氮插入层明显增加器件阈值电压。其次是一定厚度传统p沟道器件栅极介质层,栅介质层材料采取氧化铝、氧化硅、氮化硅等高禁带宽度的介质;该类介质一方面可进一步降低异质结处价带高度、实现增加器件阈值电压,一方面由于高禁带宽度可承受更高的电压、增加栅极耐压。

37.图6所示为p沟道器件本发明中不含铝氮插入层结构与传统结构栅极区域不同p-gan厚度得到相同阈值时的输出特性曲线对比图,本发明中三层不同掺杂浓度p-gan的设置在p沟道器件中可明显保留栅极区域更厚的gan,从而减小器件导通电阻。

38.n沟道与p沟道器件均为增强型模式工作是电力电子技术安全要求,也是本发明设计的基础。本发明中p型氮化镓层602与p

型氮化镓层1502,两层内含有的空穴关断n沟道器件铝镓氮势垒层5下方电子气保证n沟道器件增强型;氮化镓隔离层1401与栅极介质层9减小p沟道器件p型氮化镓层601中极化产生的空穴,同时铝氮插入层16与氮化镓隔离层1401产生电子气与p型氮化镓层601中的空穴形成电中性,实现p沟道器件的增强型操作。对于p沟道器件,p型氮化镓层601与p

型氮化镓层1501在p沟道器件导通后均提供空穴,尤其是p

型氮化镓层1501提供高浓度的空穴,氮化镓隔离层1401保证导通沟道具有更大的面积;更高的空穴浓度,更大的沟道面积可以得到更小的导通电阻。高空穴浓度保证第一源极7和第一漏极8与p

型氮化镓层1501的欧姆接触电阻更小;小导通电阻和小接触电阻双重效应下

本发明的p沟道器件输出电流更高,图4和图6本发明结构的输出电流分别提高了43%和71%,高输出电流的p沟道器件将极大的减小cmos逻辑氮化镓电路的面积。

39.综上所述,本发明即保证了n沟道与p沟道氮化镓器件的增强型操作,又提高了p沟道器件输出电流;同时本发明与传统p型氮化镓型(p-gan)高电子迁移率晶体管工艺兼容,具有很大实用性;对实现高性能氮化镓cmos逻辑电路具有重大意义。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。