1.本公开内容的实施方式一般涉及改进的形成互连的方法。本公开内容的另外的实施方式涉及在低温下形成钨的方法。

背景技术:

2.可靠地产生100nm以下及更小的特征是半导体器件的下一代极大规模集成(next generation very large scale integration;vlsi)及超大规模集成(ultra-large-scale integration;ulsi)的关键技术挑战之一。然而,随着电路技术的极限推进,vlsi及ulsi技术的缩小的尺寸已经对处理能力提出了额外要求。在基板上可靠地形成栅极结构对于vlsi及ulsi的成功以及对于增加电路密度及单个基板及裸片的质量的持续努力而言是重要的。

3.由于下一代器件的电路密度增加,互连(诸如通孔、沟槽、触点、栅极结构、及其他特征)的宽度、以及其间的介电材料的宽度减小到45nm及32nm的尺寸或以下,而介电层的厚度保持实质上恒定,结果是增加特征的深宽比。为了能够制造下一代器件及结构,半导体芯片的三维(3d)堆叠经常用于改进晶体管的性能。通过以三维而不是常规的二维来布置晶体管,多个晶体管可在集成电路(integrated circuit;ic)中非常靠近彼此地放置。半导体芯片的3d堆叠减小接线长度并且保持低的接线延迟。在制造时,半导体芯片的3d堆叠,阶梯状结构经常用于允许其上设置多个互连结构,从而形成高密度的垂直晶体管器件。

4.因此,持续需要用于形成互连以降低制造成本、存储器单元大小、及集成电路的功耗的改进的方法。

5.已知通过化学气相沉积(chemical vapor deposition;cvd)沉积的钨膜具有相对高的应力值粗糙度。另外,已知使用六氟化钨沉积的钨膜具有相对高水平的氟杂质。相对高水平的应力、粗糙度及氟杂质经常引起问题,包括但不限于晶片弯曲、结构变形、间隙填充中的空隙及缝隙、以及界面处的氟侵蚀损坏。

6.已经开发来克服这些问题的一些方法依赖于原子层沉积(atomic layer deposition;ald)。然而,ald方法通常在相对高的温度(一般高于或等于400℃)下执行。

7.由此,需要也在较低温度下执行的提供低粗糙度、低应力及低杂质的沉积钨的方法。

技术实现要素:

8.本公开内容的一个或多个实施方式涉及一种沉积钨的方法。方法包含将基板暴露于氢气流及在将基板暴露于氢气流的同时将基板暴露于钨前驱物流以在基板上沉积钨层。将基板维持在小于或等于约350℃的温度下。

9.本公开内容的额外实施方式涉及一种沉积钨的方法。方法包含将基板暴露于氢气流及在将基板暴露于氢气流的同时将基板暴露于钨前驱物流。氢气流与钨前驱物流的比率大于或等于约500:1。

10.本公开内容的另外的实施方式涉及一种选择性沉积钨的方法。方法包含将包含第

一材料表面及第二材料表面的基板暴露于氢气流以及在将基板暴露于氢气流的同时将基板暴露于钨前驱物流以在第一材料表面上沉积第一厚度的钨并且在第二材料表面上沉积第二厚度的钨。第一厚度与第二厚度的比率大于或等于约200:1。

附图说明

11.为了能够详细理解本公开内容的上述特征所用方式,可参考实施方式进行对上文简要概述的本公开内容的更具体描述,一些实施方式在附图中示出。然而,将注意,附图仅示出本公开内容的常见实施方式,并且由此不被认为限制其范围,因为本公开内容可允许其他等同有效的实施方式。

12.图1示出了根据一个或多个实施方式的形成互连的方法;

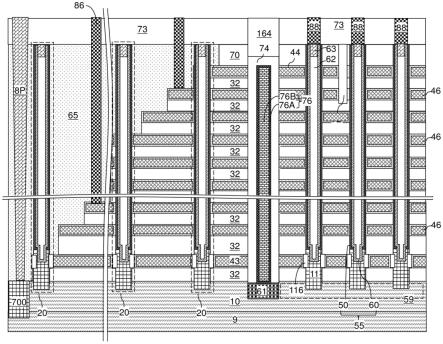

13.图2a至图2g示出了根据一个或多个实施方式的在图1的方法的不同阶段处在基板上形成的互连的横截面侧视图;

14.图3示出了根据一个或多个实施方式的可以在其上实践图1的方法的多腔室处理系统。

15.为了便于理解,相同附图标记在可能的情况下已经用于标识图中共有的相同元件。可以预期,一个实施方式的元件及特征可有利地并入其他实施方式中,而无需进一步叙述。

16.然而,应注意,附图仅示出本发明的示例性实施方式,并且由此不被认为限制其范围,因为本发明可允许其他等同有效的实施方式。

具体实施方式

17.在描述本公开内容的若干示例性实施方式之前,将理解,本公开内容不限于在以下描述中阐述的构造或工艺步骤的细节。本公开内容能够具有其他实施方式并且以各种方式实践或进行。

18.如在本说明书及随附权利要求中使用,术语“基板”指其上工艺起作用的表面、或表面的一部分。如还将由本领域技术人员所理解,除非上下文另外明确地指出,提及基板也可以指基板的仅一部分。此外,提及在基板上沉积可以意指裸基板及其上沉积或形成有一个或多个膜或特征的基板。

19.如本文所使用的“基板”指任何基板或在基板上形成的材料表面,在制造工艺期间在该基板上执行膜处理。例如,取决于应用,其上可以执行处理的基板表面包括材料,诸如硅、氧化硅、应变硅、绝缘体上硅(silicon on insulator;soi)、碳掺杂的氧化硅、非晶硅、掺杂硅、锗、砷化镓、玻璃、蓝宝石、及任何其他材料,诸如金属、金属氮化物、金属合金、及其他导电材料。基板包括但不限于半导体晶片。基板可暴露至预处理工艺以抛光、蚀刻、还原、氧化、羟基化、退火、uv固化、电子束固化和/或烘焙基板表面。除了直接在基板本身的表面上处理之外,在本公开内容中,如下文更详细公开,所公开的任何膜处理步骤还可在基板上形成的下层上执行,并且术语“基板表面”意欲包括如上下文指出的此种下层。因此,例如,在膜/层或部分膜/层已经沉积到基板表面上的情况下,新沉积的膜/层的暴露表面变为基板表面。

20.图1是示出用于在基板上形成互连的方法100的一个实施方式的流程图。图2a至图

2g示出了在图1的方法100之前以及在图1的方法100的不同阶段处的基板的横截面图。

21.图2a示出了在开始方法100之前的互连200的横截面图。大体上,互连200包括可用于形成互连结构(诸如双镶嵌结构)的多个膜层。膜堆叠201在基板202上形成。堆叠201包括介电层204。如图2a所示,介电层204在基板202上设置并且具有在介电层204中形成且由介电层204界定的导电层206。在一个实例中,介电层204可由一种或多种绝缘材料(诸如氧化硅)形成。在一个实例中,导电层206可由导电层(诸如铜)形成。

22.在方块102处,如图2b中示出,介电阻挡层208在基板202上沉积。例如,如图所示,介电阻挡层208在介电层204及导电层206两者上方沉积。由此,介电阻挡层208可在介电层204及导电层206上方形成均匀不间断的层。介电阻挡层208可由低介电常数材料形成。例如,介电阻挡层208可由含碳硅层(sic)、氮掺杂的含碳硅层(sicn)、氮化硅层、金属氮化物或金属氧化物(例如,aln、alo

x

、alon)、或类似者形成。

23.在方块104处,如图2c中示出,介电层210在基板202上沉积。例如,如图所示,介电层210在介电阻挡层208上方沉积。介电层210可实质上类似于介电层204。在一个实施方式中,介电层210可由与介电层204相同的材料形成。在另一实施方式中,在维持相同的低介电常数性质的同时,介电层210可由与介电层204不同的材料形成。

24.在方块106处,如图2d中示出,一个或多个通孔212在互连200中形成以暴露导电层206。例如,通孔212可穿过介电层210及介电阻挡层208两者形成以暴露下层的导电层206。大体上,通孔212具有宽度w1。在一些实施方式中,在通孔212的整个长度上每个通孔212的宽度是均匀的。在其他实施方式中,每个通孔212的宽度可从通孔212的顶部到通孔212的底部逐渐改变。

25.在方块108处,如图2e中示出,一个或多个沟槽214在互连200中形成。一个或多个沟槽214可在介电层210中形成。沟槽214经构造为加宽通孔212的至少一部分。在一些实施方式中,方块108可在方块106之前执行,即,沟槽214可在通孔212之前形成。在其他实施方式(诸如所描述的实施方式)中,沟槽214在形成通孔212之后形成。

26.在常规的制造方案中,执行“填充工艺”以填充通孔212,并且沟槽214用金属材料填充以形成互连200。例如,金属(诸如铜)可用于填充通孔212及沟槽214两者。已经发现用相同材料填充通孔212及沟槽214两者导致高互连电阻,这可导致半导体芯片中的rc延迟及ir降。

27.由于rc延迟及通过ir降的功率管理,芯片上的互连电阻影响芯片速度。随着设计规则持续缩小,互连电阻减小成为日渐重要的优先考虑因素。特定而言,在具有短互联线、小于40nm的较小通孔尺寸、及与通孔堆叠的多层布线的情况下,通孔(例如,通孔212)的电阻对总电阻影响显著,即,与穿过接线相比,穿过通孔的电阻较高。由此,对于实现芯片性能而言,减小通孔电阻已经变得日渐重要。

28.归因于在工艺集成中使用的材料,常规通孔形成导致高电阻。在方块108之后,在常规方法中,通孔填充用金属阻挡、衬垫、及块状填充材料完成。金属阻挡及衬垫用于可靠性及间隙填充牢固性。然而,当在通孔底部处沉积时,用于阻挡及衬垫层的材料由于其高电阻率可导致高通孔电阻。举例而言,常规的双镶嵌铜填充可由tan阻挡层(经由物理气相沉积(physical vapor deposition;pvd)工艺沉积)、在阻挡层上沉积的ta金属衬垫层(例如,pvd或化学气相沉积(cvd)工艺)、及在金属衬垫层上沉积的cu晶种/电镀层组成。取决于通

孔尺寸,阻挡及衬垫权重大于总通孔电阻的约50%至90%。因此,移除金属阻挡及衬垫层可有助于减小通孔电阻。然而,与此同时,由于消除阻挡及衬垫层,可能发生潜在风险。例如,互连仍将需要满足可靠性方面,包括避免介质击穿及金属电迁移。此外,可能需要双镶嵌结构中的适宜金属填充工艺集成以改进通孔电阻及线路电阻两者。

29.因此,下文论述提出选择性填充途径(例如,w填充途径),这阐明了较低通孔电阻及同时满足集成及可靠性需求。开发了界面处理(下文结合至少方块110论述)及填充工艺(下文结合至少方块118论述)以从通孔底部选择性生长金属材料(例如,w)而不损坏下层的金属层(例如,cu、w、co、及类似者)及周围电介质(例如,低介电常数电介质、氧化物、及类似者)。因此,下文论述提供了降低通孔电阻的一种或多种技术。在通孔填充之后,镶嵌填充将继续,这有助于形成等效线路电阻。

30.改进的方法100包括使用选择性金属通孔填充来减小电阻并且满足可靠性(与侧壁电介质204及暴露的导电层206的相互作用)及线路电阻需求。在方块110处,对互连200执行一个或多个预处理工艺以制备互连200来接收选择性金属通孔212填充。例如,方块110可包括子方块112-116。

31.在子方块112处,互连200经历用于通孔212中的导电层206的暴露部分的第一处理工艺。例如,当通孔212用第一金属沉积时,第一预处理工艺用于制备导电层206的暴露部分,用于自底向上生长。远程等离子体清洁工艺可用于预处理互连。互连200可移送到预处理腔室,此处互连200经历清洁工艺。例如,互连可经历在约250-350℃之间、使用h2/ar混合物、在约1-10torr的温度下的清洁工艺。在其他实施方式中,可施加轻微偏压能量以在没有金属溅射的情况下促进氧化物分离。例如,可将0-200w的能量施加到预处理腔室。

32.在子方块114处,互连200经历第二预处理工艺。第二处理工艺用于钝化通孔的侧壁216以最小化不期望的侧壁生长。如上文提及,介电层204可由低介电常数材料形成。因此,第二预处理工艺有助于密封介电层204的表面孔隙,并且保护介电层204不受浸泡前驱物的影响。在一个实施方式中,第二预处理工艺可以是在高温(例如,200-400℃)下的热前驱物浸泡。在一些实例中,可使用的前驱物是四甲基硅烷(tms)、二甲基氨基三甲基硅烷(dmatms)、及类似者。在一个实施方式中,通过使互连200经历uv烘焙工艺,子方块114中的第二预处理工艺可进一步包括将紫外线(uv)能量添加到前驱物浸泡工艺。

33.在一些实施方式中,方块110可包括子方块116。在方块116处,互连200经历可选的后处理清洁。例如,可选的预处理清洁可在通孔212的底部处的氧化或残留物生长的情况下使用。可选的预处理清洁使用含有过氧化物(例如,h2o2)的化学物质以稍微去除残留物,该化学物质具有碱性ph调谐。

34.在方块118处,如图2f中示出,在预处理工艺(方块110)之后,金属220选择性填充通孔212。例如,金属220的材料在通孔212中沉积直到点222,此处通孔212与沟槽214相交。所使用的金属220可以是任何适宜的金属材料,诸如钌(ru)、钨(w)、钴(co)、铝(al)、铜(cu)、或类似者。对金属220的主要需求是其为与在沟槽214中沉积的后续金属不同的材料。在通孔中选择性沉积金属220有助于减小通孔电阻,并且满足可靠性及线路电阻需求。

35.金属220可使用化学气相沉积(cvd)工艺沉积。cvd工艺可包括在高温(例如,350-500℃)下的h2预浸泡。cvd工艺可在约200-500℃的温度下、使用低流动速率(例如,2-100sccm)的含金属前驱物(例如,wf6)在大量的h2周围环境中执行。当沉积时,流动速率、压

力、及温度的组合有助于减小金属220的形态。在沉积金属220的材料之前,可施加常规的成核层用于初始1-3nm的成核。总生长量由工艺时间、压力、及前驱物流控制以均匀地填充通孔212。

36.在方块120处,如图2g中示出,第二金属224在每个沟槽214中沉积。例如,第二金属224从点222沉积到沟槽214的顶部。所使用的第二金属224可以是任何适宜的金属材料,诸如钌(ru)、钨(w)、钴(co)、铝(al)、铜(cu)、及类似者。对第二金属224的主要需求是其为与在通孔212中沉积的第一金属220的材料不同的材料。第二金属224可使用cvd工艺沉积。将单一金属材料的常规金属填充分为两步工艺涉及在通孔212中沉积的第一金属220,及在沟槽214中沉积的第二金属224有助于减小穿过通孔212的电阻。

37.在一些实施方式中,在沉积第二金属224之前,阻挡晶种层(未图示)可在第一金属220上方沉积。例如,若第二金属224是铜,则阻挡晶种层可以是铜阻挡晶种层。

38.在一些实施方式中,方法100可包括在沉积第二金属224之前执行的可选方块119。在方块119处,在第二金属224之前,互连200可经历预处理工艺。预处理工艺可用于移除可能已经在第一金属220的顶表面上形成的任何氧化物。例如,互连200可经历与子方块112类似的工艺。

39.图3标出了多腔室处理系统300。处理系统300可包括装载锁定腔室302、304,机器人306,传送腔室308,处理腔室310、312、314、316、318、328,及控制器320。装载锁定腔室302、304允许将基板(未图示)传送进出处理系统300。装载锁定腔室302、304可将引入处理系统300中的基板抽空以维持真空密封。机器人306可在装载锁定腔室302、304与处理腔室310、312、314、316、318、及328之间传送基板。机器人306也可在装载锁定腔室302、304与传送腔室308之间传送基板。

40.可配备每个处理腔室310、312、314、316、318、及328以执行多个基板操作,诸如原子层沉积(ald)、化学气相沉积(cvd)、pvd、蚀刻、预清洁、除气、加热、定向、或其他基板工艺。此外,可配备每个处理腔室310、312、314、316、318、及328以沉积介电阻挡层、沉积介电层、在堆叠中形成一个或多个通孔及沟槽、执行一个或多个预清洁工艺、沉积第一金属材料层、及沉积第二金属材料层。

41.控制器320可经配置为操作处理系统300的所有方面,诸如图1中公开的方法。例如,控制器320可经配置为控制在基板上形成互连的方法。控制器320包括可与存储器324及大容量存储装置一起操作的可编程中央处理单元(central processing unit;cpu)322、输入控制单元、及耦合到处理系统的各个部件以促进对基板处理的控制的显示单元(未图标),诸如电源、时钟、高速缓存、输入/输出(input/output;i/o)电路、及衬垫。控制器320还包括用于经由处理系统300中的传感器(包括监控前驱物、处理气体、及净化气体流的传感器)监控基板处理的硬件。量测系统参数(诸如基板温度、腔室大气压、及类似者)的其他传感器也可向控制器320提供信息。

42.为了促进对上文描述的处理系统300的控制,cpu 322可以是任何形式的通用计算机处理器中的一者,该通用计算机处理器可以在工业环境(诸如可编程逻辑控制器(programmable logic controller;plc))中用于控制各个腔室及子处理器。存储器324耦合到cpu 322并且存储器324是非瞬态的且可以是容易获得的存储器中的一个或多个,诸如随机存取存储器(random access memory;ram)、只读存储器(read only memory;rom)、软

盘驱动器、硬盘、或任何其他形式的数字储存器(本端或远程)。支持电路326耦合到cpu 322,用于以常规方式支持处理器。带电荷物质产生、加热、及其他工艺大体在存储器324中储存,通常为软件例程。软件例程也可由第二cpu(未图示)存储和/或执行,该第二cpu位于由cpu 322控制的硬件远程。

43.存储器324呈含有指令的计算机可读存储介质的形式,当由cpu 322执行时,所述指令促进处理系统300的操作。存储器324中的指令呈程序产品的形式,诸如实施本公开内容的方法的程序。程序代码可符合数个不同编程语言中的任一者。在一个实例中,本公开内容可实施为在计算机可读存储介质上存储的程序产品以与计算机系统一起使用。程序产品的程序定义实施方式的功能(包括本文描述的方法)。说明性计算机可读存储介质包括但不限于:(i)不可写存储介质(例如,计算机内的只读存储器装置,诸如其上永久存储信息的可由cd-rom驱动器读取的cd-rom磁盘、闪存、rom芯片、或任何类型的固态非易失性半导体存储器);以及(ii)其上存储可更改信息的可写存储介质(例如,在磁盘驱动器或硬盘驱动器内的软盘或任何类型的固态随机存取半导体存储器)。当携带导引本文描述的方法的功能的计算机可读指令时,此种计算机可读存储介质是本公开内容的实施方式。

44.上文论述的方法可能不仅依赖于处理系统300。例如,一个或多个方块(诸如方块120或子方块114)可在处理系统300外部的处理腔室中执行。

45.本公开内容的一个或多个实施方式涉及用于沉积钨的低温方法。本公开内容的一些实施方式相对介电表面在金属表面上选择性沉积钨。

46.本公开内容的一些实施方式有利地提供沉积钨的方法,其提供具有较低粗糙度、较低应力、及/或较低杂质的膜。本公开内容的一些实施方式提供了沉积钨的方法,其在较低温度下执行以促进需要低热预算的应用。

47.本文公开了用于沉积钨的方法。在一些实施方式中,本文公开的方法对应于上文描述的方块118。在一些实施方式中,通过本文公开的方法沉积的钨对应于上文描述的金属220。

48.示例性方法包含将基板暴露于氢气(h2)流及在将基板暴露于氢气流的同时将基板暴露于钨前驱物流。

49.在一些实施方式中,氢气流及钨前驱物流均是连续的。氢气及钨前驱物两者的连续流应当由本领域技术人员理解为对应于化学气相沉积(cvd)工艺。在一些实施方式中,钨前驱物流是脉冲的并且氢气流是连续的。钨前驱物的脉冲流及氢气的连续流应当由本领域技术人员理解为对应于脉冲的cvd工艺。

50.如上文描述,在一些实施方式中,方法可开始于将基板热浸泡在氢气(h2)环境中。在一些实施方式中,在氢气环境中的热浸泡可在沉积钨之后执行。在一些实施方式中,方法包含沉积第一量的钨、执行热浸泡及沉积第二量的钨。在一些实施方式中,热浸泡在约250℃至约600℃的范围中、在约300℃至约500℃的范围中、在约300℃至约400℃的范围中、或在约400℃至约500℃的范围中的温度下执行。

51.在一些实施方式中,本文公开的方法在相对低的温度下执行。如上文描述,在一些实施方式中,将基板维持在约200℃至约500℃的范围中的温度下。在一些实施方式,在一些实施方式中,将基板维持在约200℃至约400℃的范围中、在约250℃至约375℃的范围中、在约300℃至约350℃的范围中、或在约250℃至约350℃的范围中的温度下。在一些实施方式

中,将基板维持在小于或等于约400℃、小于或等于约375℃、小于或等于约350℃、小于或等于约325℃、或者小于或等于约300℃的温度下。

52.在一些实施方式中,控制氢气和/或钨前驱物的流动速率。在一些实施方式中,氢气的流动速率在约2000sccm至约20000sccm的范围中、在约2000sccm至约18000sccm的范围中、在约5000sccm至约20000sccm的范围中、或在约10000sccm至约20000sccm的范围中。在一些实施方式中,钨前驱物的流动速率小于或等于约500sccm、小于或等于约200sccm、小于或等于约100sccm、或者小于或等于约50sccm。

53.在一些实施方式中,控制在氢气的流动速率与钨前驱物的流动速率之间的比率。在一些实施方式中,氢气的流动速率与钨前驱物的流动速率的比率大于或等于约100:1、大于或等于约200:1、大于或等于约500:1、或者大于或等于约1,000:1、大于或等于约5,000:1、或者大于或等于约10,000:1。不受限于理论,据信钨膜中的有益结果(低粗糙度、低应力等)是归因于在处理腔室内存在的氢气的盈余。

54.在一些实施方式中,控制处理腔室的压力。在一些实施方式中,将腔室的压力维持在约5torr至约50torr的范围中、在约10torr至约50torr的范围中、在约20torr至约50torr的范围中、在约5torr至约20torr的范围中、或在约5torr至约10torr的范围中。在一些实施方式中,将压力维持在小于或等于约50torr。

55.钨前驱物可以是用于沉积钨膜的任何适宜前驱物。在一些实施方式中,钨前驱物包含反应性钨物质和载气。在一些实施方式中,钨前驱物包含反应性钨络合物及载气。在一些实施方式中,钨前驱物包含wf6、w

x

cl

5x

、wcl6、或w(co)6中的一个或多个。

56.在一些实施方式中,钨前驱物包含wf6或基本上由wf6组成。如在此方面使用的,当基于摩尔的大于或等于约95%、大于或等于约98%、大于或等于约99%、或者大于或等于约99.5%的反应性钨物质不具有任何载气时,钨前驱物基本上由wf6组成。

57.在一些实施方式中,通过所公开的方法沉积的钨具有相对低水平的杂质。在钨前驱物包含wf6的那些实施方式中,所沉积的钨具有小于或等于约10

20

原子/cm3、小于或等于约5x10

19

原子/cm3、小于或等于约10

19

原子/cm3、小于或等于约5x10

18

原子/cm3、或者小于或等于约10

18

原子/cm3的氟含量。

58.在一些实施方式中,所沉积的钨的表面粗糙度是相对低的。在一些实施方式中,所沉积钨的均方根粗糙度小于或等于约2nm、小于或等于约1.5nm、小于或等于约1nm、或者小于或等于约0.5nm。

59.在一些实施方式中,所沉积的钨的应力是相对低的。在一些实施方式中,所沉积的钨的应力小于或等于约2000mpa、小于或等于约1500mpa、小于或等于约1200mpa、小于或等于约1000mpa、小于或等于约800mpa、小于或等于约500mpa、或者小于或等于约200mpa。

60.在一些实施方式中,基板包含多种暴露的材料。在一些实施方式中,基板包含第一材料表面及第二材料表面。如上文标识,第一材料表面可包含金属或金属合金。在一些实施方式中,金属选自铜、钨、钴或钌中的一个或多个。另外,第二材料表面可包含低介电常数电介质、氧化物、氮化硅、氮氧化硅及类似者中的一个或多个。

61.在一些实施方式中,本文描述的方法相对第二材料表面在第一材料表面上选择性沉积钨。换言之,在一些实施方式中,第一厚度的钨在第一材料表面上沉积并且第二厚度的钨在第二材料表面上沉积。第一厚度大于第二厚度。在一些实施方式中,第一厚度与第二厚

度的比率大于或等于约100:1、大于或等于约200:1、大于或等于约250:1、大于或等于约500:1、大于或等于约700:1、或者大于或等于约1,000:1。

62.尽管上述内容涉及本发明的实施方式,但本发明的其他及进一步实施方式可在不脱离其基本范围的情况下设计,并且其范围由随附权利要求确定。

63.在整个此说明书中提及“一个实施方式”、“某些实施方式”、“一个或多个实施方式”或“一实施方式”意味着结合实施方式描述的特定特征、结构、材料、或特性包括在本公开内容的至少一个实施方式中。因此,在整个此说明书的各个位置中出现词组诸如“在一个或多个实施方式中”、“在某些实施方式中”、“在一个实施方式中”或“在一实施方式中”不一定指本公开内容的相同实施方式。此外,特定特征、结构、材料或特性可以任何适宜方式结合在一个或多个实施方式中。

64.尽管本文的公开内容已经参考特定实施方式进行描述,但是本领域技术人员将理解,所描述的实施方式仅说明本公开内容的原理及应用。本领域技术人员将显而易见,可以对本公开内容的方法及设备进行各种修改及变化,而不脱离本公开内容的精神及范围。因此,本公开内容可以包括在随附权利要求及其等同物的范围内的修改及变化。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。