一种栅极沟槽形成方法及dram制造方法

技术领域

1.本发明涉及半导体技术领域,尤其涉及一种栅极沟槽形成方法及dram制造方法。

背景技术:

2.存储器是数字系统中用以存储大量信息的设备或部件,是计算机和数字设备中的重要组成部分。存储器可分为随机存取存储器(ram)和只读存储器(rom)两大类。ram包括dram、pram、mram等,晶体管是制造这些ram的关键部件。

3.在dram中的bcat(buried channel array transistor,埋沟阵列晶体管)具有多种形成方法。在现有的sadp(self align double patterning,自对准双图案化)方法包括以下步骤:bcat掩模光刻步骤;对bcat掩模干刻蚀步骤;在第一次形成soh(spin on hard-mask,旋涂硬掩模)并进行芯轴刻蚀工艺;以ald(atomic layer deposition,原子层沉积)方式形成氧化物间隔件工艺;第二次进行多晶硅沉积;对多晶硅进行回蚀,然后去除氧化物间隔件以形成沟槽空间,其中,该沟槽空间通过下面的掩模将沟槽空间转移至有源区以形成栅极沟槽。然而,第一次形成的soh和第二次沉积的多晶硅不同,由不同材料的特性导致最终形成的字线沟槽的关键尺寸和轮廓不均匀。

技术实现要素:

4.鉴于上述的分析,本发明实施例旨在提供一种栅极沟槽形成方法及dram制造方法,用以解决现有不同硬掩模材料(soh和多晶硅)导致最终形成的字线沟槽的关键尺寸散布和轮廓不均匀的问题。

5.一方面,本发明实施例提供了一种栅极沟槽形成方法,包括:在半导体衬底上方依次形成栅极掩模层、第一旋涂硬掩模层和光刻掩模层,其中,所述光刻掩模层具有光刻掩模层图案;利用光刻掩模层图案为掩模对所述第一旋涂硬掩模层进行刻蚀以形成图案化的第一旋涂硬掩模层;在图案化的第一旋涂硬掩模层上方沉积氧化物层,以及在所述氧化物层上方形成第二旋涂硬掩模层;对所述第二旋涂硬掩模层进行刻蚀以形成图案化的第二旋涂硬掩模层;去除所述氧化物层中未被图案化的第二旋涂硬掩模层覆盖的部分以形成包括图案化的第一旋涂硬掩模层和图案化的第二旋涂硬掩模层的组合硬掩模图案;以及将所述组合硬掩模图案经由所述栅极掩模层转移至所述半导体衬底以形成栅极沟槽,其中,所述第一旋涂硬掩模层的材料与所述第二旋涂硬掩模层的材料相同。

6.上述技术方案的有益效果如下:根据本发明实施例提供的栅极沟槽形成方法,第一旋涂硬掩模层的材料与第二旋涂硬掩模层的材料相同,能够简化制作步骤,提高工艺稳定性,并且在栅极沟槽形成过程中,组合硬掩模图案中的第一旋涂硬掩模层图案与第二旋涂硬掩模层图案的关键尺寸散布和轮廓不均匀性最小化,进而能够将最终形成的栅极沟槽的关键尺寸散布最小化以及轮廓不均匀性最小化。

7.基于上述方法的进一步改进,利用光刻掩模层图案为掩模对所述第一旋涂硬掩模层进行刻蚀以形成图案化的第一旋涂硬掩模层进一步包括:以光刻掩模层图案为掩模,通

过干刻蚀工艺对所述第一旋涂硬掩模层进行刻蚀,将图案化的第一旋涂硬掩模层形成为具有第一图案,其中,所述第一图案是所述光刻掩模层图案的反相图案。

8.基于上述方法的进一步改进,在形成所述栅极掩模层之后并且在形成所述第一旋涂硬掩模层之前还包括:在所述栅极掩模层上方形成氮氧化硅掩模层。

9.基于上述方法的进一步改进,在图案化的第一旋涂硬掩模层上方沉积氧化物层,以及在所述氧化物层上方形成第二旋涂硬掩模层进一步包括:利用原子层沉积工艺在所述图案化的第一旋涂硬掩模层的侧壁和顶面上以及在暴露的氮氧化硅掩模层上方沉积氧化物层,其中,所述氧化物层的厚度用于限定所述栅极沟槽的宽度;以及通过旋涂工艺在所述氧化物层上方形成所述第二旋涂硬掩模层,其中,所述第二旋涂硬掩模层具有平坦顶面。

10.上述技术方案的有益效果如下:氧化物层的厚度用于限定栅极沟槽的宽度,因此通过改变氧化物层的厚度能够调节所述栅极沟槽的宽度。另外,通过旋涂工艺形成的第二旋涂硬掩模层来替换沉积工艺所形成的多晶硅层,提高工艺稳定性。

11.基于上述方法的进一步改进,对所述第二旋涂硬掩模层进行刻蚀以形成图案化的第二旋涂硬掩模层进一步包括:通过回蚀工艺对所述第二旋涂硬掩模层进行刻蚀,以形成图案化的第二旋涂硬掩模层,同时暴露所述氧化物层中位于所述图案化的第一旋涂硬掩模层的顶面和侧壁上的部分,其中,所述图案化的第一旋涂硬掩模层的顶面与所述图案化的第二旋涂硬掩模层的顶面齐平。

12.上述技术方案的有益效果如下:通过图案化的第一旋涂硬掩模层的顶面与图案化的第二旋涂硬掩模层的顶面齐平,使得轮廓不均匀性最小化。

13.基于上述方法的进一步改进,所述回蚀工艺利用电感耦合等离子体型蚀刻设备;以及在所述回蚀工艺中,刻蚀气体包括o2/n2/ch4的混合气体或o2/hbr的混合气体。

14.基于上述方法的进一步改进,去除所述氧化物层中未被图案化的第二旋涂硬掩模层覆盖的部分以形成包括图案化的第一旋涂硬掩模层和图案化的第二旋涂硬掩模层的组合硬掩模图案进一步包括:通过刻蚀工艺去除所述氧化物层中位于所述图案化的第一旋涂硬掩模层的顶面和侧壁上的部分以暴露所述氮氧化硅掩模的部分顶面,并形成包括图案化的第一旋涂硬掩模层和图案化的第二旋涂硬掩模层的组合硬掩模图案,其中,所述图案化的第一旋涂硬掩模层的宽度与所述图案化的第二旋涂硬掩模层的宽度相同。

15.基于上述方法的进一步改进,所述氧化物层的刻蚀工艺利用多频率的电容耦合等离子刻蚀设备;在所述氧化物层的刻蚀工艺中,lf为3000w至8000w,其中,所述lf的频率为100khz至12.36khz;以及hf为100w至3000w,其中,所述hf的频率为13.56khz至100mhz;以及在所述氧化物层的刻蚀工艺中,刻蚀气体包括ar、c4f8、o2和c4f6的混合气体。

16.上述技术方案的有益效果如下:多频率的电容耦合等离子刻蚀设备能够在氧化物层的刻蚀工艺中能够确保氧化物和第一和第二旋涂硬掩模层之间的选择比。

17.基于上述方法的进一步改进,栅极沟槽形成方法进一步包括:利用多频率的电容耦合等离子体刻蚀设备进一步去除所述氮氧化硅掩模中未被图案化的第一旋涂硬掩模层和图案化的第二旋涂硬掩模层覆盖的暴露部分,以暴露所述栅极掩模层的顶面并形成氮氧化硅掩模层图案,其中,所述氮氧化硅掩模层图案与所述组合硬掩模图案相同。

18.基于上述方法的进一步改进,在形成所述栅极掩模层之前还包括:在所述半导体衬底上方形成刻蚀停止层,其中,将所述组合硬掩模图案经由所述栅极掩模层转移至所述

半导体衬底以形成栅极沟槽进一步包括:利用过刻蚀工艺将所述组合硬掩模图案转移至所述栅极掩模层和所述刻蚀停止层,以形成栅极掩模层图案和刻蚀停止层图案;以及以所述栅极掩模层图案和所述刻蚀停止层图案为掩模,对所述半导体衬底的多个有源区进行刻蚀,以在所述多个有源区中形成所述栅极沟槽,其中,通过浅沟槽隔离sti区隔离所述多个有源区中的相邻有源区。

19.基于上述方法的进一步改进,在形成第一旋涂硬掩模层之后,并且在形成所述光刻掩模层之前,还包括:在所述第一旋涂硬掩模层上方形成抗反射层;在所述抗反射层上方形成所述光刻掩模层之后,对所述光刻掩模层进行光刻以形成光刻掩模层图案;以及在对所述第一旋涂硬掩模层进行刻蚀之后,去除所述抗反射层。

20.另一方面,本发明实施例提供了一种dram制造方法,包括:以上实施例所述的栅极沟槽形成方法形成栅极沟槽;以及在所述栅极沟槽中形成栅极介质层和栅极材料层以形成字线

21.与现有技术相比,本发明至少可实现如下有益效果之一:

22.1、第一旋涂硬掩模层的材料与第二旋涂硬掩模层的材料相同,能够简化制作步骤,提高工艺稳定性,并且在栅极沟槽形成过程中,组合硬掩模图案中的第一旋涂硬掩模层图案与第二旋涂硬掩模层图案的关键尺寸散布和轮廓不均匀性最小化,进而能够将最终形成的栅极沟槽的关键尺寸散布最小化以及轮廓不均匀性最小化。

23.2、氧化物层的厚度用于限定栅极沟槽的宽度,因此通过改变氧化物层的厚度能够调节所述栅极沟槽的宽度。另外,通过旋涂工艺形成的第二旋涂硬掩模层来替换沉积工艺所形成的多晶硅层,提高工艺稳定性。

24.3、通过图案化的第一旋涂硬掩模层的顶面与图案化的第二旋涂硬掩模层的顶面齐平,使得轮廓不均匀性最小化。

25.4、多频率的电容耦合等离子刻蚀设备能够在氧化物层的刻蚀工艺中能够确保氧化物和第一和第二旋涂硬掩模层之间的选择比。

26.本发明中,上述各技术方案之间还可以相互组合,以实现更多的优选组合方案。本发明的其他特征和优点将在随后的说明书中阐述,并且,部分优点可从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过说明书以及附图中所特别指出的内容中来实现和获得。

附图说明

27.附图仅用于示出具体实施例的目的,而并不认为是对本发明的限制,在整个附图中,相同的参考符号表示相同的部件。

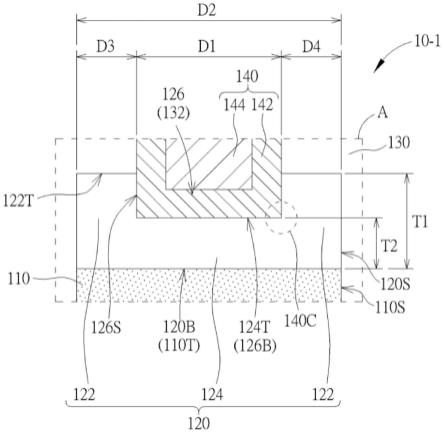

28.图1为根据本发明实施例的栅极沟槽形成方法的中间阶段的截面图。

29.图2为根据本发明实施例的栅极沟槽形成方法的中间阶段的截面图。

30.图3为根据本发明实施例的栅极沟槽形成方法的中间阶段的截面图。

31.图4为根据本发明实施例的栅极沟槽形成方法的中间阶段的截面图。

32.图5为根据本发明实施例的栅极沟槽形成方法的中间阶段的截面图。

33.图6为根据本发明实施例的栅极沟槽形成方法的中间阶段的截面图。

34.图7为根据本发明实施例的栅极沟槽形成方法的中间阶段的截面图。

35.附图标记:

36.100-半导体衬底;102-有源区;104-sti区;106-刻蚀停止层;108-栅极掩模层;110-氮氧化硅掩模层;112-第一旋涂硬掩模层;114-抗反射层;116-光刻掩模层图案;118-第一图案;120-氧化物层;122-第二旋涂硬掩模层;124-第二旋涂硬掩模层图案;126-氮氧化硅掩模层图案;128-氧化物层图案;130-沟槽;132-栅极掩模层图案;134-刻蚀停止层图案;136-沟槽

具体实施方式

37.下面结合附图来具体描述本发明的优选实施例,其中,附图构成本技术一部分,并与本发明的实施例一起用于阐释本发明的原理,并非用于限定本发明的范围。

38.本发明的一个具体实施例,公开了一种栅极沟槽形成方法。下文中,将参考图1至图7,对栅极沟槽形成方法进行详细描述。

39.首先,参考图1,提供半导体衬底100。半导体衬底100包括多个有源区102和sti(shallow trench isolation,浅沟槽隔离)区104,其中,通过浅沟槽隔离sti区104隔离多个有源区102中的相邻有源区。

40.参考图1,在半导体衬底上方依次形成栅极掩模层108、第一旋涂硬掩模层112和光刻掩模层,其中,光刻掩模层具有光刻掩模层图案116。具体地,在半导体衬底上方依次形成刻蚀停止层106、栅极掩模层108、氮氧化硅掩模层110、第一旋涂硬掩模层112、抗反射层114和光刻掩模层。在实施例中,在抗反射层114上方形成光刻掩模层之后,对光刻掩模层进行光刻以形成光刻掩模层图案116。相邻光刻掩模层图案116之间的间隔宽度为通过光刻工艺能够获得的最小关键尺寸。例如,抗反射层114的材料包括氮氧化硅(sion),栅极掩模层108的材料为非晶碳层(acl),刻蚀停止层106的材料包括氧化硅、氮化硅或者氮氧化硅。

41.参考图2,利用光刻掩模层图案116为掩模对第一旋涂硬掩模层112进行刻蚀以形成图案化的第一旋涂硬掩模层。具体地,利用光刻掩模层图案116为掩模对第一旋涂硬掩模层112进行刻蚀以形成图案化的第一旋涂硬掩模层112进一步包括:以光刻掩模层图案116为掩模,通过干刻蚀工艺对第一旋涂硬掩模层112进行刻蚀,将图案化的第一旋涂硬掩模层112形成为具有第一图案118(又称第一旋涂硬掩模层图案118),其中,第一图案是光刻掩模层图案116的反相图案。该第一图案118的宽度与相邻光刻掩模层图案116之间的间隔宽度相同,即,该第一图案118的宽度为最小关键尺寸。另外,在对第一旋涂硬掩模层112进行刻蚀同时,对抗反射层114进行刻蚀,然后去除位于图案化的第一旋涂硬掩模层上方的抗反射层图案。

42.参考图3和图4,在图案化的第一旋涂硬掩模层112上方沉积氧化物层120,以及在氧化物层120上方形成第二旋涂硬掩模层122。具体地,参考图3,在图案化的第一旋涂硬掩模层112上方沉积氧化物层进一步包括:利用原子层沉积工艺在图案化的第一旋涂硬掩模层112的侧壁和顶面上以及在暴露的氮氧化硅掩模层110上方沉积氧化物层120,其中,氧化物层120的厚度用于限定栅极沟槽的宽度。参考图4,在氧化物层120上方形成第二旋涂硬掩模层122进一步包括:通过旋涂工艺在氧化物层120上方形成第二旋涂硬掩模层122,其中,第二旋涂硬掩模层122具有平坦顶面。利用与形成第一旋涂硬掩模层112的相同的设备和工艺参数形成第二旋涂硬掩模层122,而不需要执行多晶硅沉积工艺,进而简化了制作步骤,

并提高了工艺稳定性。

43.参考图5,对第二旋涂硬掩模层122进行刻蚀以形成图案化的第二旋涂硬掩模层。具体地,通过回蚀工艺对第二旋涂硬掩模层122进行刻蚀,以形成图案化的第二旋涂硬掩模层,即,图5中所示的第二旋涂硬掩模层图案124,同时暴露氧化物层中位于图案化的第一旋涂硬掩模层的顶面和侧壁上的部分。参考图5,氧化物层包括三个部分:第一部分位于图案化的第二旋涂硬掩模层下方,第二部分位于图案化的第一旋涂硬掩模层顶面上方,以及第三部分位于图案化的第一旋涂硬掩模层和图案化的第二旋涂硬掩模层之间,具体地,位于图案化的第一旋涂硬掩模层的侧壁和图案化的第二旋涂硬掩模层的侧壁之间。因此,在回蚀工艺之后,暴露氧化物层中的整个第二部分和第三部分的顶部。图案化的第一旋涂硬掩模层的顶面与图案化的第二旋涂硬掩模层的顶面齐平。该回蚀(etch back)工艺利用电感耦合等离子体型蚀刻设备。在回蚀工艺中,刻蚀气体包括o2/n2/ch4的混合气体或o2/hbr的混合气体。在一个实施例中,在回蚀工艺中,大气压力为5mt,功率为550ws,电压为380vb,ch4的气体流量为17sccm,ar的气体流量为150sccm,n2的气体流量为90sccm,o2的气体流量为30sccm。在可选实施例中,大气压力为10mt,功率为300ws-50wb,o2的气体流量为100sccm,ar的气体流量为100sccm,hbr的气体流量为50sccm。

44.参考图6,去除氧化物层中未被图案化的第二旋涂硬掩模层覆盖的部分以形成包括图案化的第一旋涂硬掩模层112和图案化的第二旋涂硬掩模层122的组合硬掩模图案。去除氧化物层中未被图案化的第二旋涂硬掩模层覆盖的部分以形成包括图案化的第一旋涂硬掩模层112和图案化的第二旋涂硬掩模层122的组合硬掩模图案进一步包括:通过刻蚀工艺去除氧化物层中位于图案化的第一旋涂硬掩模层112的顶面和侧壁上的部分以暴露氮氧化硅掩模的部分顶面,并形成包括图案化的第一旋涂硬掩模层和图案化的第二旋涂硬掩模层的组合硬掩模图案,其中,图案化的第一旋涂硬掩模层的宽度与图案化的第二旋涂硬掩模层的宽度相同。参考图6,组合硬掩模图案包括第二旋涂硬掩模层图案124与位于第二旋涂硬掩模层图案124下方的氧化物层图案128,并且还包括第一旋涂硬掩模层图案118。氧化物层的刻蚀工艺利用多频率的电容耦合等离子刻蚀设备以确保第一和第二旋涂硬掩模层(soh)和氧化物之间的选择比。在该氧化物层的刻蚀工艺中,lf为3000w至8000w,其中,lf的频率为100khz至12.36khz;以及hf为100w至3000w,其中,hf的频率为13.56khz至100mhz。在氧化物层的刻蚀工艺中,刻蚀气体包括ar、c4f8、o2和c4f6的混合气体。在一个实施例中,在该氧化物层的刻蚀工艺中,大气压力为30mt,功率中的hf为2000w,lf为4500w,rf为同步射频,频率为5khz,占空比(duty)为40,直流电源dc为-150v,ar的气体流量为1000sccm,c4h8的气体流量为10sccm,o2的气体流量为35sccm,c4h6的气体流量为30sccm,rdc为50(33/33/34)%。过蚀刻(oe)为30%,b.he为30tr,atcc为45℃,温度t为150℃,温度w为150℃以及温度chiller为-10℃。

45.接下来,参考图6利用多频率的电容耦合等离子体刻蚀设备进一步去除氮氧化硅掩模中未被图案化的第一旋涂硬掩模层112和图案化的第二旋涂硬掩模层122覆盖的暴露部分,以暴露栅极掩模层108的顶面并形成氮氧化硅掩模层图案126并形成沟槽130。氮氧化硅掩模层图案126与组合硬掩模图案相同,具体地,氮氧化硅掩模层图案126位于组合硬掩模图案下方并与组合硬掩模图案垂直对准。例如,沟槽130的第一侧壁包括第一旋涂硬掩模层图案118的侧壁和氮氧化硅掩模层图案126的侧壁。沟槽130的第一侧壁包括第二旋涂硬

掩模层图案124的侧壁、氧化物层图案128的侧壁和氮氧化硅掩模层图案126的侧壁。

46.参考图7,将组合硬掩模图案经由栅极掩模层108转移至半导体衬底以形成栅极沟槽,其中,第一旋涂硬掩模层112的材料与第二旋涂硬掩模层122的材料相同。具体地,将组合硬掩模图案经由栅极掩模层108转移至半导体衬底以形成栅极沟槽进一步包括:利用过刻蚀工艺将组合硬掩模图案转移至栅极掩模层108和刻蚀停止层106,以形成栅极掩模层图案132和刻蚀停止层图案134,同时形成沟槽136。然后,以栅极掩模层图案132和刻蚀停止层图案134为掩模,对半导体衬底的多个有源区进行刻蚀,以在多个有源区中形成栅极沟槽,其中,通过有浅沟槽隔离sti区隔离多个有源区中的相邻有源区。

47.本发明的一个具体实施例,公开了一种dram制造方法。dram制造方法包括:通过以上实施例所述的栅极沟槽形成方法形成栅极沟槽;以及在栅极沟槽中形成栅极介质层和栅极材料层以形成bcat的栅极或字线。

48.与现有技术相比,本发明至少可实现如下有益效果之一:

49.1、第一旋涂硬掩模层的材料与第二旋涂硬掩模层的材料相同,能够简化制作步骤,提高工艺稳定性,并且在栅极沟槽形成过程中,组合硬掩模图案中的第一旋涂硬掩模层图案与第二旋涂硬掩模层图案的关键尺寸散布和轮廓不均匀性最小化,进而能够将最终形成的栅极沟槽的关键尺寸散布最小化以及轮廓不均匀性最小化。

50.2、氧化物层的厚度用于限定栅极沟槽的宽度,因此通过改变氧化物层的厚度能够调节所述栅极沟槽的宽度。另外,通过旋涂工艺形成的第二旋涂硬掩模层来替换沉积工艺所形成的多晶硅层,提高工艺稳定性。

51.3、通过图案化的第一旋涂硬掩模层的顶面与图案化的第二旋涂硬掩模层的顶面齐平,使得轮廓不均匀性最小化。

52.4、多频率的电容耦合等离子刻蚀设备能够在氧化物层的刻蚀工艺中能够确保氧化物和第一和第二旋涂硬掩模层之间的选择比。

53.本领域技术人员可以理解,实现上述实施例方法的全部或部分流程,可以通过计算机程序来指令相关的硬件来完成,所述的程序可存储于计算机可读存储介质中。其中,所述计算机可读存储介质为磁盘、光盘、只读存储记忆体或随机存储记忆体等。

54.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。