1.本发明属于微电子与半导体领域,涉及三维堆迭的封装结构及其封装方法。

背景技术:

2.传统封装以单面贴装为主,占据了较大的贴装面积。不管有没有引脚,封装的连接处都集中在封装结构的边缘或外侧,不能有效利用封装的整个底部区域与顶部区域。

3.近来引入了集成电路的三维立体封装,使得芯片可以立体地堆迭起来,增加单位体积内的电路密度。然而,每一层芯片的连接必须以客制化的方式连接,无法如堆迭积木一样将多层芯片组合起来。设计层与层之间的特定链接接口耗费大量时间与制作成本。

技术实现要素:

4.本发明是为了解决现有技术中的不足而提出的一种三维封装,目的是提供标准积木堆迭式的三维立体封装结构、半导体封装结构、与三维立体封装结构的制作方法,以解决现有封装的体积利用率低,响应时间长等问题。

5.为了实现上述目的,本发明采用了如下技术方案:根据本技术的一实施例,提供一种三维立体封装结构,其特征在于,包含:第一层,该第一层包含至少一个第一半导体封装结构,该第一半导体封装结构还包含:第一基板,其中该第一基板之中包含第一互连结构;多个第一金属凸块,分别连接至该第一互连结构所包含的电路;至少一个第一微电子元器件,该至少一个第一微电子元器件装贴至该第一基板,该至少一个第一微电子元器件的电路连接至该第一互连结构所包含的电路;在该第一基板之上的第一填充料层,用于封装包覆该至少一个第一微电子元器件;在该第一填充料层之上的多个第一金属焊垫与多个第一上表面对位结构;以及在该第一填充料层之中的多个第一垂直穿孔与其中的金属,用于连接该多个第一金属焊垫与该第一互连结构所包含的电路;以及第二层,该第二层包含至少一个第二半导体封装结构,该第二半导体封装结构还包含:第二基板,其中该第二基板之中包含第二互连结构与多个第二下表面对位结构;多个第二金属凸块,分别连接至该第二互连结构所包含的电路;至少一个第二微电子元器件,该至少一个第二微电子元器件装贴至该第二基板,该至少一个第二微电子元器件的电路连接至该第二互连结构所包含的电路;在该第二基板之上的第二填充料层,用于封装包覆该至少一个第二微电子元器件;在该第二填充料层之上的多个第二金属焊垫与多个第二上表面对位结构;以及在该第二填充料层之中的多个第二垂直穿孔与其中的金属,用于连接该多个第二金属焊垫与该第二互连结构所包含的电路,其中该第二层的至少一个该第二金属凸块与该第一层的至少一个该第一金属焊垫相连接,其中该第二层的至少一个该第二下表面对位结构与该第一层的至少一个该第一上表面对位结构相连接。

6.较佳地,为了提供更高的面积利用率与封装密度,所述的三维立体封装结构,其特征在于,还包含:第三层至第n层,其中n为大于或等于3的正整数,其中该第三层至该第n层当中的第i层,包含至少一个该第二半导体封装结构,i为3至n之间的正整数,其中该第i层

的至少一个该第二金属凸块与第i-1层的至少一个该第二金属焊垫相连接,其中该第i层的至少一个该第二下表面对位结构与该第i-1层的至少一个该第二上表面对位结构相连接。

7.较佳地,为了让微电子元器件的电路无须再绕经底下的互连结构才能连接到上方的金属焊垫,至少一个该第一垂直穿孔与其中的金属用于连接该第一金属焊垫与该至少一个第一微电子元器件的上面的电路。

8.较佳地,为了让微电子元器件的电路无须再绕经底下的互连结构才能连接到上方的金属焊垫,其中至少一个该第二垂直穿孔与其中的金属用于连接该第二金属焊垫与该至少一个第二微电子元器件的上面的电路。

9.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个第一金属焊垫的数量等于该多个第一金属凸块的数量。

10.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个第二金属焊垫的数量等于该多个第二金属凸块的数量。

11.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第一轴相邻的任两个该第一金属焊垫之间的第一金属焊垫距离等于在第二轴相邻的任两个该第一金属焊垫之间的第二金属焊垫距离,其中该第一轴垂直于该第二轴与该第一垂直穿孔。

12.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第一轴相邻的任两个该第一金属凸块之间的第一金属凸块距离等于在第二轴相邻的任两个该第一金属凸块之间的第二金属凸块距离,其中该第一轴垂直于该第二轴与该第一垂直穿孔。

13.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第一轴相邻的任两个该第一金属焊垫之间的第一金属焊垫距离等于在该第一轴相邻的任两个该第一金属凸块之间的第一金属凸块距离。

14.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第二轴相邻的任两个该第一金属焊垫之间的第二金属焊垫距离等于在该第二轴相邻的任两个该第一金属凸块之间的第二金属凸块距离,其中该第一轴垂直于该第二轴与该第一垂直穿孔。

15.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第一轴相邻的任两个该第二金属凸块之间的第一金属凸块距离等于在第二轴相邻的任两个该第二金属凸块之间的第二金属凸块距离,其中该第一轴垂直于该第二轴与该第一垂直穿孔。

16.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第一轴相邻的任两个该第二金属焊垫之间的第一金属焊垫距离等于在该第一轴相邻的任两个该第二金属凸块之间的第一金属凸块距离。

17.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第二轴相邻的任两个该第二金属焊垫之间的第二金属焊垫距离等于在该第二轴相邻的任两个该第二金属凸块之间的第二金属凸块距离,其中该第一轴垂直于该第二轴与该第一垂直穿孔。

18.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,该多个第二金属焊垫的数量不同于该多个第二金属凸块的数量。

19.较佳地,为了让上下层的结合更为紧固,相邻的任两个该第一上表面对位结构的形状或指向不同。

20.较佳地,为了让上下层的结合更为紧固,相邻的任两个该第二下表面对位结构的形状或指向不同。

21.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个第二上表面对位结构的数量与该多个第二下表面对位结构的数量相同。

22.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,该多个第二上表面对位结构的数量与该多个第二下表面对位结构的数量不同。

23.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个第一金属焊垫与该多个第一上表面对位结构具有一对一的对应关系。

24.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个第二金属焊垫与该多个第二上表面对位结构具有一对一的对应关系。

25.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个第二金属凸块与该多个第二下表面对位结构具有一对一的对应关系。

26.较佳地,为了让上下层的结合更为紧固,该多个第二金属焊垫与该多个第二上表面对位结构具有一对多的对应关系。

27.较佳地,为了让上下层的结合更为紧固,该多个第二金属凸块与该多个第二下表面对位结构具有一对多的对应关系。

28.较佳地,为了结合上下层,该多个第一上表面对位结构为第一突起结构,该多个第二下表面对位结构为相应于该第一突起结构的第一凹陷结构。

29.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个第二上表面对位结构为该第一突起结构。

30.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,该多个第二上表面对位结构为不同于该第一突起结构的第二突起结构。

31.较佳地,为了提供积木式的封装结构堆迭,该第二层的一个该第二半导体封装结构堆迭于该第一层的两个该第一半导体封装结构之上。

32.较佳地,为了提供积木式的封装结构堆迭,该第i层的一个该第二半导体封装结构堆迭于该第i-1层的两个该第二半导体封装结构之上。

33.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,该第二层所包含的两个第二半导体封装结构的厚度不同。

34.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,该第n层所包含的两个第二半导体封装结构的厚度不同。

35.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,该第一层的厚度与该第二层的厚度不同。

36.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,在该n层当中有两层的厚度不同。

37.较佳地,为了确保电连接,在互相连接的至少一个该第一金属焊垫与至少一个该第二金属凸块之间具有导电胶。

38.较佳地,为了确保电连接,在互相连接的第i-1层的至少一个该第二金属焊垫与第i层的至少一个该第二金属凸块之间具有导电胶。

39.较佳地,为了确保电连接,在多个该第一金属焊垫与该第一填充料层的上表面之间具有多个预留空间,以放置至少一个该第二金属凸块与该导电胶。

40.较佳地,为了确保电连接,至少一个该第二金属焊垫与该第二填充料层的上表面

之间具有预留的空间,以放置至少一个该第二金属凸块与该导电胶。

41.较佳地,为了确保电连接,该多个第一金属焊垫与该多个第二金属凸块的形状相应。

42.较佳地,为了确保电连接,该第i-1层所包含的该多个第二金属焊垫与该第i层所包含的该多个第二金属凸块的形状相应。

43.根据本技术的一实施例,提供一种半导体封装结构,其特征在于,包含:基板,其中该基板之中包含互连结构;该基板之下的多个金属凸块,分别连接至该互连结构所包含的电路;至少一个微电子元器件,该至少一个微电子元器件贴装至该基板,该至少一个微电子元器件的电路连接至该互连结构所包含的电路;在该基板之上的填充料层,用于封装包覆该至少一个微电子元器件;在该填充料层之上的多个金属焊垫与多个上表面对位结构;以及在该填充料层之中的多个垂直穿孔与其中的金属,用于连接该多个金属焊垫与该互连结构所包含的电路。

44.较佳地,为了结合上下层,该基板还包含多个下表面对位结构。

45.较佳地,为了让微电子元器件的电路无须再绕经底下的互连结构才能连接到上方的金属焊垫,其中至少一个该垂直穿孔与其中的金属用于连接该金属焊垫与该至少一个微电子元器件的上面的电路。

46.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个金属焊垫的数量等于该多个金属凸块的数量。

47.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第一轴相邻的任两个该金属焊垫之间的第一金属焊垫距离等于在第二轴相邻的任两个该金属焊垫之间的第二金属焊垫距离,其中该第一轴垂直于该第二轴与该垂直穿孔。

48.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第一轴相邻的任两个该金属凸块之间的第一金属凸块距离等于在第二轴相邻的任两个该金属凸块之间的第二金属凸块距离,其中该第一轴垂直于该第二轴与该垂直穿孔。

49.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第一轴相邻的任两个该金属焊垫之间的第一金属焊垫距离等于在该第一轴相邻的任两个该金属凸块之间的第一金属凸块距离。

50.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第二轴相邻的任两个该金属焊垫之间的第二金属焊垫距离等于在该第二轴相邻的任两个该金属凸块之间的第二金属凸块距离,其中该第一轴垂直于该第二轴与该垂直穿孔。

51.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,该多个金属焊垫的数量不同于该多个金属凸块的数量。

52.较佳地,为了让上下层的结合更为紧固,相邻的任两个该上表面对位结构的形状或指向不同。

53.较佳地,为了让上下层的结合更为紧固,相邻的任两个该下表面对位结构的形状或指向不同。

54.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个上表面对位结构的数量与该多个下表面对位结构的数量相同。

55.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,该多个上表

面对位结构的数量与该多个下表面对位结构的数量不同。

56.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个金属焊垫与该多个上表面对位结构具有一对一的对应关系。

57.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个金属凸块与该多个下表面对位结构具有一对一的对应关系。

58.较佳地,为了让上下层的结合更为紧固,该多个金属焊垫与该多个上表面对位结构具有一对多的对应关系。

59.较佳地,为了让上下层的结合更为紧固,该多个金属凸块与该多个下表面对位结构具有一对多的对应关系。

60.较佳地,为了结合上下层,该多个上表面对位结构为突起结构,该多个下表面对位结构为相应于该突起结构的凹陷结构。

61.较佳地,为了确保电连接,在多个该金属焊垫与该填充料层的上表面之间具有多个预留空间,用以放置另一个该半导体封装结构的该多个金属凸块与导电胶。

62.根据本技术的一实施例,提供一种三维立体封装结构的制作方法,其特征在于,包含:提供第一层,其中该第一层包含至少一个第一半导体封装结构,其中该至少一个第一半导体封装结构之上具有多个第一金属焊垫与多个第一上表面对位结构,该至少一个第一半导体封装结构之下具有多个第一金属凸块;提供第二层,其中该第二层包含至少一个第二半导体封装结构,其中该至少一个第二半导体封装结构之上具有多个第二金属焊垫与多个第二上表面对位结构,该至少一个第二半导体封装结构之下具有多个第二金属凸块与多个第二下表面对位结构;以及将该第二层所包含的该第二半导体封装结构放置与连接该第一层的该第一半导体封装结构之上,其中该第二层的至少一个该第二金属凸块与该第一层的至少一个该第一金属焊垫相连接,其中该第二层的至少一个该第二下表面对位结构与该第一层的至少一个该第一上表面对位结构相连接。

63.较佳地,为了确保电连接,在将该第二层所包含的该第二半导体封装结构放置与连接该第一层的该第一半导体封装结构之前,更包含在该第一金属焊垫所相应的预留空间中放置导电胶。

64.较佳地,为了逐步测试封装结构以尽早发现问题,在将该第二层所包含的该第二半导体封装结构放置与连接该第一层的该第一半导体封装结构之后,更包含对该三维立体封装结构进行测试。

65.较佳地,为了提供更高的面积利用率与封装密度,该三维立体封装结构的制作方法,其特征在于,更包含:提供第三层至第n层,其中n为大于或等于3的正整数,其中该第三层至该第n层包含至少一个该第二半导体封装结构;以及将该第三层至该第n层当中的每一个第i层所包含的该第二半导体封装结构放置与连接第i-1层的第二半导体封装结构之上,其中i为3至n当中的正整数;其中每一个该第i层的至少一个该第二金属凸块与该第i-1层的至少一个该第二金属焊垫相连接,其中每一个该第i层的至少一个该第二下表面对位结构与该第i-1层的至少一个该第二上表面对位结构相连接。

66.较佳地,为了逐步测试封装结构以尽早发现问题,其特征在于,在将该每一个第i层所包含的该第二半导体封装结构放置与连接该第i-1层的第二半导体封装结构之后,更包含对该三维立体封装结构进行测试,当测试不通过时,进行报警。

67.较佳地,为了增进三维立体封装结构的保护,减少后续水气或外界对其影响,该三维立体封装结构的制作方法,其特征在于,更包含:将该三维立体封装结构进行塑封。

68.较佳地,为了尽早解决问题,当测试异常时,进行快速的进行相关部件的更换动作。

69.由于采用上述方案,本发明的有益效果为:本技术提供可实现包含多个封装结构的三维堆迭封装结构,提高了封装密度,减少了贴装的面积,降低了贴片难度。由于半导体封装结构的设计规格的一致性,可以实现多类芯片、集成电路或微电子元器件不同组合的三维立体封装结构。结合之后,通过金属与金属键合、回流或回流焊等方式,实现两个以上的半导体封装结构的直接互连互通。最后,还可以通过塑封体将整个三维立体封装结构保护起来,减少后续水气或外界对其影响。

附图说明

70.图1a至图1g分别为根据本技术一实施例的三维立体封装结构100的剖面示意图。

71.图2a为根据本技术一实施例的半导体封装结构110的俯视示意图。

72.图2b为根据本技术一实施例的半导体封装结构110的俯视示意图。

73.图2c为根据本技术一实施例的半导体封装结构110的仰视示意图。

74.图2d为根据本技术一实施例的半导体封装结构110的仰视示意图。

75.图3为根据本技术一实施例的三维立体封装结构300的俯视示意图。

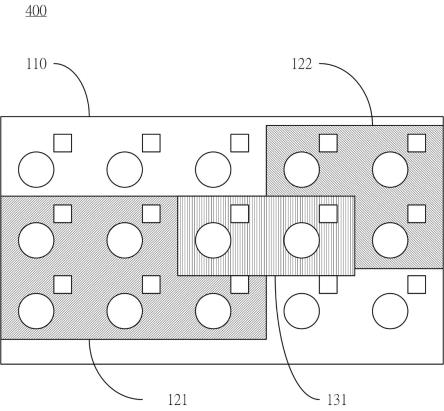

76.图4为根据本技术一实施例的三维立体封装结构400的俯视示意图。

77.图5a为根据本技术一实施例的半导体封装结构的金属焊垫与上表面对位结构的俯视示意图。

78.图5b为根据本技术一实施例的半导体封装结构的金属焊垫与上表面对位结构的俯视示意图。

79.图5c为根据本技术一实施例的半导体封装结构的金属焊垫与上表面对位结构的俯视示意图。

80.图6为根据本技术一实施例的半导体封装结构110的一剖面示意图。

81.图7为根据本技术一实施例的半导体封装结构120的一剖面示意图。

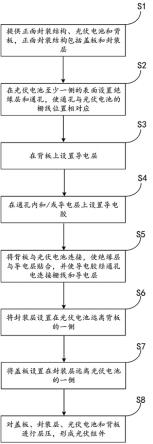

82.图8为根据本技术一实施例的半导体封装结构的制作方法900的一流程示意图。

83.图9为根据本技术一实施例的半导体封装结构的制作方法1000的一流程示意图。

84.图10为根据本技术一实施例的三维立体封装结构的制作方法1100的一流程示意图。

具体实施方式

85.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本创作中的实施例,本领域普通技术人员在没有做出创造性劳动的前提下所得到的所有其它实施方式,都属于本创作所保护的范围。

86.本创作之说明书和权利要求以及图式中的术语“第一”“第二”“第三”等(如果存在)系用于区别类似之对象,而不必用于描述特定的顺序或先后次序。应当理解,该等描述

之对象在适当情况下可以互换。在本创作之描述中,“复数个”之含义是两个或两个以上,除非另有明确具体地限定。此外,术语“包括”和“具有”以及它们的任何变形,意图在于覆盖不排它的包含。图式中所示的一些方框图是功能实体,不一定必须与物理或逻辑上独立的实体相对应。可以采用软件形式来实现该等功能实体,或在一个或复数个硬件电路或集成电路中实现该等功能实体,或在不同网络和/或处理器装置和/或微控制器装置中实现该等功能实体。

87.在本创作之描述中,需要理解的是,术语“中心”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示之方位或位置关系为基于附图所示之方位或位置关系,仅是为了便于描述本创作和简化描述,而不是指示或暗示所指之装置或组件必须具有特定之方位、以特定之方位构造和操作,是故不能理解为对本创作之限制。

88.在本创作之描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,亦可以系可拆卸连接,或一体地连接;可以系机械连接,亦可以系电连接或可以相互通讯;可以系直接相连,亦可以藉由中间媒介间接相连,可以系两个组件内部之连通或两个组件之相互作用关系。对于本领域之普通技术人员而言,可以根据具体情况理解前述术语在本创作中之具体含义。

89.为使本创作之目的、特征和优点能够更加明显易懂,下面结合图式和具体实施方式对本创作作进一步详细之说明。

90.本创作所欲提供的是一种三维立体封装结构,该三维立体封装结构包含至少两个堆迭层,或包含n个堆迭层。在每一堆迭层当中,至少包含一个半导体封装结构。为了方便说明起见,将最下方的堆迭层称之为第一层。相邻于第一层之上的堆迭层称为第二层。依此类推,第n层位于第n-1层之上,其中n为大于或等于2的正整数。

91.在一实施例当中,以第i层所属的半导体封装结构而言,其下表面包含有多个第i金属凸块或金属垫,可以形成二维度的第i金属凸块阵列,用于和第i-1层所属的半导体封装结构的电路相连。上述的i可以是2至n-1的正整数。

92.第i层所属的半导体封装结构的下表面还包含多个第i下表面对位机构,用于和第i-1层所属的半导体封装结构的多个第i-1上表面对位机构彼此结合,用于固定第i层所属的半导体封装结构与相应的第i-1层所属的半导体封装结构,使其不会彼此滑动。本领域普通技术人员可以理解到,由于下方已经没有相应的半导体封装结构,最下方的第一层所属的半导体封装结构的下表面可以不包含多个第一下表面对位机构。

93.类似地,第i层所属的半导体封装结构的上表面包含多个金属焊垫,可以形成二维度的第i金属焊垫阵列,用于和第i 1层所属的半导体封装结构的第i 1金属凸块阵列相连。在每一个该第i金属焊垫之上,可以具有预留的空间容纳相应的第i 1金属凸块。在一实施例当中,该预留的空间较相应的金属凸块还要稍大。该预留的空间还可以容纳少许的导电胶(例如银胶)或焊料以便连接该金属凸块与金属焊垫。

94.第i层所属的半导体封装结构的上表面还包含多个第i上表面对位机构,用于和第i 1层所属的半导体封装结构的多个第i 1下表面对位机构彼此结合,用于固定第i层所属的半导体封装结构与相应的第i 1层所属的半封装导体结构,使其不会彼此滑动。

95.第i层所属的每一个半导体封装结构当中可以包含一或多个微电子元器件。这些微电子元器件可以包含但不限于下列:主动微电子元器件、被动微电子元器件、集成电路

等。上述的微电子元器件可以贴装在一基板之上,并且位于一填充料层之内,被该填充料层包封保护。

96.该基板当中具有一个互连结构。该互连结构用于连接至少一部份的该第i金属凸块阵列、上述的微电子元器件、以及至少一部分的第i金属焊垫阵列。本领域普通技术人员可以理解到,上述的互连结构可以包含多个重布线层(rdl,re-distribution layer)。上述的互连结构可以包含一或多层金属层,每一层金属层皆具有电路。相邻的金属层之间具有绝缘层。互连结构内具有穿过绝缘层的垂直电路,用于连接两个金属层之间的电路。

97.该填充料层当中可以具有多个垂直穿孔,内有电路用于连接上述的第i金属焊垫与该互连结构当中的电路。此外,上述的垂直穿孔内的电路也可以用于连接上述的第i金属焊垫与微电子元器件的电路接口。

98.微电子元器件可以具有多个电路接口,利用多种方式之一来连接该互连结构当中的电路。例如元器件具有多个引脚,或具有球格阵列的焊垫,可以焊接到该互连结构当中的焊垫。又例如元器件可以利用金属打线的方式,来连接到该互连结构当中的电路。

99.本领域普通技术人员可以理解到,在一范例当中,微电子元器件的电路可以直接透过向上的垂直穿孔,连接到第i金属焊垫。在另一范例当中,微电子元器件的电路可以先经过互连结构的电路,再透过向上的垂直穿孔,连接到第i金属焊垫。

100.在一实施例当中,第i 1层的半导体封装结构的电路,可以依序经由第i金属焊垫、第i层的半导体封装结构的垂直穿孔、第i层的半导体封装结构的互连结构、与第i金属凸块,连接到第i-1层的半导体封装结构的电路。这连续的电路之间并不经过第i层的半导体封装结构内的微电子元器件。

101.在另一实施例当中,第i 1层的半导体封装结构的电路,可以依序经由第i金属焊垫、第i层的半导体封装结构的垂直穿孔、第i层的半导体封装结构内的微电子元器件、第i层的半导体封装结构的互连结构、与第i金属凸块,连接到第i-1层的半导体封装结构的电路。

102.在更一实施例当中,第i 1层的半导体封装结构的电路,可以依序经由第i金属焊垫、第i层的半导体封装结构的垂直穿孔、第i层的半导体封装结构的互连结构、第i层的半导体封装结构内的微电子元器件、第i层的半导体封装结构的互连结构、与第i金属凸块,连接到第i-1层的半导体封装结构的电路。

103.请参考图1a所示,其为根据本技术一实施例的三维立体封装结构100的剖面示意图。该三维立体封装结构100包含上下两层,下方的第一层具有单一个半导体封装结构110。上方的第二层具有两个半导体封装结构121与122。在未堆迭结合之前,第一层半导体封装结构110与第二层半导体封装结构121的厚度可以是相等的。半导体封装结构121与122的厚度可以是相等的。半导体封装结构121与122分别连接了不同数量的第一金属焊垫。在一范例当中,半导体封装结构110的所有第一金属焊垫均连接到第二层的半导体封装结构121与122。半导体封装结构121与122可以是相邻的。本领域普通技术人员可以理解到,虽然图1a所示的第二层只有两个半导体封装结构121与122,但本技术并不限定每一层的半导体封装结构的数量。

104.请参考图1b所示,其为根据本技术一实施例的三维立体封装结构100的剖面示意图。和图1a所示的实施例相比,图1b所示的半导体封装结构123与122并非相邻的。半导体封

装结构110的所有第一金属焊垫并未全部连接到第二层的半导体封装结构123与122。半导体封装结构123并未贴齐半导体封装结构110的边界。换言之,第二层的平面投影面积,可以小于第一层的平面投影面积。推广来说,第i 1层的平面投影面积,可以小于第i层的平面投影面积。

105.请参考图1c所示,其为根据本技术一实施例的三维立体封装结构100的剖面示意图。和图1a所示的实施例相比,图1c所示的第二层的半导体封装结构124与125的厚度要小于第一层的半导体封装结构110。本领域普通技术人员可以理解到,任两层的半导体封装结构厚度可以是不同的,但同一层的多个半导体封装结构的彼此厚度可以是相同的。

106.请参考图1d所示,其为根据本技术一实施例的三维立体封装结构100的剖面示意图。和图1a所示的实施例相比,图1d所示的第二层的半导体封装结构127与122的厚度是不同的。在一实施例当中,最上一层的多个半导体封装结构厚度可以是不同的。在另一实施例当中,当第i 1层的半导体封装结构未堆迭到第i层的某一个半导体封装结构时,该半导体封装结构的厚度可以与第i层的其他半导体封装结构厚度不同。

107.请参考图1e所示,其为根据本技术一实施例的三维立体封装结构100的剖面示意图。和图1a所示的实施例相比,图1e所示的第一层包含两个半导体封装结构111与112。第二层的半导体封装结构128同时连接到第一层的两个半导体封装结构111与112。如上所述,第二层的平面投影面积,可以小于第一层的平面投影面积。推广来说,第i 1层的平面投影面积,可以小于第i层的平面投影面积。

108.请参考图1f所示,其为根据本技术一实施例的三维立体封装结构100的剖面示意图。和图1e所示的实施例相比,图1f所示的第一层包含两个不相邻的半导体封装结构111与112。第二层的半导体封装结构128同时连接到第一层不相邻的两个半导体封装结构111与112。当上一层的半导体封装结构128的强度够大时,可以出现下方是空隙的情况。

109.请参考图1g所示,其为根据本技术一实施例的三维立体封装结构100的剖面示意图。和图1a所示的实施例相比,图1g所示的实施例还包含了第三层。第三层包含了三个半导体封装结构131、132与133。如前所述,本领域普通技术人员可以理解到,本技术所包含的三维立体封装结构100可以包含多层结构,可以不只三层。

110.请参考图2a所示,其为根据本技术一实施例的半导体封装结构110的俯视示意图。该半导体封装结构110的上表面包含多个金属焊垫220与多个上表面对位结构210。如图2a所示,该多个金属焊垫220组成一个二维金属焊垫阵列。图2a的水平轴或称为第一轴,图2a的垂直轴或称为第二轴,第一轴与第二轴彼此垂直。该二维金属焊垫阵列相应于该第一轴与该第二轴,该半导体封装结构110的边缘为矩形,也分别平行于该第一轴与该第二轴。

111.如图2a所示,每一个该金属焊垫220的面积可以是相同的。该金属焊垫220的形状可以是圆形,也可以是矩形、正方形、菱形或其他的形状。任两个相邻的金属焊垫220在第一轴的第一金属焊垫距离221是相同的。同样地,任两个相邻的金属焊垫220在第二轴的第二金属焊垫距离222是相同的。在一实施例当中,第一金属焊垫距离221与第二金属焊垫距离222通常也是相同的。

112.如图2a所示,该多个上表面对位结构210也形成一个对位结构阵列。该对位结构阵列相应于该第一轴与该第二轴。任两个相邻的对位结构210在第一轴的第一对位结构距离211是相同的。同样地,任两个相邻的对位结构210在第二轴的第二对位结构距离212是相同

的。在一实施例当中,第一对位结构距离211与第二对位结构距离212通常也是相同的。

113.图2a所示的金属焊垫与对位结构具有一对一的相应关系。第一金属焊垫距离221可以等于第一对位结构距离211。第二金属焊垫距离222可以等于第二对位结构距离212。然而,在其他实施例当中,金属焊垫与对位结构可以具有一对多的相应关系。

114.请参考图2b所示,其为根据本技术一实施例的半导体封装结构110的俯视示意图。和图2a所示的实施例相比,图2b所示的实施例具有两种对位结构210,在第一轴或第二轴上相邻的对位结构210可以具有不同的形状。本领域普通技术人员可以理解到,尽管图2b使用正方形与三角形来表示不同的对位结构210,但本技术并不限定对位结构210的立体形状,也不限定对位结构210是突起的还是凹陷的,只需要该对位结构210可以与上一层的对位结构结合即可。

115.请参考图2c所示,其为根据本技术一实施例的半导体封装结构110的仰视示意图。该半导体封装结构110的下表面包含多个金属凸块230,形成一个二维的金属凸块阵列,相应于上述的第一轴与第二轴。在第一轴上任两个相邻的两个金属凸块230间隔皆为第一金属凸块距离231。在第二轴上任两个相邻的两个金属凸块230间隔皆为第二金属凸块距离232。

116.如图2a与图2c所示,该半导体封装结构110的该金属焊垫阵列与该金属凸块阵列所包含的元素数量是相同的。第一金属凸块距离231等于第一金属焊垫距离221,第二金属凸块距离232等于第二金属焊垫距离222。每一个金属凸块230投影可以对应到一个金属焊垫220。该金属凸块230的形状可以是圆形,也可以是矩形、正方形、菱形或其他的形状。金属凸块230的形状与大小与金属焊垫220相同。

117.然而,本领域普通技术人员可以理解到,该半导体封装结构110的该金属焊垫阵列与该金属凸块阵列所包含的元素数量可以是不同的。第一金属凸块距离231可以不同于第一金属焊垫距离221,第二金属凸块距离232可以不同于第二金属焊垫距离222。每一个金属凸块230投影可以不对应到一个金属焊垫220。金属凸块230的形状与大小与金属焊垫220不同。

118.请参考图2d所示,其为根据本技术一实施例的半导体封装结构110的仰视示意图。为了方便说明起见,上表面的金属焊垫220的投影以虚线来表示。如前所述,该半导体封装结构110的该金属焊垫阵列与该金属凸块阵列所包含的元素数量可以是不同的。第一金属凸块距离231可以不同于第一金属焊垫距离221,第二金属凸块距离232可以不同于第二金属焊垫距离222。每一个金属凸块230投影可以不对应到一个金属焊垫220。金属凸块230的形状与大小与金属焊垫220不同。

119.请参考图3所示,其为根据本技术一实施例的三维立体封装结构300的俯视示意图。该三维立体封装结构300包含两层,第一层包含半导体封装结构110,第二层包含半导体封装结构121与122。如图3所示,半导体封装结构121与122的金属焊垫阵列的规格与半导体封装结构110的金属焊垫阵列的规格是相同的。同样地,半导体封装结构121与122的上表面对位结构阵列的规格与半导体封装结构110的上表面对位结构阵列的规格是相同的。

120.尽管在图3当中并未示出,半导体封装结构110的金属焊垫阵列的规格与半导体封装结构121与122的金属凸块阵列的规格是相同的。半导体封装结构121与122的上表面对位结构的规格与半导体封装结构110的下表面对位结构的规格是相同的。因此,半导体封装结

构121与122才能堆迭在半导体封装结构110之上。

121.本领域普通技术人员可以理解到,在此提到的金属凸块阵列与金属焊垫阵列的规格,包含了任两个元素在第一轴的距离、在第二轴的距离、以及元素的投影面积的形状与大小。当这三个参数相符时,可以说它们的规格是相同的。在此提到的上表面对位结构的规格与下表面对位结构的规格相符,包含其排列的投影形状与距离相同,以及每个元素能与相对应的元素结合。

122.当第i 1层的半导体封装结构的金属凸块阵列与下表面对位结构的规格,和第i层的半导体封装结构的金属焊垫阵列与上表面对位结构的规格相符时,第i 1层的半导体封装结构可以堆迭在第i层的半导体封装结构之上。换言之,当第i 1层的下表面规格(金属凸块阵列与下表面对位结构的规格)与第i层的上表面规格(金属焊垫阵列与上表面对位结构的规格)相符时,第i 1层的半导体封装结构可以堆迭在第i层的半导体封装结构之上。但是第i层的半导体封装结构的上表面规格未必与下表面规格相同,例如图2d所示的实施例。

123.请参考图4所示,其为根据本技术一实施例的三维立体封装结构400的俯视示意图。该三维立体封装结构400包含三层,第一层包含半导体封装结构110,第二层包含半导体封装结构121与122,第三层包含半导体封装结构131。该三维立体封装结构400的第一层与第二层如该三维立体封装结构300。半导体封装结构131堆迭于半导体封装结构121与122之上。

124.请参考图5a所示,其为根据本技术一实施例的半导体封装结构的金属焊垫与上表面对位结构的俯视示意图。如图5a所示,一个金属焊垫220可以对应到四个上表面对位结构210。四个上表面对位结构210分别位于该金属焊垫220的上下左右等距离处。尽管在图5a当中,这四个上表面对位结构210的投影形状都相同,但在某些实施例中,这四个上表面对位结构210的投影形状或指向可以不同。例如这四个上表面对位结构210可以分别是相同形状的等腰三角形或正三角形,其中一个锐角指向金属焊垫220。在另一例当中,这四个上表面对位结构210可以分别是三角形、矩形、菱形、梯形。

125.请参考图5b所示,其为根据本技术一实施例的半导体封装结构的金属焊垫与上表面对位结构的俯视示意图。如图5b所示,一个金属焊垫220可以对应到八个上表面对位结构210,分别位于该金属焊垫220的八个方位。

126.请参考图5c所示,其为根据本技术一实施例的半导体封装结构的金属焊垫与上表面对位结构的俯视示意图。如图5c所示,一个金属焊垫220可以对应到两种上表面对位结构210a与210b。这四个上表面对位结构形成一个正方形,在第一轴相邻的两个上表面对位结构是不同的,在第二轴相邻的两个上表面对位结构是不同的。

127.本领域普通技术人员可以理解到,尽管图5a至图5c所示的实施例为半导体封装结构的上表面规格的一部分,但也可以对应到半导体封装结构的下表面规格的一部分,只要将金属焊垫220换成为金属凸块230,上表面对位结构换成为下表面对位结构。

128.请参考图6所示,其为根据本技术一实施例的半导体封装结构110的一剖面示意图。该半导体封装结构110包含基板620,与贴装在基板620之上的三个微电子元器件630、640、与650。该基板620当中具有互连结构,互连结构可以包含多个重布线层。微电子元器件630、640、与650的电路可以透过球格阵列632、金属打线634、与引脚连接到互连结构的电路。在该基板620的下方包含多个金属凸块230。这些金属凸块230也连接到上述的互连结

构。

129.在基板之上包含填充料层660,用于包覆封装该微电子元器件630、640、与650。在填充料层600的上表面包含多个上表面对位结构210,以及多个金属焊垫220和对应的预留空间。填充料层具有一或多个垂直穿孔615,其中具有电路连接上述的金属焊垫220与互连结构的电路。填充料层具有一或多个垂直穿孔616,其中具有电路连接上述的金属焊垫220与微电子元器件650上表面的背部金属接脚。由于微电子元器件630遮挡住上方的金属焊垫220与下方的互连结构的联机,因此某些金属焊垫220并不连接到下方的互连结构。

130.请参考图7所示,其为根据本技术一实施例的半导体封装结构120的一剖面示意图。和图6所示的实施例不同,图7所示的半导体封装结构120的下表面规格与上表面规格不相符。半导体封装结构120包含了多个下表面对囗结构232。由于这些下表面对位结构232是凹陷的结构,基板620中的互连结构在设计时,可能需要避开这些下表面对位结构232。

131.请参考图8所示,其为根据本技术一实施例的半导体封装结构的制作方法900的一流程示意图。该半导体封装结构的制作方法900可以用于制作图6所示的半导体封装结构110。该半导体封装结构的制作方法900开始于步骤910。

132.步骤910:提供具有第一互连结构以及与该第一互连结构相连的多个第一金属凸块的第一基板。该多个第一金属凸块可以参考图6所示的金属凸块230。该第一基板可以为图6所示的基板620。

133.步骤920:将一或多个微电子元器件贴装到该第一基板,并且将其连接到该第一互连结构的电路。该一或多个微电子元器件可以参考图6所示的微电子元器件630、640和650。

134.步骤930:在该第一基板上形成第一填充料层,以及该第一填充料层之上的多个第一上表面对位结构。该第一填充料层可以参考图6所示的填充料层660。该多个第一上表面对位结构可以参考图6所示的上表面对位结构210。

135.步骤940:在该第一填充料层制作多个第一垂直穿孔,以连接该第一互连结构的电路或该微电子元器件,并且在该多个第一垂直穿孔内注入金属,以及在该多个第一穿孔之上形成多个第一金属焊垫与其上预留的空间。该第一金属焊垫可以参考图6所示的金属焊垫220。该多个第一垂直穿孔与金属可以参考图6所示的垂直穿孔615与616。

136.请参考图9所示,其为根据本技术一实施例的半导体封装结构的制作方法1000的一流程示意图。该半导体封装结构的制作方法1000可以用于制作图7所示的半导体封装结构120。该半导体封装结构的制作方法1000开始于步骤1010。

137.步骤1010:提供具有第二互连结构以及与该第二互连结构相连的多个第二金属凸块的第二基板。该多个第一金属凸块可以参考图7所示的金属凸块230。该第一基板可以为图7所示的基板620。

138.步骤1015:在该第二基板的下表面形成多个第二下表面对位结构。该第二下表面对位结构可以为图7所示的下表面对位结构232。

139.步骤1020:将一或多个微电子元器件贴装到该第二基板,并且将其连接到该第二互连结构的电路。该一或多个微电子元器件可以参考图7所示的微电子元器件740和750。

140.步骤1030:在该第二基板上形成第二填充料层,以及该第二填充料层之上的多个第二上表面对位结构。该第二填充料层可以参考图7所示的填充料层660。该多个第二上表面对位结构可以参考图7所示的上表面对位结构210。

141.步骤1040:在该第二填充料层制作多个第二垂直穿孔,以连接该第二互连结构的电路或该微电子元器件,并且在该多个第二垂直穿孔内注入金属,以及在该多个第二穿孔之上形成多个第二金属焊垫与其上预留的空间。该第二金属焊垫可以参考图7所示的金属焊垫220。该多个第一垂直穿孔与金属可以参考图7所示的垂直穿孔615与616。

142.请参考图10所示,其为根据本技术一实施例的三维立体封装结构的制作方法1100的一流程示意图。该三维立体封装结构的制作方法1100可以用于制作前述的三维立体封装结构,具有n层结构,n为大于或等于2的正整数。该三维立体封装结构的制作方法1100开始于步骤1110。本技术并不限定步骤1110与1120的先后顺序。在事先的初始化步骤当中,可以设定变量i=3,i的限制条件为小于或等于n。

143.步骤1110:提供第一层,该第一层包含一个以上的第一半导体封装结构。其中该第一半导体封装结构可以是由半导体封装结构的制作方法900所制作出来的产品。

144.步骤1120:提供第二层,该第二层包含一个以上的第二半导体封装结构。其中该第二半导体封装结构可以是由半导体封装结构的制作方法1000所制作出来的产品。

145.步骤1130:将该第二层的第二半导体封装结构放置与连接至该第一层的第一半导体封装结构之上。本步骤可以包含在该第一层所属的第一金属焊垫相应的预留空间中放置导电胶,以按压的方式将第二层放置上去。接着,流程可以进到步骤1140或步骤1145。

146.可选的步骤1140:测试既有的三维立体封装结构,判断是否测试通过。当测试通过时,流程进到步骤1145。当测试不通过时,流程进到步骤1190。

147.步骤1145:判断是否还有第i层需要堆迭,其中i为小于或等于n的正整数。当需要堆迭第i层时,流程进到步骤1150。否则,流程进到步骤1180。

148.步骤1150:提供第i层,该第i层包含一个以上的第二半导体封装结构。其中该第二半导体封装结构可以是由半导体封装结构的制作方法1000所制作出来的产品。

149.步骤1160:将该第i层的第二半导体封装结构放置与连接至该第i-1层的第二半导体封装结构之上。本步骤可以包含在该第i-1层所属的第二金属焊垫相应的预留空间中放置导电胶,以按压的方式将第i层放置上去。接着,流程可以进到步骤1170。

150.步骤1170:令i=i 1。接着流程回到步骤1140或1145。

151.可选的步骤1180:将完成的三维立体封装结构整体塑封。

152.可选的步骤1190:由于测试不通过,本步骤进行相关部件的更换动作。

153.根据本技术的一实施例,提供一种三维立体封装结构,其特征在于,包含:第一层,该第一层包含至少一个第一半导体封装结构,该第一半导体封装结构还包含:第一基板,其中该第一基板之中包含第一互连结构;多个第一金属凸块,分别连接至该第一互连结构所包含的电路;至少一个第一微电子元器件,该至少一个第一微电子元器件装贴至该第一基板,该至少一个第一微电子元器件的电路连接至该第一互连结构所包含的电路;在该第一基板之上的第一填充料层,用于封装包覆该至少一个第一微电子元器件;在该第一填充料层之上的多个第一金属焊垫与多个第一上表面对位结构;以及在该第一填充料层之中的多个第一垂直穿孔与其中的金属,用于连接该多个第一金属焊垫与该第一互连结构所包含的电路;以及第二层,该第二层包含至少一个第二半导体封装结构,该第二半导体封装结构还包含:第二基板,其中该第二基板之中包含第二互连结构与多个第二下表面对位结构;多个第二金属凸块,分别连接至该第二互连结构所包含的电路;至少一个第二微电子元器件,该

至少一个第二微电子元器件装贴至该第二基板,该至少一个第二微电子元器件的电路连接至该第二互连结构所包含的电路;在该第二基板之上的第二填充料层,用于封装包覆该至少一个第二微电子元器件;在该第二填充料层之上的多个第二金属焊垫与多个第二上表面对位结构;以及在该第二填充料层之中的多个第二垂直穿孔与其中的金属,用于连接该多个第二金属焊垫与该第二互连结构所包含的电路,其中该第二层的至少一个该第二金属凸块与该第一层的至少一个该第一金属焊垫相连接,其中该第二层的至少一个该第二下表面对位结构与该第一层的至少一个该第一上表面对位结构相连接。

154.较佳地,为了提供更高的面积利用率与封装密度,所述的三维立体封装结构,其特征在于,还包含:第三层至第n层,其中n为大于或等于3的正整数,其中该第三层至该第n层当中的第i层,包含至少一个该第二半导体封装结构,i为3至n之间的正整数,其中该第i层的至少一个该第二金属凸块与第i-1层的至少一个该第二金属焊垫相连接,其中该第i层的至少一个该第二下表面对位结构与该第i-1层的至少一个该第二上表面对位结构相连接。

155.较佳地,为了让微电子元器件的电路无须再绕经底下的互连结构才能连接到上方的金属焊垫,至少一个该第一垂直穿孔与其中的金属用于连接该第一金属焊垫与该至少一个第一微电子元器件的上面的电路。

156.较佳地,为了让微电子元器件的电路无须再绕经底下的互连结构才能连接到上方的金属焊垫,其中至少一个该第二垂直穿孔与其中的金属用于连接该第二金属焊垫与该至少一个第二微电子元器件的上面的电路。

157.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个第一金属焊垫的数量等于该多个第一金属凸块的数量。

158.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个第二金属焊垫的数量等于该多个第二金属凸块的数量。

159.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第一轴相邻的任两个该第一金属焊垫之间的第一金属焊垫距离等于在第二轴相邻的任两个该第一金属焊垫之间的第二金属焊垫距离,其中该第一轴垂直于该第二轴与该第一垂直穿孔。

160.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第一轴相邻的任两个该第一金属凸块之间的第一金属凸块距离等于在第二轴相邻的任两个该第一金属凸块之间的第二金属凸块距离,其中该第一轴垂直于该第二轴与该第一垂直穿孔。

161.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第一轴相邻的任两个该第一金属焊垫之间的第一金属焊垫距离等于在该第一轴相邻的任两个该第一金属凸块之间的第一金属凸块距离。

162.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第二轴相邻的任两个该第一金属焊垫之间的第二金属焊垫距离等于在该第二轴相邻的任两个该第一金属凸块之间的第二金属凸块距离,其中该第一轴垂直于该第二轴与该第一垂直穿孔。

163.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第一轴相邻的任两个该第二金属凸块之间的第一金属凸块距离等于在第二轴相邻的任两个该第二金属凸块之间的第二金属凸块距离,其中该第一轴垂直于该第二轴与该第一垂直穿孔。

164.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第一轴相邻的任两个该第二金属焊垫之间的第一金属焊垫距离等于在该第一轴相邻的任两个该第二金

属凸块之间的第一金属凸块距离。

165.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第二轴相邻的任两个该第二金属焊垫之间的第二金属焊垫距离等于在该第二轴相邻的任两个该第二金属凸块之间的第二金属凸块距离,其中该第一轴垂直于该第二轴与该第一垂直穿孔。

166.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,该多个第二金属焊垫的数量不同于该多个第二金属凸块的数量。

167.较佳地,为了让上下层的结合更为紧固,相邻的任两个该第一上表面对位结构的形状或指向不同。

168.较佳地,为了让上下层的结合更为紧固,相邻的任两个该第二下表面对位结构的形状或指向不同。

169.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个第二上表面对位结构的数量与该多个第二下表面对位结构的数量相同。

170.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,该多个第二上表面对位结构的数量与该多个第二下表面对位结构的数量不同。

171.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个第一金属焊垫与该多个第一上表面对位结构具有一对一的对应关系。

172.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个第二金属焊垫与该多个第二上表面对位结构具有一对一的对应关系。

173.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个第二金属凸块与该多个第二下表面对位结构具有一对一的对应关系。

174.较佳地,为了让上下层的结合更为紧固,该多个第二金属焊垫与该多个第二上表面对位结构具有一对多的对应关系。

175.较佳地,为了让上下层的结合更为紧固,该多个第二金属凸块与该多个第二下表面对位结构具有一对多的对应关系。

176.较佳地,为了结合上下层,该多个第一上表面对位结构为第一突起结构,该多个第二下表面对位结构为相应于该第一突起结构的第一凹陷结构。

177.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个第二上表面对位结构为该第一突起结构。

178.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,该多个第二上表面对位结构为不同于该第一突起结构的第二突起结构。

179.较佳地,为了提供积木式的封装结构堆迭,该第二层的一个该第二半导体封装结构堆迭于该第一层的两个该第一半导体封装结构之上。

180.较佳地,为了提供积木式的封装结构堆迭,该第i层的一个该第二半导体封装结构堆迭于该第i-1层的两个该第二半导体封装结构之上。

181.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,该第二层所包含的两个第二半导体封装结构的厚度不同。

182.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,该第n层所包含的两个第二半导体封装结构的厚度不同。

183.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,该第一层的

厚度与该第二层的厚度不同。

184.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,在该n层当中有两层的厚度不同。

185.较佳地,为了确保电连接,在互相连接的至少一个该第一金属焊垫与至少一个该第二金属凸块之间具有导电胶。

186.较佳地,为了确保电连接,在互相连接的第i-1层的至少一个该第二金属焊垫与第i层的至少一个该第二金属凸块之间具有导电胶。

187.较佳地,为了确保电连接,在多个该第一金属焊垫与该第一填充料层的上表面之间具有多个预留空间,以放置至少一个该第二金属凸块与该导电胶。

188.较佳地,为了确保电连接,至少一个该第二金属焊垫与该第二填充料层的上表面之间具有预留的空间,以放置至少一个该第二金属凸块与该导电胶。

189.较佳地,为了确保电连接,该多个第一金属焊垫与该多个第二金属凸块的形状相应。

190.较佳地,为了确保电连接,该第i-1层所包含的该多个第二金属焊垫与该第i层所包含的该多个第二金属凸块的形状相应。

191.根据本技术的一实施例,提供一种半导体封装结构,其特征在于,包含:基板,其中该基板之中包含互连结构;该基板之下的多个金属凸块,分别连接至该互连结构所包含的电路;至少一个微电子元器件,该至少一个微电子元器件贴装至该基板,该至少一个微电子元器件的电路连接至该互连结构所包含的电路;在该基板之上的填充料层,用于封装包覆该至少一个微电子元器件;在该填充料层之上的多个金属焊垫与多个上表面对位结构;以及在该填充料层之中的多个垂直穿孔与其中的金属,用于连接该多个金属焊垫与该互连结构所包含的电路。

192.较佳地,为了结合上下层,该基板还包含多个下表面对位结构。

193.较佳地,为了让微电子元器件的电路无须再绕经底下的互连结构才能连接到上方的金属焊垫,其中至少一个该垂直穿孔与其中的金属用于连接该金属焊垫与该至少一个微电子元器件的上面的电路。

194.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个金属焊垫的数量等于该多个金属凸块的数量。

195.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第一轴相邻的任两个该金属焊垫之间的第一金属焊垫距离等于在第二轴相邻的任两个该金属焊垫之间的第二金属焊垫距离,其中该第一轴垂直于该第二轴与该第一垂直穿孔。

196.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第一轴相邻的任两个该金属凸块之间的第一金属凸块距离等于在第二轴相邻的任两个该金属凸块之间的第二金属凸块距离,其中该第一轴垂直于该第二轴与该第一垂直穿孔。

197.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第一轴相邻的任两个该金属焊垫之间的第一金属焊垫距离等于在该第一轴相邻的任两个该金属凸块之间的第一金属凸块距离。

198.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,在第二轴相邻的任两个该金属焊垫之间的第二金属焊垫距离等于在该第二轴相邻的任两个该金属凸块之

间的第二金属凸块距离,其中该第一轴垂直于该第二轴与该垂直穿孔。

199.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,该多个金属焊垫的数量不同于该多个金属凸块的数量。

200.较佳地,为了让上下层的结合更为紧固,相邻的任两个该上表面对位结构的形状或指向不同。

201.较佳地,为了让上下层的结合更为紧固,相邻的任两个该下表面对位结构的形状或指向不同。

202.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个上表面对位结构的数量与该多个下表面对位结构的数量相同。

203.较佳地,为了丰富三维立体封装结构与半导体封装结构的设计弹性,该多个上表面对位结构的数量与该多个下表面对位结构的数量不同。

204.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个金属焊垫与该多个上表面对位结构具有一对一的对应关系。

205.较佳地,为了简化三维立体封装结构与半导体封装结构的设计,该多个金属凸块与该多个下表面对位结构具有一对一的对应关系。

206.较佳地,为了让上下层的结合更为紧固,该多个金属焊垫与该多个上表面对位结构具有一对多的对应关系。

207.较佳地,为了让上下层的结合更为紧固,该多个金属凸块与该多个下表面对位结构具有一对多的对应关系。

208.较佳地,为了结合上下层,该多个上表面对位结构为突起结构,该多个下表面对位结构为相应于该突起结构的凹陷结构。

209.较佳地,为了确保电连接,在多个该金属焊垫与该填充料层的上表面之间具有多个预留空间,用以放置另一个半导体封装结构的金属凸块与导电胶。

210.根据本技术的一实施例,提供一种三维立体封装结构的制作方法,其特征在于,包含:提供第一层,其中该第一层包含至少一个第一半导体封装结构,其中该至少一个第一半导体封装结构之上具有多个第一金属焊垫与多个第一上表面对位结构,该至少一个第一半导体封装结构之下具有多个第一金属凸块;提供第二层,其中该第二层包含至少一个第二半导体封装结构,其中该至少一个第二半导体封装结构之上具有多个第二金属焊垫与多个第二上表面对位结构,该至少一个第二半导体封装结构之下具有多个第二金属凸块与多个第二下表面对位结构;以及将该第二层所包含的该第二半导体封装结构放置与连接该第一层的该第一半导体封装结构之上,其中该第二层的至少一个该第二金属凸块与该第一层的至少一个该第一金属焊垫相连接,其中该第二层的至少一个该第二下表面对位结构与该第一层的至少一个该第一上表面对位结构相连接。

211.较佳地,为了确保电连接,在将该第二层所包含的该第二半导体封装结构放置与连接该第一层的该第一半导体封装结构之前,更包含在该第一金属焊垫所相应的预留空间中放置导电胶。

212.较佳地,为了逐步测试封装结构以尽早发现问题,在将该第二层所包含的该第二半导体封装结构放置与连接该第一层的该第一半导体封装结构之后,更包含对该三维立体封装结构进行测试,当测试不通过时,进行报警。

213.较佳地,为了提供更高的面积利用率与封装密度,该三维立体封装结构的制作方法,其特征在于,更包含:提供第三层至第n层,其中该第三层至该第n层包含至少一个该第二半导体封装结构;以及将该第三层至该第n层当中的每一个第i层所包含的该第二半导体封装结构放置与连接第i-1层的第二半导体封装结构之上,其中i为3至n当中的正整数;其中每一个该第i层的至少一个该第二金属凸块与该第i-1层的至少一个该第二金属焊垫相连接,其中每一个该第i层的至少一个该第二下表面对位结构与该第i-1层的至少一个该第二上表面对位结构相连接。

214.较佳地,为了逐步测试封装结构以尽早发现问题,其特征在于,在将该每一个第i层所包含的该第二半导体封装结构放置与连接该第i-1层的第二半导体封装结构之后,更包含对该三维立体封装结构进行测试。

215.较佳地,为了增进三维立体封装结构的保护,减少后续水气或外界对其影响,该三维立体封装结构的制作方法,其特征在于,更包含:将该三维立体封装结构进行塑封。

216.较佳地,为了尽早解决问题,当测试异常时,进行相关部件的更换动作。

217.本技术提供可实现包含多个封装结构的三维立体封装结构,提高了封装密度,减少了贴装的面积,降低了贴片难度。由于半导体封装结构的设计规格的一致性,可以实现多类芯片、集成电路或微电子元器件不同组合的三维立体封装结构。结合之后,通过金属与金属键合、回流或回流焊等方式,实现两个以上的半导体封装结构的直接互连互通。最后,还可以通过塑封体将整个三维立体封装结构保护起来,减少后续水气或外界对其影响。

218.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,根据本发明的技术方案及其发明构思加以等同替换或改变,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。