一种三通道l波段vpx信号处理系统

技术领域

1.本实用新型涉及信号处理技术领域,尤其是一种三通道l波段vpx信号处理系统。

背景技术:

2.vpx总线是vita组织于2007年在其vme总线基础上提出的新一代高速串行总线标准。vpx总线的基本规范、机械结构和总线信号等具体内容均在ansi/vita46系列技术规范中定义。vpx总线来源于vme总线,而vme总线诞生于30年前,结合了motorola公司versa总线电气标准和欧式卡机械封装标准,是一种开放式架构,在工业控制、信号处理和国防领域中得到了广泛应用。

3.但是,现有技术中暂无用于三通道l波段的vpx信号处理,现有技术中的vpx信号处理装置采样dbf处理板搭配dsp信号处理板的方式,其投入成本较高。如专利公开号为“cn210627192u”、名称为“vpx信号处理系统”的中国实用新型专利,其通过光纤接口接收信号至第一处理板,信号经第一fpga处理器处理后通过板内串口传输至第二处理板,经第二fpga处理器、数字信号处理器以及交换机处理后通过板外串口输出。第一处理板、第二处理板和电源模块分别安装在底板上,所述机箱内设有与底板适配的槽位,底板安装在所述机箱内,使得所述第一处理板、第二处理板以及电源模块位于机箱内,机箱设有前面板和后面板,前面板和后面板均与第一处理板、第二处理板以及电源模块连接。

4.因此,急需要提出一种结构简单、信号处理可靠的三通道l波段vpx信号处理系统。

技术实现要素:

5.针对上述问题,本实用新型的目的在于提供一种三通道l波段vpx信号处理系统,本实用新型采用的技术方案如下:

6.一种三通道l波段vpx信号处理系统,其包括xc6slx9系列的可编程逻辑器件u79,与可编程逻辑器件u79连接的第一通道电路、第二通道电路和第三通道电路,与可编程逻辑器件u79连接的射频输出电路,与第一通道电路、第二通道电路、第三通道电路和射频输出电路连接的时钟分频电路,以及与可编程逻辑器件u79、射频输出电路,与第一通道电路、第二通道电路、第三通道电路、射频输出电路和时钟分频电路连接的供电电路;所述第二通道电路与第三通道电路的结构相同

7.与现有技术相比,本实用新型具有以下有益效果:

8.(1)本实用新型巧妙地设置了可编程逻辑器件u79、射频输出电路,与第一通道电路、第二通道电路、第三通道电路、射频输出电路和时钟分频电路;通过可编程逻辑器件u79对三个射频通道电路信号通路、射频输出电路以及时钟分频电路进行集中管控,由此实现高集成度多通道整体技术方案。

9.(2)本实用新型的第一通道电路巧妙地设置了第二低功耗宽带射频合成器u74、正交调制器u75、功率放大器u23和射频连接器j33,第二低功耗宽带射频合成器u74产生本振信号,正交调制器u75接收差分中频信号和第二低功耗宽带射频合成器u74过来的本振信号

变换出低失真射频信号,经过功率放大器u23进行功率放大之后输出到射频连接器j33。

10.(3)本实用新型的第二通道电路和第三通道电路通过设置第三低功耗宽带射频合成器u17、差分混频器u18、射频变压器u19、功率放大器u36和带通滤波器lc2,其中,差分混频器u18接收第三低功耗宽带射频合成器u17u17产生的差分本振信号和差分输入信号产生差分中频信号,经过射频变压器u19转换成单端信号,通过功率放大器u36进行功率放大后送入带通滤波器lc2过滤掉中心频率

±

100mhz范围以外的干扰信号送入后端电路。

11.(4)本实用新型巧妙地设置了第一滤波电路和双路滤波电路,以保证射频输出信号可靠;

12.综上所述,本实用新型具有结构简单、信号处理可靠等优点,在信号处理技术领域具有很高的实用价值和推广价值。

附图说明

13.为了更清楚地说明本实用新型实施例的技术方案,下面将对实施例中所需使用的附图作简单介绍,应当理解,以下附图仅示出了本实用新型的某些实施例,因此不应被看作是对保护范围的限定,对于本领域技术人员来说,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

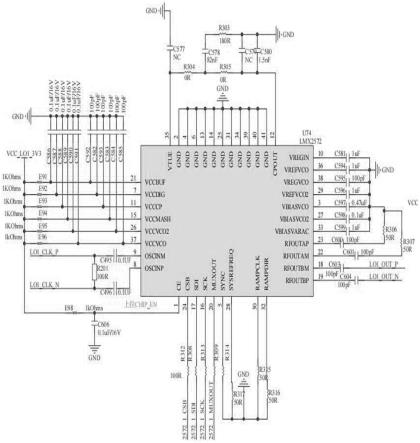

14.图1为本实用新型中第二低功耗宽带射频合成器的原理图。

15.图2为本实用新型中第一通道电路的输入解调电路原理图。

16.图3为本实用新型中第一通道电路的接口电路原理图。

17.图4为本实用新型中第三低功耗宽带射频合成器的原理图。

18.图5为本实用新型中差分混频器u18和射频变压器u19的原理图。

19.图6为本实用新型中功率放大器u36和带通滤波器lc2的原理图。

20.图7为本实用新型中第一低功耗宽带射频合成器的接口电路原理图。

21.图8为本实用新型中第一低功耗宽带射频合成器的原理图。

22.图9为本实用新型中加差分滤波器u28和信号变压器b2的原理图。

23.图10为本实用新型中第一滤波电路和第一射频放大器u2的原理图。

24.图11为本实用新型中第一射频衰减器u3的原理图。

25.图12为本实用新型中增益放大器u1的原理图。

26.图13为本实用新型中第二射频衰减器u6和双路滤波电路的原理图。

27.图14为本实用新型中第三射频衰减器u5的原理图。

28.图15为本实用新型中时钟分频电路原理图。

29.图16为时钟分频接口芯片的原理图。

30.图17为第一时钟分频接口电路原理图。

31.图18为第二时钟分频接口电路原理图。

32.图19为第一fpga接口电路原理图。

33.图20为第二fpga接口电路原理图。

34.图21为fpga芯片第一部分原理图。

35.图22为fpga芯片第二部分原理图。

具体实施方式

36.为使本技术的目的、技术方案和优点更为清楚,下面结合附图和实施例对本实用新型作进一步说明,本实用新型的实施方式包括但不限于下列实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动的前提下所获得的所有其他实施例,都属于本技术保护的范围。

37.实施例

38.如图1至图22所示,本实施例提供了一种三通道l波段vpx信号处理系统,其包括xc6slx9系列的可编程逻辑器件u79,与可编程逻辑器件u79连接的第一通道电路、第二通道电路和第三通道电路,与可编程逻辑器件u79连接的射频输出电路,与第一通道电路、第二通道电路、第三通道电路和射频输出电路连接的时钟分频电路,以及与可编程逻辑器件u79、射频输出电路,与第一通道电路、第二通道电路、第三通道电路、射频输出电路和时钟分频电路连接的供电电路。首先,需要说明的是,本实施例中所述的“第一”、“第二”等序号用语仅用于区分同类部件,不能理解成对保护范围的特定限定。另外,本实施例是基于结构的改进,并未对芯片的软件程序进行改进,其采用常规的程序片段组合便能实现,在此就不予赘述。

39.在本实施例中,为了输出可靠的射频信号,通过设置射频输出电路,其包括依次连接的第一低功耗宽带射频合成器u26、加差分滤波器u28、信号变压器b2、第一滤波电路、第一射频放大器u2、第一射频衰减器u3、增益放大器u1、第二射频衰减器u6、双路滤波电路、第三射频衰减器u5和射频接口j17,以及与加差分滤波器u28连接的射频连接器j28;所述第一低功耗宽带射频合成器u26与可编程逻辑器件u79连接。在本实施例中按照滤波放大本振混频后放大滤波的组合进行设计,必要位置增加衰减器避免信号功率饱和。

40.其中,本实施例的第一滤波电包括依次串联连接的电容c14、电容c15、电容c16、电容c17、电容c18、电阻r7、电容c19和电感l3,跨接在电容c14之间的电感l4,跨接在电容c15之间的电感l5,跨接在电容c16之间的电感l6,跨接在电容c17之间的电感l7,跨接在电容c18之间的电感l8,并联后一端与信号变压器b1连接的电容c6和电容c25,并联后一端连接在电容c14与电容c15之间、且另一端接地的电容c7和电容c26,并联后一端连接在电容c15与电容c16之间、且另一端接地的电容c8和电容c27,并联后一端连接在电容c16与电容c17之间、且另一端接地的电容c9和电容c28,并联后一端连接在电容c17与电容c18之间、且另一端接地的电容c10和电容c30,并联后一端连接在电容c18与电阻r7之间、且另一端接地的电容c11、电容c29和电阻r11,一端连接在电阻r7与电容c19之间、且另一端接地的电阻r12,以及一端连接在电容c19与电感l3之间、且另一端接地的电容c22。在本实施例中,通过设置五阶滤波和t型滤波,以滤除频率超过2150mhz的带外干扰信号。

41.另外,本实施例的双路滤波电路由并联的第二滤波电路和第三滤波电路组成;所述第二滤波电路由串联的第一阶滤波、第二阶滤波、第三阶滤波和第四阶滤波组成;所述第一阶滤波与第二射频衰减器u6连接;所述第四阶滤波与第三射频衰减器u5连接;所述第一阶滤波包括并联连接的电容c42、电感l14和电容c53,并联后输入与电感l14连接的电容c43、电感l15和电容c55,以及并联后一端与第二射频衰减器u6的输出连接、且另一端接地的电容c38、电感l13和电容c39。本实施例通过设置双路的滤波,并且每一回路设置四阶滤波,其作用是组合成一个高性能的70mhz中心频率带宽约38mhz的带通滤波器。

42.在本实施例中,设置了第一通道电路、第二通道电路和第三通道电路,其中第二通道电路和第三通道电路的结构相同。其中,第一通道电路包括与可编程逻辑器件u79连接、且型号为lmx2572的第二低功耗宽带射频合成器u74,与第二低功耗宽带射频合成器u74连接、且型号为adl5375-15的正交调制器u75,与正交调制器u75的输出连接、且型号为qorvo_885062的功率放大器u23,以及与功率放大器u23连接的射频连接器j33。另外,第二通道电路包括与可编程逻辑器件u79连接、且型号为lmx2572的第三低功耗宽带射频合成器u17,与第三低功耗宽带射频合成器u17连接的差分混频器u18,与差分混频器u18连接、且型号为tcm1-63ax的射频变压器u19,与射频变压器u19连接的功率放大器u36,以及与功率放大器u36连接的带通滤波器lc2。在本实施例中,利用第一通道电路、第二通道电路是两个独立的l波段射频到中频的下变频通道,第三通道电路为一个独立的l波段中频到射频的上变频通道。

43.在本实施例中,为了获取时钟信号,该时钟分频电路包括型号为abljo_100mhz的vcxo模块,连接在vcxo模块与可编程逻辑器件u79之间、且型号为adf4002的分频器u59,以及与vcxo模块连接、且型号为sn65lvds108的八通道中继器u57;所述第一通道电路、第二通道电路、第三通道电路和射频输出电路与八通道中继器u57连接。

44.上述实施例仅为本实用新型的优选实施例,并非对本实用新型保护范围的限制,但凡采用本实用新型的设计原理,以及在此基础上进行非创造性劳动而作出的变化,均应属于本实用新型的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。