技术特征:

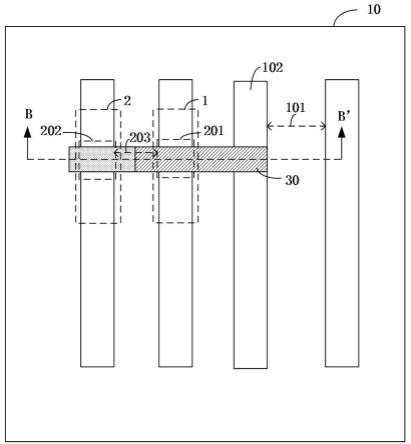

1.一种半导体结构,其特征在于,包括:第一pmos管;第一nmos管,所述第一nmos管的栅极与所述第一pmos管的栅极共用同一第一多晶硅结构;所述第一多晶硅结构包括第一栅极区域及第二栅极区域,所述第一栅极区域与所述第二栅极区域间隔排布;所述第一栅极区域为所述第一pmos管的栅极,所述第二栅极区域为所述第一nmos管的栅极,所述第二栅极区域为n型掺杂区域;所述第一栅极区域与所述第二栅极区域之间的所述第一多晶硅结构内具有第一凹槽。2.根据权利要求1所述的半导体结构,其特征在于,所述第一凹槽的宽度与所述第一多晶硅结构的宽度相同。3.根据权利要求1所述的半导体结构,其特征在于,所述半导体结构还包括衬底,所述衬底内具有浅沟槽隔离结构,所述浅沟槽隔离结构于所述衬底内隔离出多个间隔排布的有源区,所述有源区沿第一方向延伸;所述第一多晶硅结构沿第二方向延伸,所述第二方向与所述第一方向相交;所述第一多晶硅结构横跨至少两个所述有源区;所述第一pmos管还包括源极及漏极,所述第一pmos管的源极及所述第一pmos管的漏极位于同一所述有源区内,且位于所述第一栅极区域相对的两侧;所述第一nmos管还包括源极及漏极,所述第一nmos管的源极及所述第一nmos管的漏极位于同一所述有源区内,且位于所述第二栅极区域相对的两侧。4.根据权利要求3所述的半导体结构,其特征在于,所述半导体结构还包括:第二pmos管,包括栅极、源极及漏极;第二nmos管,包括栅极、源极及漏极;所述第二nmos管的栅极与所述第二pmos管的栅极共用同一第二多晶硅结构;所述第二多晶硅结构包括第三栅极区域及第四栅极区域;所述第三栅极区域与所述第四栅极区域间隔排布;所述第三栅极区域为所述第二pmos管的栅极,所述第四栅极区域为所述第二nmos管的栅极,所述第四栅极区域为n型掺杂区域;所述第三栅极区域与所述第四栅极区域之间的所述第二多晶硅结构内具有第二凹槽;所述第二pmos管的源极及所述第二pmos管的漏极位于同一所述有源区内,且位于所述第三栅极区域相对的两侧;所述第二nmos管的源极及所述第二nmos管的漏极位于同一所述有源区内,且位于所述第四栅极区域相对的两侧。5.根据权利要求4所述的半导体结构,其特征在于,所述半导体结构还包括:第一传输晶体管,包括栅极、源极及漏极;所述第一传输晶体管的栅极横跨所述第一nmos管所在的有源区,所述第一传输晶体管的源极及所述第一传输晶体管的漏极位于所述第一nmos管所在的有源区内,且所述第一传输晶体管与所述第一nmos管共漏极,所述第一传输晶体管的源极位于所述第一传输晶体管的栅极远离所述第一传输晶体管的漏极的一侧;第二传输晶体管,包括栅极、源极及漏极;所述第二传输晶体管的栅极横跨所述第二nmos管所在的有源区,所述第二传输晶体管的源极及所述第二传输晶体管的漏极位于所述第二nmos管所在的有源区内,且所述第二传输晶体管与所述第二nmos管共漏极,所述第二传输晶体管的源极位于所述第二传输晶体管的栅极远离所述第二传输晶体管的漏极的一侧。

6.根据权利要求5所述的半导体结构,其特征在于,所述半导体结构还包括:第一导电插塞,与所述第一多晶硅结构及所述第二pmos管的漏极相接触,以将所述第一多晶硅结构与所述第二pmos管的漏极相连接;第二导电插塞,与所述第二多晶硅结构及所述第一pmos管的漏极相接触,以将所述第二多晶硅结构与所述第一pmos管的漏极相连接;多个第三导电插塞,多个所述第三导电插塞分别与所述第一pmos管的源极、所述第二pmos管的源极、所述第一nmos管的源极、所述第一nmos管的漏极、所述第二nmos管的源极、所述第二nmos管的漏极、所述第一传输晶体管的源极、所述第一传输晶体管的漏极、所述第二传输晶体管的源极及所述第二传输晶体管的漏极一一对应接触;多个第四导电插塞,多个所述第四导电插塞与所述第一传输晶体管的栅极及所述第二传输晶体管的栅极一一对应接触。7.一种半导体结构的制备方法,其特征在于,包括:提供衬底,所述衬底内形成有浅沟槽隔离结构,所述浅沟槽隔离结构于所述衬底内隔离出多个间隔排布的有源区;于所述衬底上形成第一初始多晶硅结构,所述第一初始多晶硅结构横跨至少两个所述有源区,所述第一初始多晶硅结构包括第一栅极区域及第二栅极区域,所述第一栅极区域及所述第二栅极区域均位于所述有源区的正上方,且所述第一栅极区域与所述第二栅极区域间隔排布;于所述第一栅极区域与所述第二栅极区域之间的所述第一初始多晶硅结构内形成第一凹槽;对所述第二栅极区域进行n型掺杂,以得到第一多晶硅结构;其中,所述第一多晶硅结构中的第一栅极区域为第一pmos管的栅极,所述第一多晶硅结构中的第二栅极区域为第一nmos管的栅极;于所述第一多晶硅结构相对两侧的所述有源区内形成源极及漏极。8.根据权利要求7所述的半导体结构的制备方法,其特征在于,于所述衬底上形成第一初始多晶硅结构的同时,还于所述衬底上形成第二初始多晶硅结构,所述第二初始多晶硅结构横跨至少两个所述有源区,所述第二初始多晶硅结构包括第三栅极区域及第四栅极区域,所述第三栅极区域及所述第四栅极区域均位于所述有源区的正上方,且所述第三栅极区域与所述第四栅极区域间隔排布;于所述第一栅极区域与所述第二栅极区域之间的所述第一初始多晶硅结构内形成第一凹槽的同时,还于所述第三栅极区域与所述第四栅极区域之间的所述第二初始多晶硅结构内形成第二凹槽;对所述第二栅极区域进行n型掺杂,以得到第一多晶硅结构的同时,还对所述第四栅极区域进行n型掺杂,以形成第二多晶硅结构;其中,所述第二多晶硅结构中的第三栅极区域为第二pmos管的栅极,所述第二多晶硅结构中的第四栅极区域为第二nmos管的栅极;于所述第一多晶硅结构相对两侧的所述有源区内形成源极及漏极的同时,还于所述第二多晶硅结构相对两侧的有源区内形成源极及漏极。9.根据权利要求8所述的半导体结构的制备方法,其特征在于,于所述衬底上形成第一初始多晶硅结构的同时,还于所述衬底上形成第一传输晶体管

的栅极及第二传输晶体管的栅极;所述第一传输晶体管的栅极横跨所述第一nmos管所在的有源区;所述第二传输晶体管的栅极横跨所述第二nmos管所在的有源区;于所述第一多晶硅结构相对两侧的所述有源区内形成源极及漏极的同时,还于所述第一传输晶体管相对两侧的有源区内及所述第二传输晶体管相对两侧的有源区内形成源极及漏极;所述第一传输晶体管与所述第一nmos管共漏极,所述第二传输晶体管与所述第二nmos管共漏极。10.根据权利要求9所述的半导体结构的制备方法,其特征在于,形成源极及漏极之后,还包括:形成第一导电插塞、第二导电插塞、多个第三导电插塞及多个第四导电插塞;所述第一导电插塞与所述第一多晶硅结构及所述第二pmos管的漏极相接触,以将所述第一多晶硅结构与所述第二pmos管的漏极相连接;所述第二导电插塞与所述第二多晶硅结构及所述第一pmos管的漏极相接触,以将所述第二多晶硅结构与所述第一pmos管的漏极相连接;多个所述第三导电插塞分别与所述第一pmos管的源极、所述第二pmos管的源极、所述第一nmos管的源极、所述第一nmos管的漏极、所述第二nmos管的源极、所述第二nmos管的漏极、所述第一传输晶体管的源极、所述第一传输晶体管的漏极、所述第二传输晶体管的源极及所述第二传输晶体管的漏极一一对应接触;多个所述第四导电插塞与所述第一传输晶体管的栅极及所述第二传输晶体管的栅极一一对应接触。

技术总结

本发明涉及一种半导体结构及其制备方法。所述半导体结构包括:第一PMOS管;第一NMOS管,第一NMOS管的栅极与第一PMOS管的栅极共用同一第一多晶硅结构;第一多晶硅结构包括第一栅极区域及第二栅极区域,第一栅极区域与第二栅极区域间隔排布;第一栅极区域为第一PMOS管的栅极,第二栅极区域为第一NMOS管的栅极,第二栅极区域为N型掺杂区域;第一栅极区域与第二栅极区域之间的第一多晶硅结构内具有第一凹槽。由于第一凹槽将第一栅极区域与第二栅极区域隔开,减少了N型掺杂离子由第二栅极区域向第一栅极区域扩散的扩散路径,从而降低了第一PMOS管的电性曲线的偏移程度,从而能够避免SRAM的读写速度下降。SRAM的读写速度下降。SRAM的读写速度下降。

技术研发人员:张静 牛龙

受保护的技术使用者:合肥新晶集成电路有限公司

技术研发日:2022.10.26

技术公布日:2022/11/22

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。