一种led外延片、制备方法及电子设备

技术领域

1.本发明涉及半导体技术领域,特别涉及一种led外延片、制备方法及电子设备。

背景技术:

2.led(light emitting diode,发光二极管) 是一种利用载流子复合时释放能量形成发光的半导体器件,具有节能、环保、寿命长等优点,被广泛应用在日常生活中,如普通照明、城市景观照明、交通指示灯、手机、显示屏、汽车用灯等。

3.现有的led结构中外延结构至关重要,其中外延结构主要包括:基片、依次生长在衬底上的缓冲层、三维生长层、二维生长层、gan层、n型半导体层、量子阱层、电子阻挡层、p型半导体层,其中,多量子阱层由ingan量子阱层和gan量子垒层交替层叠组成,在电流作用下,p型半导体层中空穴和n型半导体层中电子经过迁移在量子阱层中进行复合,从而发出相对应的光。

4.当前的gan基led外延结构主要难点是,由于电子的有效质量相对较小,且迁移速率远大于空穴的迁移速率,此外由于量子阱层中的最后一层垒层与电子阻挡层的晶格常数差异,使得量子阱层与电子阻挡层之间存在极化效应,导致电子阻挡层的能带降低,削弱了其阻挡电子进入p型半导体的能力,从而导致电子与空穴在p型半导体层发生无效的非辐射复合,使得led的发光效率下降。尤其是在通入大电流的情况下,因极化效应导致电子阻挡层的阻挡电子能力下降会使得led会出现电子溢流,电子会穿过量子阱层和电子阻挡层进入p型半导体层,从而与空穴在p型半导体层发生非辐射复合,导致led的发光效率下降。

技术实现要素:

5.针对现有技术的不足,本发明的目的在于提供一种led外延片、制备方法及电子设备,旨在解决现有技术中的技术问题。

6.本发明提出一种led外延片,包括多量子阱层,所述多量子阱层包括交替堆叠的量子阱层及量子垒层,其中,所述量子垒层包括交替排布的第一子层和第二子层,所述第一子层为gan层,所述第二子层为含er组分的量子垒子层。

7.进一步的,所述多量子阱层包括a个第一周期结构,所述第一周期结构由所述量子阱层及所述量子垒层交替堆叠形成,所述a的取值范围为:1≤a≤13。

8.进一步的,所述量子垒层由b层所述第一子层和c层所述第二子层相互层叠组成,其中,b和c的取值范围为:1≤b≤c≤8。

9.进一步的,所述第二子层为er

x

alyinzga

1-x-y-z

n,其中,0.1<x<0.5、 0.1<y<0.9、 0≤z<0.3、x y z≤1、 x<y。

10.进一步的,所述led外延片还包括:基片,在所述基片上依次沉积有缓冲层、n型gan层、所述多量子阱层、电子阻挡层以及p型gan层。

11.与现有技术相比,本发明的有益效果在于:通过将现有的量子垒层转变成交替排布的gan层和含er组分的量子垒子层,并在量子垒中加入er组分, 以使量子垒层中形成

gan/含er组分的量子垒子层的超晶格结构,从而提高多量子阱层中对电子的势垒高度,减少了电子的泄漏;并且含er组分的量子垒子层和所述gan层可实现面内晶格常数匹配和无应变材料生长,从而降低器件有源区位错密度,减小位错散射和漏电通道, 使得外延结构具有更优越的性能及可靠性。

12.本发明还提供了一种led外延片的制备方法,用于制备上述的led外延片,所述led外延片的制备方法包括以下步骤:在沉积多量子阱层的步骤中,交替沉积量子阱层和量子垒层,以形成所述多量子阱层,其中,通过交替沉积gan层及含er组分的量子垒子层,以形成所述量子垒层。

13.进一步的,还包括以下步骤:提供一基片,并在所述基片上沉积缓冲层;在所述缓冲层上沉积n型gan层;在所述n型gan层上沉积所述多量子阱层;在所述多量子阱层上沉积电子阻挡层;在所述电子阻挡层上沉积p型gan层。

14.进一步的,利用mocvd设备沉积所述多量子阱层,其中,所述mocvd设备的设备参数为:控制所述基片的温度在第一温度范围,控制所述mocvd设备的腔体压力为第一压力范围、并控制所述mocvd设备中承载所述基片的载具转速在第一转速范围,通入第一流量范围的nh3作为氮源,通入第二流量范围的tega作为镓源,通入第三流量范围的tmin作为铟源,通入第四流量范围的triper作为铒源,通入第五流量范围的tmal作为铝源。

15.进一步的,所述第一温度范围为750-950℃,所述第一压力范围为150-250 torr,所述第一转速范围为400-600转/min,所述第一流量范围为50-200 slm,所述第二流量范围为300-600 sccm,所述第三流量范围为600-2400sccm,所述第四流量范围为300-1300sccm,所述第五流量范围为100-1000sccm,所述量子垒层的单层厚度为3-10 nm。

16.本发明还提供了一种电子设备,包括上述的led外延片。

附图说明

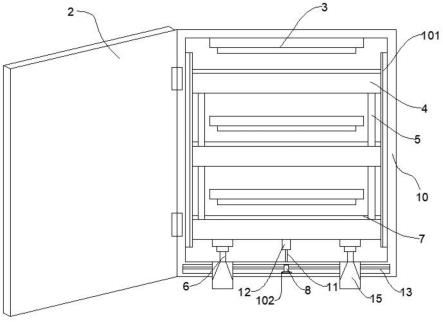

17.图1为本发明第一实施例中的led外延片的结构示意图;图2为本发明第二实施例中的量子垒层的结构示意图;图3为本发明第二实施例中led外延片的制备方法的流程框图;主要元件符号说明:1-基板;2-缓冲层;3

‑ꢀ

n型gan层;4-多量子阱层、41-量子阱层、42-量子垒层、421-第一子层、422-第二子层;5-电子阻挡层;6

‑ꢀ

p型gan层;如下具体实施方式将结合上述附图进一步说明本发明。

具体实施方式

18.为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的若干实施例。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本发明的公开内容更加透彻全面。

19.需要说明的是,当元件被称为“固设于”另一个元件,它可以直接在另一个元件上或者也可以存在居中的元件。当一个元件被认为是“连接”另一个元件,它可以是直接连接到另一个元件或者可能同时存在居中元件。本文所使用的术语“垂直的”、“水平的”、“左”、“右”以及类似的表述只是为了说明的目的。

20.除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本发明。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

21.请参阅图1,本发明第一实施例中的led外延片,晶圆的制备包括所述基片1的制备和外延工艺两大环节。

22.所述基片1是由半导体单晶材料制造而成的晶圆片,所述基片1可以直接进入晶圆制造环节生产半导体器件,也可以进行外延工艺加工生产形成外延结构。外延(epitaxy)是指在经过切、磨、抛等仔细加工的所述基片1上生长一层新单晶的过程,新单晶可以与所述基片1为同一材料,也可以是不同材料(即同质外延或者是异质外延)。由于新单晶按基片1晶相延伸生长,从而被称之为外延结构。器件制作在外延结构上为正外延,若器件制作在所述基片1上则称为反外延。

23.本实施例中,所述led外延片包括基片1,在所述基片1上依次沉积有缓冲层2、n型gan层3、多量子阱层4、电子阻挡层5以及p型gan层6,优选地,采用金属有机化学气相沉积(mocvd)设备生长所述led外延片。

24.所述多量子阱层4包括交替堆叠的量子阱层41及量子垒层42,所述量子垒层42包括交替排布的第一子层421和第二子层422,优选的,所述第一子层421为gan层,所述第二子层422为含er组分的量子垒子层。因电子的有效质量比空穴小,在大电流工作条件下,led会出现电子溢流,电子会快速越过多量子阱层4达到电子阻挡层5和p型gan层6,出现非辐射复合,传统的多量子阱层4中,gan量子垒层由于禁带宽度较小,势垒高度不够,不可避免的会出现电子溢流的现象,通过生长algan量子垒层,可提高禁带宽度和势垒高度,且al的组分越高,势垒高度越高,防止了电子溢流现象,但是高al组分的algan层和gan层之间晶格失配严重,由于晶格失配导致其界面压张应力增大,导致其界面粗糙,位错密度也相应较多,并且随着界面压张应力增大,进而会导致algan势垒高度下降,影响到对电子的阻挡。通过采用所述含er组分的量子垒子层替换传统的algan层,可实现异质结界面上的晶格匹配,晶格匹配其界面应力基本为0,界面表面平滑,位错密度相对较小,并且避免了所述含er组分的量子垒子层的势垒高度下降,确保了对电子的阻挡能力。其次,所述含er组分的量子垒子层的禁带宽度相较algan层,其厚度即使很薄也能够有足够高的势垒高度阻挡电子,将所述含er组分的量子垒子层采用与algan层相同的膜厚设计,将获得更强的阻挡电子的能力。

25.通过将现有的gan量子垒层转变成周期性依次层叠的所述gan层和所述含er组分的量子垒子层,采用gan/含er组分的量子垒子层的超晶格结构,提高了所述多量子阱层4中

对电子的势垒高度,减少了电子的泄漏。所述含er组分的量子垒子层和所述gan层依次层叠,可实现面内晶格常数匹配和无应变材料生长,从而降低器件有源区位错密度,减小位错散射和漏电通道,提升器件的性能及可靠性。

26.进一步的,所述多量子阱层4包括a个第一周期结构,所述第一周期结构由所述量子阱层41及所述量子垒层42交替堆叠形成,所述a的取值范围为:1≤a≤13。可以理解的,a为正整数,a代表所述量子阱层41和所述含er组分的量子垒子层的交替沉积的周期个数,a越大,代表着越多的电子和空穴被束缚在量子阱层41,进而使led的发光效率越高。

27.如图2所示,所述含er组分的量子垒子层包括交替排布的第一子层421和第二子层422,在本实施例中,所述量子垒层42由b层所述第一子层421和c层所述第二子层422相互层叠组成,b和c的取值范围为:1≤b≤c≤8。通过将不同材料但晶格匹配的所述gan层和所述含er组分的量子垒子层进行交替沉积,相对薄的所述含er组分的量子垒子层和相对厚的所述gan层交替生长后,既可保证对电子良好的阻挡能力,又可在控制所述多量子阱层4的厚度的情况下,提高势垒高度,所述量子垒层42的单层厚度为3-10 nm,避免所述多量子阱层4的厚度太厚,影响到异质结外延成长的界面应力,可以理解地,b和c均为正整数。

28.具体的,所述第二子层422为er

x

alyinzga

1-x-y-z

n,在所述第二子层422中,er的组分为x,al的组分为y,in的组分为z,ga的组分为

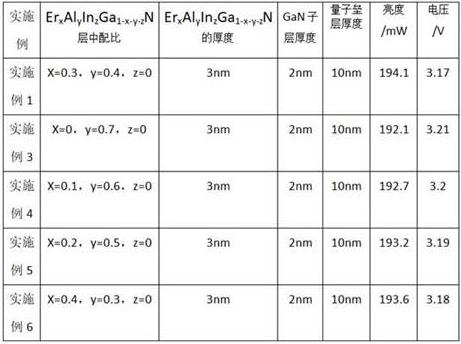

1-x-y-z

,在本实施例中,0.1<x<0.5、 0.1<y<0.9、 0≤z<0.3、x y z≤1、 x<y,优选的,er的组分为0.3,al的组分为0.4,in的组分为0,ga的组分为0.3。根据所述er

x

alyinzga

1-x-y-z

n层中er的组分不同,其与所述gan层之间的晶格匹配度也会随之变化,通过将所述er的组分控制在取值范围内,可使所述er

x

alyinzga

1-x-y-z

n层与所述gan层之间的界面压张应力减小,其中,当x为0.3时,所述er

x

alyinzga

1-x-y-z

n层与所述gan层之间没有界面压张应力。

29.综上,本发明上述实施例中的led外延片,通过将现有的量子垒层转变成交替排布的gan层和含er组分的量子垒子层,并在量子垒中加入er组分, 以使量子垒层中形成gan/含er组分的量子垒子层的超晶格结构,从而提高多量子阱层中对电子的势垒高度,减少了电子的泄漏;并且含er组分的量子垒子层和所述gan层可实现面内晶格常数匹配和无应变材料生长,从而降低器件有源区位错密度,减小位错散射和漏电通道, 使得外延结构具有更优越的性能及可靠性。

30.请参阅图2,本发明第二实施例提供了一种led外延片的制备方法,用于制备上述技术方案中所述的led外延片,采用金属有机化学气相沉积(mocvd)设备生长所述led外延片,其中采用高纯氨气(nh3)作为n(氮)源,三乙基镓(tega)作为ga(镓)源,三甲基铟(tmin)为in(铟)源,三甲基铝(tmal)作为al(铝)源,采用高纯h2(氢气)或n2(氮气)或高纯h2(氢气)和n2(氮气)的混合气作为载气,具体地,包括以下步骤:s101,提供一基片,并在所述基片上沉积缓冲层;在具体实施时,基片可选择为蓝宝石基片、硅基片、氮化镓基片以及复合式衬底等。在蓝宝石基片上沉积缓冲层,可根据相应基底选择不同的缓冲层,缓冲层材料一般为gan,aln/gan或者algan材料,本实施例中选用在蓝宝石基底上沉积aln /gan缓冲层,先在基底上沉积13~30nm的aln缓冲层,工艺流程:向pvd腔体内通入氮气60~180sccm,氩气30~60sccm,氧气1.3~5sccm,采用dc脉冲电源,功率设定3000~6000w,从而得到aln缓冲层。随后在mocvd腔体内沉积gan缓冲层,工艺流程:1、将反应室的温度控制为700~950℃,压力控制

为100~200torr,石墨基座转速控制为800~900转/min,通入流量为30~120slm的nh3作为n(氮)源,通入流量为20~200sccm的tmga作为ga(镓)源,生长厚度为5~40nm的gan。

31.进一步的,将反应室温度升高至1000~1200 ℃,压力控制为100~450torr,石墨基座转速控制为400~1000转/min,通入流量为100~180slm的nh3作为n(氮)源,通入流量为1200~1800sccm的tmga作为ga(镓)源,使得生长出1um~1.5um gan缓冲层。

32.s102,在所述缓冲层上沉积n型gan层;在具体实施时,在所述过渡层上沉积n型gan层;具体的,在制备n型半导体层的步骤中,将反应室温度降低至1090~1120℃,压力控制为100~500torr,石墨基座转速控制为500~1200转/min,通入流量为120~160slm的nh3作为n(氮)源,通入流量为1000~1500sccm的tmga作为ga(镓)源,通入sih4作为n型掺杂gan层的n型掺杂剂,同时si(硅)的掺杂浓度为2

×e18 atoms/cm

3-5

×e19

atoms/cm3,使得生长出掺si的n型掺杂gan层,并控制所沉积的n型掺杂gan层厚度为1~3um。其中该n型掺杂gan层是作为提供电子的主要外延层,在生长gan时通入sih4以提供si元素,其中si为四价元素,而gan中ga为三价元素,此时si原子替换ga原子时会提供电子,从而形成提供电子的n型掺杂gan层。

33.s103,在所述n型gan层上沉积所述多量子阱层;进一步的,在本发明实施例中,有源层由a个周期性交替排布的量子阱层和量子垒层交替堆叠组成,具体的,在n型半导体层上先堆叠一层量子阱层,量子垒层再排布在量子阱层上,然后周期性交替堆叠量子阱层和量子垒层,最终组合成多量子阱层。其中,在本实施例中,量子阱层和量子垒层交替排布的周期a取值范围为:1≤a≤13;进一步的,量子阱层为ingan层,量子垒层为gan/er

x

alyinzga

1-x-y-z

n层两子层层叠组成。量子阱层的厚度为1.8~6 nm,量子垒层的厚度为3~10 nm(gan层1~5nm/er

x

alyinzga

1-x-y-z

n层1~5nm)。在一个周期中,量子阱层和量子垒层的沉积总厚度为6.5nm~20nm。

34.具体的,在沉积量子阱层时,其反应室生长温度为760℃~820 ℃,压力为150~250 torr,石墨基座转速为400~600转/min,通入流量为120~200 slm的nh3作为n(氮)源,通入流量为200~250sccm的tega作为ga(镓)源,通入流量为1800~2400 sccm的tmin作为in(铟)源,并控制所沉积的ingan量子阱层厚度为1.6~8nm。

35.具体的,在沉积量子垒第一子层gan层时,其反应室温度为850~950 ℃,压力为150~250 torr,放置基片的石墨基座转速为400~700转/min,通入流量为150~200slm的nh3作为n(氮)源,通入流量为800~1000sccm的tega作为ga(镓)源,所沉积第一子层gan层厚度为1nm~5nm。

36.在沉积量子垒第二子层er

x

alyinzga

1-x-y-z

n层时,其反应室温度为850~950 ℃,压力控制为150~250torr,石墨基座转速控制为400~600转/min,通入流量为120~160slm的nh3作为n(氮)源,通入流量为300~600sccm的tmga作为ga(镓)源,ga(镓)源流量由高到低逐渐变化,通入流量为100~1000sccm的tmal作为al(铝)源,al(铝)源流量由低到高逐渐变化,通入流量为600~2400 sccm的tmin作为in(铟)源,in(铟)源由高逐渐变低,通入流量为100-600sccm的triper作为er(铒)源, er(铒)源流量由低到高逐渐变化,并控制所沉积的er

x

alyinzga

1-x-y-z

n层厚度为1~5nm。

37.该er

x

alyinzga

1-x-y-z

n层带隙比gan大,置于gan子层之上,电子移动至eraalbga

1-a-b

n层需要跨过更高的势垒高度,进而能有效限制电子移动,减少电子溢流,提高电子空穴在有

源层复合发光效率。此外,通过调节eralgan层的组分由er

0.1

al

0.4

ga

0.5

n到er

0.2

al

0.7

ga

0.1

n,可以实现势垒的渐变和与gan晶格常数的匹配,可以具有更好的晶体质量,从而降低有源层的位错密度,减少非辐射复合中心和漏电通道,使led器件具有更优越的性能及可靠性。

38.s104,在所述多量子阱层上沉积电子阻挡层;在具体实施时,在多量子阱层上沉积电子阻挡层,将反应室温度控制为850~1000℃,压力控制为100~300torr,放置基片的石墨盘转速控制为800~1000转/min,通入流量为80~160slm的nh3做为n(氮)源,流量为600~1200sccm的tega作为ga(镓)源,流量为10~120sccm的tmal作为al(铝)源,沉积algan电子阻挡层,其电子阻挡层厚度为20nm~100nm。

39.s105,在所述电子阻挡层上沉积p型gan层。

40.在具体实施时,p型gan层包括低温p型gan层、高温p型gan层和p型gan接触层。其中低温p型gan层在低温条件下生长,高温p型gan层在高温条件下生长,p型gan接触层为重掺mg。

41.1、将反应室温度控制为700~800 ℃,压力控制为100~300torr,放置基片的石墨盘转速控制为1000~1200 转/min,通入流量为80~160slm的nh3做为n(氮)源,流量为800~1600sccm的tega作为ga(镓)源,通入二茂镁(cp2mg)作为p型掺杂剂,mg(镁)的掺杂浓度为5

×e19

atoms/cm3~2

×e20

atoms/cm3,沉积低温p型gan层,其厚度为6 nm~30nm。cp2mg提供mg(镁)元素,mg原子替换ga原子时产生空穴,形成p型gan层,通过适量浓度的mg掺杂能够对gan中的缺陷空位进行填充修复位错,阻断位错的进一步延伸。

42.2、将反应室温度控制为900~1100℃,压力控制为100~500torr,放置基片的石墨盘转速控制为800~1000转/min,通入流量为80~160slm的nh3做为n(氮)源,流量为700~1100sccm的tega作为ga(镓)源,通入二茂镁(cp2mg)作为p型掺杂剂,mg(镁)的掺杂浓度为3

×e18 atoms/cm3~2

×e19 atoms/cm3,沉积掺mg高温p型gan层,其厚度为20nm~160 nm。

43.3、将反应室温度控制为700~1000℃,压力控制为100~500torr,放置基片的石墨盘转速控制为800~1000转/min,通入流量为80~160slm的nh3做为n(氮)源,流量为360~600sccm的tega作为ga(镓)源,通入二茂镁(cp2mg)作为p型掺杂剂,同时mg(镁)的掺杂浓度为2

×e20

atoms/cm3~1

×e22

atoms/cm3,沉积重掺mg的gan层作为p型接触层,其厚度为1nm~10nm。

44.本发明第三实施例提供了一种led外延片,本实施例中的led外延片与第一实施例中的led外延片的不同之处在于:er

x

alyinzga

1-x-y-z

n层中,er的组分x为0,al的组分y为0.7,in的组分为0,ga的组分为0.3。

45.本发明第四实施例提供了一种led外延片,本实施例中的led外延片与第一实施例中的led外延片的不同之处在于:er

x

alyinzga

1-x-y-z

n层中,er的组分x为0.1,al的组分y为0.6,in的组分为0,ga的组分为0.3。

46.本发明第五实施例提供了一种led外延片,本实施例中的led外延片与第一实施例中的led外延片的不同之处在于:er

x

alyinzga

1-x-y-z

n层中,er的组分x为0.2,al的组分y为0.5,in的组分为0,ga的组分为0.2。

47.本发明第六实施例提供了一种led外延片,本实施例中的led外延片与第一实施例中的led外延片的不同之处在于:er

x

alyinzga

1-x-y-z

n层中,er的组分x为0.4,al的组分y为0.3,in的组分为0,ga的组分为0.3。

48.请参阅下表:由上表可以看出,er组分低,压电极化效应显著,影响发光效率,垒层层势较低,电子较容易跃迁,导致电压下降,漏电严重,er组分过高导致位错密度增加,漏电通道增加,亮度衰减。

49.综上,本发明实施例当中的led外延片的制备方法,通过将现有的量子垒层转变成交替排布的gan层和含er组分的量子垒子层,并在量子垒中加入er组分, 以使量子垒层中形成gan/含er组分的量子垒子层的超晶格结构,从而提高多量子阱层中对电子的势垒高度,减少了电子的泄漏;并且含er组分的量子垒子层和所述gan层可实现面内晶格常数匹配和无应变材料生长,从而降低器件有源区位错密度,减小位错散射和漏电通道, 使得外延结构具有更优越的性能及可靠性。

50.本发明第七实施例提供了一种电子设备,包含上述技术方案中所述的led外延片。

51.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

52.以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对本发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。