1.本发明涉及半导体技术领域,特别涉及一种实现卷积神经网络的单片光子集成芯片。

背景技术:

2.目前,卷积神经网络cnn已经广泛应用于图像识别、目标检测和语义分割等各种领域,卷积神经网络是通过神经元的线性和非线性运算将输入映射到输出,是一类包含卷积计算且具有深度结构的前馈神经网络(feedforward neural networks),是深度学习(deep learning)的代表算法之一。卷积神经网络是一种重要的神经网络结构,在图像这种二维数据的处理具有很重要的作用。

3.其中,卷积神经网络的结构通常为包含卷积层、池化层、以及非线性激活层和全连接层。卷积运算的基本原理是采用一个卷积核矩阵与输入矩阵的子矩阵对应元素相乘并相加,这种卷积运算能够有效提取图像的特征。在卷积层进行特征提取后,输出的特征图会被传递至池化层进行特征选择和信息过滤。池化层包含预设定的池化函数,其功能是将特征图中单个点的结果替换为其相邻区域的特征图统计量。将卷积层或者池化层的输出展开为一维的向量之后作为全连接层的输入,该层往往实现分类的功能。卷积神经网络中的全连接层等价于传统前馈神经网络中的隐含层。全连接层位于卷积神经网络隐含层的最后部分,并只向其它全连接层传递信号。卷积神经网络中输出层的上游通常是全连接层,输出层直接输出分类结果。

4.相关技术中,在实现卷积神经网络时,通常是采用电子卷积神经网络的方案,电子卷积神经网络是基于电子元器件来实现的,如通过电阻、二极管和导线等构建卷积神经网络。而该方案存在延迟大和功耗高的问题,高延迟是由于大规模的密集互联密度导致的高rc延迟,高功耗是由于整个电路中的金属电阻会产生极大的能耗。且在基于电子器件的卷积神经网络中绝大多数的能量都是在线性运算中产生的。而线性运算在卷积神经网络运算中占有极大比例。

5.为改善这一状况,近年来,相关技术中还提出了光电混合的方案。比如,相关技术中还提出利用时间拉伸实现光电卷积神经网络。该方案通过使用几十公里的色散光纤通过时间拉伸效应将锁模激光器产生的脉冲光的不同频率分量在时域上展开,利用waveshaper将频率分量削平,以及利用反常色散光纤将包含输入和权重相乘之后的信息的频率分量重新压缩成脉冲信号,从而实现相加的过程。然而,该方案的池化层和非线性激活层仍是在电域上实现的,且使用了几十公里的色散光纤来实现时间拉伸效应,功耗仍然较高且不具备可扩展性,只能应用于少量、单一的卷积神经网络。

6.因此,如何提供一种高集成度、低功耗和可扩展的卷积神经网络实现方案,成为目前亟需解决的问题。

技术实现要素:

7.本发明旨在至少在一定程度上解决相关技术中的技术问题之一。

8.为此,本发明的目的在于提出一种实现卷积神经网络的单片光子集成芯片,使用全光方案完成输入层、卷积层、池化层、非线性激活层和全连接输出层的单片芯片集成,从而在单片光子集成芯片上实现了光卷积神经网络。该芯片集成度高、功耗低且具有可扩展性,可以便捷的实现多个隐藏层,能够适用于各种复杂的卷积网络。

9.为达到上述目的,本发明实施例提出了一种实现卷积神经网络的单片光子集成芯片,包括:输入层、卷积池化层和输出全连接层,其中,

10.所述输入层包括:半导体环形锁模激光器、第一半导体光放大器、1

×

n阵列波导光栅和第一组幅度调制器,所述卷积池化层包括:所述1

×

n阵列波导光栅、所述第一组幅度调制器、第二组幅度调制器、n

×

1阵列波导光栅和放大非线性区域,所述放大非线性区域包括:1

×

2多模干涉耦合器、第一激光器、第二半导体光放大器、第一相位调制器、第二激光器、第三半导体光放大器、第二相位调制器和2

×

1多模干涉耦合器,所述输出全连接层包括:1

×

k多模干涉耦合器、第三组幅度调制器和光电探测器组,n和k为正整数,其中,

11.所述半导体环形锁模激光器的输出端与所述第一半导体光放大器的输入端相连,用于产生光频梳信号;所述第一半导体光放大器的输出端与所述1

×

n阵列波导光栅的输入端相连,用于向所述光频梳信号提供增益;

12.所述1

×

n阵列波导光栅的每个输出端与所述第一组幅度调制器对应的输入端相连,用于进行波分解复用,将放大后的光频梳信号分解成n路信号分别输出至不同的输出端;

13.所述第一组幅度调制器的每个输出端与所述第二组幅度调制器对应的输入端相连,在输入层中用于将待分类的图像信号加载至分解后的每路光频梳信号的光脉冲上;

14.所述第二组幅度调制器的每个输出端与所述n

×

1阵列波导光栅的输入端相连,在卷积层中用于实现卷积运算中输入信号值与权重值的相乘运算;

15.所述n

×

1阵列波导光栅的输出端与所述1

×

2多模干涉耦合器的输入端相连,在卷积层中用于进行波分复用,将n路进行所述相乘运算后的光信号合为1路光信号,以实现相加运算;

16.所述1

×

2多模干涉耦合器的输出端分别与所述第二半导体光放大器和所述第三半导体光放大器的输入端相连,用于将所述相加运算得到的1路光信号分解为相同的两路光信号;

17.所述第一激光器与所述第二半导体光放大器的输入端相连,所述第二激光器与所述第三半导体光放大器的输入端相连,所述第二半导体光放大器的输出端与所述第一相位调制器的输入端相连,所述第三半导体光放大器的输出端与所述第二相位调制器的输入端相连,所述第二半导体光放大器和所述第三半导体光放大器在卷积层中用于放大所述两路光信号的幅度;

18.所述第一相位调制器和所述第二相位调制器的输出端与所述2

×

1多模干涉耦合器的输入端相连,所述2

×

1多模干涉耦合器的输出端与所述1

×

k多模干涉耦合器的输入端相连,所述2

×

1多模干涉耦合器用于将放大后的两路光信号合并为1路光信号作为卷积层输出的光信号;

19.所述卷积层输出的光信号通过外部控制系统反馈至池化层的所述第一组幅度调制器处,所述第一组幅度调制器在池化层中还用于将上一卷积层输出的光信号加载至所述分解后的每路光频梳信号的光脉冲上;

20.所述第二组幅度调制器在池化层中还用于进行特征选择和信息过滤;所述第二半导体光放大器和所述第三半导体光放大器,在池化层中还用于实现非线性激活sigmoid函数功能,以进行线性计算;所述第一相位调制器和所述第二相位调制器在池化层中用于差分增益调制中的相位控制;

21.所述1

×

k多模干涉耦合器的每个输出端与所述第三组幅度调制器对应的输入端相连,用于将池化层输出的计算完成的光信号通过分解成k路功率相等的光信号分别输出至不同的输出端;

22.所述第三组幅度调制器的每个输出端与所述光电探测器组对应的输入端相连,用于对k路光信号分别进行调制;

23.每个所述光电探测器用于根据调制后的光信号产生并输出电信号,所述光电探测器组输出的全部电信号中,功率值最大的电信号对应的通道为所述卷积神经网络识别的分类结果;

24.所述输入层、所述卷积池化层和所述输出全连接层包含的全部元器件通过光波导结构相连,并集成设置在所述iii-v族化合物半导体材料基底上。

25.另外,根据本发明上述实施例的实现卷积神经网络的单片光子集成芯片,还可以具有以下附加的技术特征:

26.可选地,在本发明的一个实施例中,所述1

×

n阵列波导光栅,具体用于:根据卷积神经网络的计算需求,从所述光频梳信号的不同频率分量中提取出预设数量的单一频率分量。

27.可选地,在本发明的一个实施例中,所述第二组幅度调制器中的每个幅度调制器在卷积层中的调制信号分别为不同的卷积核内的权重值,所述第二组幅度调制器在卷积层中具体用于:将权重信号加载在搭载了所述待分类的图像信号的每路光频梳信号的光脉冲上。

28.可选地,在本发明的一个实施例中,所述第二组幅度调制器中的每个幅度调制器在池化层中的调制信号相同,所述第二组幅度调制器在池化层中具体用于:将所述待分类的图像信号的特征图中的任一点的特征替换为所述任一点的相邻区域的特征图统计量,以进行所述特征选择和所述信息过滤。

29.可选地,在本发明的一个实施例中,所述第二半导体光放大器和所述第三半导体光放大器在池化层中具体用于:通过控制对应的激光器的输入光功率值使所述第二半导体光放大器和所述第三半导体光放大器工作在不同的饱和状态;基于所述第二半导体光放大器和所述第三半导体光放大器之间的差分增益,将输入的不同峰值功率的光信号对应映射在0至1的闭区间内,其中,0表示低电平,1表示高电平。

30.可选地,在本发明的一个实施例中,所述池化层输出的光信号通过所述外部控制系统反馈至下一层的卷积层的所述第一组幅度调制器处进行幅度调制,并根据所述卷积神经网络的计算需求进行目标数量次卷积计算、池化计算和非线性计算直至计算完成。

31.可选地,在本发明的一个实施例中,iii-v族化合物半导体材料包括但不限于:

inp、gaas、alas、ingaasp、ingaalas和ingaas中的任一种。

32.本发明的实施例提供的技术方案至少带来以下有益效果:

33.(1)本发明采用iii-v化合物半导体材料作为芯片基底,通过半导体激光器、半导体光放大器、半导体调制器、阵列波导光栅、半导体耦合器、半导体光电探测器与无源波导结构等器件的单片集成,实现了将卷积神经网络的每一层均在单片光子集成芯片上集成,提高了实现卷积神经网络的芯片的集成度。

34.(2)本发明采用全光方案,降低了光-电-光转换带来的功率损耗和信号传输过程中的损耗,从而降低了芯片的功耗,有利于实现大规模卷积神经网络的计算。

35.(3)本发明的单片光子集成芯片具有可扩展性,可以便捷的实现多个隐藏层,能够适用于各种复杂的卷积神经网络。

36.(4)本发明使用环形锁模激光器产生光频梳作为光卷积神经网络的光源,进一步提高了集成度高并降低了功耗,且基于光频梳的特性,便于实现卷积网络中的相乘和相加运算。

37.(5)本发明中的单片光子集成芯片在毫米或厘米量级,缩小了实现卷积神经网络的芯片的尺寸,降低了制造成本。

38.本发明附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解。

附图说明

39.本发明上述的和/或附加的方面和优点从下面结合附图对实施例的描述中将变得明显和容易理解,其中:

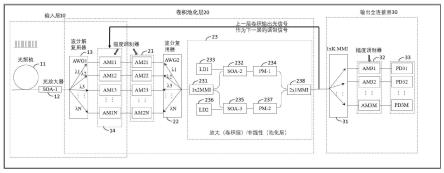

40.图1为根据本发明一个实施例的实现卷积神经网络的单片光子集成芯片的结构示意图。

41.附图标记:输入层-10;卷积池化层-20;输出全连接层-30;半导体环形锁模激光器-11;第一半导体光放大器-12;1

×

n阵列波导光栅-13;第一组幅度调制器-14;第二组幅度调制器-21;n

×

1阵列波导光栅-22;放大非线性区域-23;1

×

2多模干涉耦合器-231;第二半导体光放大器-232;第一激光器-233;第一相位调制器-234;第三半导体光放大器-235;第二激光器-236;第二相位调制器-237;2

×

1多模干涉耦合器-238;1

×

k多模干涉耦合器-31、第三组幅度调制器-32和光电探测器组33。

具体实施方式

42.下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,旨在用于解释本发明,而不能理解为对本发明的限制。

43.需要说明的是,在本发明一个实施例中,申请人发现,相比于电子器件,光子器件由于具高带宽和低功耗的优势,更加适合于实现卷积神经网络,用于线性互联。光互联功耗极低,光纤传输的损耗可达到《0.1db/km,iii-v族化合物光波导传输损耗可达《2db/cm,硅波导甚至可以达到《1db/cm,而芯片尺寸基本在毫米或厘米量级,因此光子卷积神经网络的损耗比电子卷积神经网络大大的降低了。除此之外,基于光子器件构建的光卷积神经网络

的带宽可以达到10thz量级,远高于电子卷积神经网络的khz-mhz量级。

44.基于此,本发明提出了一种实现卷积神经网络的单片光子集成芯片,实现了光卷积神经网络的单片芯片集成,该芯片集成度高、功耗低且具有可扩展性。

45.下面参照附图描述根据本发明实施例提出的实现卷积神经网络的单片光子集成芯片。

46.图1为根据本发明一个实施例的实现卷积神经网络的单片光子集成芯片的结构示意图。

47.如图1所示,该实现卷积神经网络的单片光子集成芯片包括:输入层10、卷积池化层20、输出全连接层30。

48.其中,输入层10、卷积池化层20和输出全连接层30包含的全部元器件集成设置在iii-v族化合物半导体材料基底40上,在光子集成芯片上实现光卷积神经网络。图1所示的黑色实体框线内部为完整单片光子集成芯片,图1为该单片光子集成芯片的俯视图,该芯片整体从左到右可分为输入层10、卷积池化层20和输出全连接层30三个部分,其中输入层10和卷积池化层20部分重合,即运算过程中这两个层的部分器件可重复使用。

49.其中,输入层10从左到右包括:半导体环形锁模激光器11、第一半导体光放大器12、1

×

n阵列波导光栅13和第一组幅度调制器14。

50.半导体环形锁模激光器(ring laser)11的输出端与第一半导体光放大器12的输入端相连,用于产生光频梳信号。具体的,半导体环形锁模激光器11用于产生光脉冲信号,该光脉冲信号在频域上是一系列等频间隔、位置固定且具有极宽光谱范围的单色谱线(纵模),即光频梳信号。

51.第一半导体光放大器(semiconductor optical amplifier,简称soa)12的输出端与1

×

n阵列波导光栅13的输入端相连,用于向光频梳信号提供增益。具体的,光放大器用于给脉冲提供增益,在本技术一个实施例中,第一半导体光放大器12可以对光频梳信号的光功率进行放大,以满足卷积网络运算对光频梳信号的功率需求。

[0052]1×

n阵列波导光栅13的每个输出端与第一组幅度调制器14对应的输入端相连,用于进行波分解复用,将放大后的光频梳信号分解成n路信号分别输出至不同的输出端。具体的,1

×

n阵列波导光栅13具有1路输入和n路输出,可近似视作波分解复用器。其中,n为正整数,具体的数值大小可以根据实际卷积运算需要进行设置。

[0053]

在本发明一个实施例中,1

×

n阵列波导光栅13将光频梳信号中的不同频率分量按照卷积神经网络的计算需求提取出预设数量的单一频率分量,并分成n路分别输出到不同的通道中,预设数量根据计算所需预先确定。

[0054]

第一组幅度调制器14的每个输出端与第二组幅度调制器21对应的输入端相连,在输入层中用于将待分类的图像信号加载至分解后的每路光频梳信号的光脉冲上。在本发明一个实施例中,当本技术的单片光子集成芯片用于进行图像分类时,第一组幅度调制器14将外部输入的待分类的图像信号加载到光频梳信号上,以光频梳信号为载体,便于后续进行卷积运算中的相乘和相加计算。第一组幅度调制器14包含的调制器(am)的数量为n,每个调制器(am)的输入端与1

×

n阵列波导光栅13对应的输出端连接。

[0055]

卷积池化层20从左到右包括:上述的1

×

n阵列波导光栅13和第一组幅度调制器14,以及第二组幅度调制器21、n

×

1阵列波导光栅22和放大非线性区域23,其中,放大非线

性区域23包括:1

×

2多模干涉耦合器(multiple-mode interference,简称mmi)231、第二半导体光放大器232、第一激光器(laser diode,简称ld)233、第一相位调制器(pm)234、第三半导体光放大器235、第二激光器236、第二相位调制器237和2

×

1多模干涉耦合器238。其中,第二半导体光放大器232、第一激光器(laser diode,简称ld)233和第一相位调制器(pm)234为一路,视为上臂,第三半导体光放大器235、第二激光器236和第二相位调制器237为一路,视为下臂。

[0056]

具体而言,本发明的卷积池化层20既可以实现卷积神经网络中卷积层的运算,也可以实现池化层的运算,实际应用中,卷积池化层20通过控制其内部不同的器件工作,以实现不同层的运算。

[0057]

其中,输入层10和卷积池化层20共用的器件为1

×

n阵列波导光栅13和第一组幅度调制器14,在输入层10加载了图像信号的n路光频梳信号先由卷积层进行卷积运算,即在卷积层中输入图像信号已通过第一组幅度调制器14加载在光频梳的光脉冲上,再经过第二组幅度调制器21。

[0058]

第二组幅度调制器21的每个输出端与n

×

1阵列波导光栅22的输入端相连,在卷积层中用于实现卷积运算中输入信号值与权重值的相乘运算。具体的,第二组幅度调制器21包含的调制器的数量与第一组幅度调制器14包含的数量相同,均为n,每个调制器的输入端与第一组幅度调制器14中对应的调制器的输出端连接。

[0059]

在本发明一个实施例中,第二组幅度调制器21中的每个幅度调制器在卷积层中的调制信号分别为不同的卷积核内的权重值,第二组幅度调制器21在卷积层中具体用于将权重信号加载在搭载了待分类的图像信号的每路光频梳信号的光脉冲上,以实现了卷积运算中的输入信号值与权重值的相乘运算。

[0060]n×

1阵列波导光栅22的输出端与1

×

2多模干涉耦合器231的输入端相连,在卷积层中用于进行波分复用,将n路进行相乘运算后的光信号合为1路光信号,以实现相加运算。具体的,n

×

1阵列波导光栅22近似视作波分复用器,相乘运算后的光脉冲信号经过n

×

1的阵列波导光栅22进行波分复用,实现了n路光输入,1路光输出,从而实现了卷积运算中的相加运算。

[0061]

放大非线性区域23既可以实现放大运算也可以实现非线性运算,其中,在卷积层只有两个多模干涉耦合器mmi和上下两臂中的soa工作,用于向光路提供增益,因此在卷积层中该区域为放大区域,起到为光信号增大功率的作用,而在池化层该区域内所有的元器件均进行工作,起到非线性激活函数的作用,因此在池化层中该区域为为非线性区域。

[0062]

具体而言,该区域中的1

×

2多模干涉耦合器的231输出端分别与第二半导体光放大器232和第三半导体光放大器235的输入端相连,第一激光器233与第二半导体光放大器232的输入端相连,第二激光器236与第三半导体光放大器235的输入端相连,第二半导体光放大器232的输出端与第一相位调制器234的输入端相连,第三半导体光放大器235的输出端与第二相位调制器237的输入端相连,第一相位调制器234和第二相位调制器237的输出端与2

×

1多模干涉耦合器238的输入端相连。实际应用中,n

×

1阵列波导光栅22输出的进行了相加运算后的1路光信号进入放大区域,先经过1

×

2多模干涉耦合器231后被均分为两路相同的光信号,然后通过上下两臂的soa实现幅度放大,补偿之前光路传输的损耗,再通过2

×

1多模干涉耦合器238将放大后的两路光信号合并为1路光信号作为卷积层输出的光信

号。

[0063]

进一步的,卷积层输出的放大运算后的1路光信号通过外部控制系统反馈至下一层即池化层的第一组幅度调制器14处,进行后续的池化运算。

[0064]

具体而言,池化层为图1所示的卷积池化层20对应的虚线框内的完整结构。在池化层中,上述的1

×

n阵列波导光栅13将光频梳产生的不同频率分量按照卷积网络的需求提取出所需数量的单一频率分量,分成n路分别输出到不同的通道中。上一层即卷积层输出的光信号通过外部控制系统反馈至池化层的第一组幅度调制器14处,作为调制信号加载在从1

×

n阵列波导光栅13输出的光脉冲上,即第一组幅度调制器在池化层中还用于将上一卷积层输出的光信号加载至分解后的n路光频梳信号的光脉冲上,再经过第二组幅度调制器21进行调制。

[0065]

第二组幅度调制器14在池化层中还用于进行特征选择和信息过滤。具体实施时,在本发明一个实施例中,第二组幅度调制器14中的每个幅度调制器在池化层中的调制信号相同,第二组幅度调制器14在池化层中具体用于:将待分类的图像信号的特征图中任一点的特征替换为任一点的相邻区域的特征图统计量,以进行特征选择和信息过滤,即,将特征图中单个点的结果替换为其相邻区域的特征图统计量进行特征选择和信息过滤。

[0066]

第二组幅度调制器14输出的n路光信号经过n

×

1阵列波导光栅22进行波分复用实现了n路光输入,1路光输出后进入非线性区域。

[0067]

在非线性区域中,第二组幅度调制器14输出的1路光信号先经过1

×

2多模干涉耦合器231被均分为两路相同的光信号分别进入非线性区域的上臂和下臂,上臂中的第二半导体光放大器232和下臂中的第三半导体光放大器235,在池化层中还用于实现非线性激活sigmoid函数功能,以进行线性计算。

[0068]

具体实施时,在本发明一个实施例中,第二半导体光放大器232和第三半导体光放大器235通过控制对应的激光器的输入光功率值使各自分别工作在不同的饱和状态,以调节非线性激活sigmoid函数的阈值,即上臂的soa通过控制第一激光器ld233的输入光功率大小,下臂soa通过控制第二激光器ld236的输入光功率大小,分别工作在不同的饱和状态,从而调节非线性激活函数的阈值;基于所述第二半导体光放大器和所述第三半导体光放大器之间的差分增益,将输入的不同峰值功率的光信号对应映射在0至1的闭区间内,其中,0表示低电平,1表示高电平。

[0069]

具体而言,通过控制激光器的输入光功率值,使ld1向soa2处注入适量的连续激光输入信号,使soa2的增益接近其在透明区域的端点。同时,ld2输入的连续激光输入信号使soa3在略高于透明区域的不同增益级别上工作,因此这两个soa之间的差分增益对应于这两个soa分支之间的相移。基于这种偏置方案,使得具有较高峰值功率的输入光信号在经过此结构后输出的脉冲光功率维持在同一高电平(即逻辑上的“1”,该高电平具体功率值在不同的应用场景下取值不同)。对应的,具有较低峰值功率的输入光信号在经过此结构后输出的脉冲光功率维持在同一低电平(即逻辑上的

‘0’

,该低电平具体功率值在不同的应用场景下取值不同),而中间峰值功率的光信号被一一映射在0至1之间,使得输入的不同峰值功率光信号变量被映射0至1的闭区间内,由此实现了sigmod激活函数功能。

[0070]

第一相位调制器234和第二相位调制器237在池化层中用于差分增益调制中的相位控制。具体的,第一相位调制器234对第二半导体光放大器232输出的脉冲光信号进行相

位调制,第二相位调制器237对第三半导体光放大器235输出的脉冲光信号进行相位调制,从而实现差分增益调制中的相位控制,确保非线性函数功能的实现。

[0071]2×

1多模干涉耦合器238,在池化层中还用于将相位调制后的两路光信号合并为1路光信号作为池化层输出的光信号。

[0072]

至此,本发明的单片光子集成芯片完成了一次卷积、池化和非线性计算。在本发明一个实施例中,池化层输出的进行非线性计算后的光信号还可以通过外部控制系统反馈至下一层的卷积层的第一组幅度调制器14处进行幅度调制,进行下一次的卷积、池化和非线性计算。并且,还可以根据卷积神经网络的计算需求进行目标数量次卷积计算、池化计算和非线性计算直至计算完成。其中,目标数量根据卷积神经网络完成图像分类任务所需的计算此处确定,后续每次的卷积、池化和非线性计算过程可参照上述第一次计算的描述,实现原理相同,此处不再赘述。

[0073]

由此,上述实施例中的卷积层和池化层可视为第一层,本发明的单片光子集成芯片,通过将卷积层输出的光信号作为池化层的调制信号,并将池化层输出的光信号反馈至下一层的卷积层的第一组幅度调制器处进行幅度调制,使本芯片具有可扩展性,可以便捷的实现多个隐藏层,有利于应用于各种复杂的卷积神经网络。

[0074]

进一步的,输出全连接层30包括:1

×

k多模干涉耦合器31、第三组幅度调制器32和光电探测器(photoelectric detector,简称pd)组33,k为正整数。

[0075]

其中,1

×

k多模干涉耦合器31的输入端与2

×

1多模干涉耦合器238的输出端相连,每个输出端分别与第三组幅度调制器32对应的输入端相连,1

×

k多模干涉耦合器31用于将池化层输出的计算完成(即进行了目标数量次的卷积、池化和非线性计算)的光信号分解成k路功率相等的光信号分别输出至不同的输出端。

[0076]

第三组幅度调制器32的每个输出端与光电探测器组33对应的输入端相连,用于对k路光信号分别进行调制。具体的,第三组幅度调制器32包含k个幅度调制器,均分的k路功率相等的光信号分别进入对应的一个幅度调制器进行调制。

[0077]

光电探测器组33包含k个光电探测器,调制后的光信号进入对应的光电探测器产生电信号,光电探测器组33再将电信号输出至输出通道中。输出层的通道数量为本发明的卷积神经网络分类结果类别的数量,光电探测器组33输出的全部电信号中,功率值最大的电信号对应的通道为卷积神经网络识别的分类结果。

[0078]

需要说明的是,上述输入层10、卷积池化层20和输出全连接层30的全部元器件之间均通过光波导结构相连,并且本技术的芯片采用iii-v族化合物半导体材料作为基底,上述各个结构层中的全部元器件,单片集成设置在iii-v族化合物半导体材料基底40上。在本发明一个实施例中,iii-v族化合物半导体材料包括但不限于:inp、gaas、alas、ingaasp、ingaalas和ingaas中的任一种,基底具体的材料可以根据实际需要选择其中任一种。由此实现了光卷积神经网络的片上集成。

[0079]

综上所述,本发明实施例的实现卷积神经网络的单片光子集成芯片,采用iii-v化合物半导体材料作为芯片基底,通过半导体激光器、半导体光放大器、半导体调制器、阵列波导光栅、半导体耦合器、半导体光电探测器与无源波导结构等器件的单片集成,实现了将卷积神经网络的全部层在单片光子集成芯片上集成,提高了实现卷积神经网络的芯片的集成度和卷积神经网络的完整性。采用全光方案,降低了光-电-光转换带来的功率损耗和信

号传输过程中的损耗,从而降低了芯片的功耗,有利于实现大规模卷积神经网络的计算。使用环形锁模激光器产生光频梳作为光卷积神经网络的光源,进一步提高了集成度高并降低了功耗,且基于光频梳的特性,极易实现卷积网络中的相乘和相加运算。该单片光子集成芯片具有可扩展性,可以便捷的实现多个隐藏层,能够适用于各种复杂的卷积神经网络,且芯片在毫米或厘米量级,缩小了实现卷积神经网络的芯片的尺寸,降低了制造成本。

[0080]

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

[0081]

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。在本发明的描述中,“多个”的含义是至少两个,例如两个,三个等,除非另有明确具体的限定。

[0082]

尽管上面已经示出和描述了本发明的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本发明的限制,本领域的普通技术人员在本发明的范围内可以对上述实施例进行变化、修改、替换和变型。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。