技术特征:

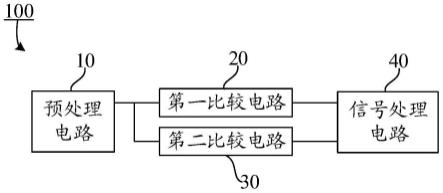

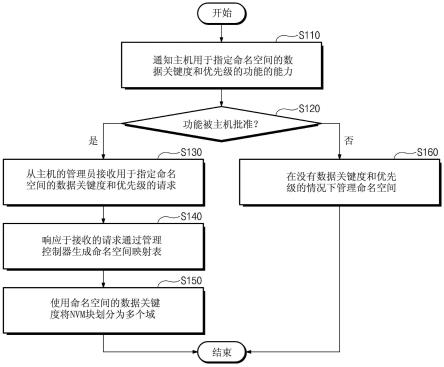

1.一种数据总线翻转电路,其特征在于,包括:预处理电路,用于接收当前数据与前一笔数据的比较结果,并对所述比较结果进行预处理,输出预处理信号,所述比较结果中包含多个子结果,每一位所述子结果用于表征对应位的所述当前数据和所述前一笔数据的比较结果;第一比较电路,用于接收所述预处理信号,并基于所述预处理信号输出第一比较信号;所述第一比较信号用于判断所述比较结果中预设值的数量是否大于等于第一值,所述预设值表征所述当前数据与所述前一笔数据的对应位数据不同;第二比较电路,用于接收所述预处理信号,并基于所述预处理信号输出所述第二比较信号;所述第二比较信号用于判断所述预设值的数量是否大于等于第二值;信号处理电路,用于接收所述第一比较信号、所述第二比较信号和所述前一笔数据对应的数据翻转信号,并输出所述当前数据的数据翻转信号。2.根据权利要求1所述的电路,其特征在于,所述数据总线翻转电路还包括:输出电路;所述输出电路用于接收所述当前数据的数据翻转信号,并基于所述当前数据的数据翻转信号确定当前数据线传输的数据。3.根据权利要求2所述的电路,其特征在于,所述第一值大于所述第二值,所述第二值等于所述数据线同一时刻传输的数据量的一半;所述第一比较信号在所述预设值的数量大于等于所述第一值时指示第二状态;所述第一比较信号在所述预设值的数量小于所述第一值时指示第一状态;所述第二比较信号在所述预设值的数量大于等于所述第二值时指示所述第一状态;所述第二比较信号在所述预设值的数量小于所述第二值时指示所述第二状态;所述信号处理电路用于在所述第二比较信号和所述第一比较信号均指示所述第一状态时,输出所述前一笔数据的数据翻转信号作为所述当前数据的数据翻转信号;所述信号处理电路用于在所述第二比较信号输出所述第一状态、且在所述第一比较信号输出所述第二状态时,输出第一数据翻转信号作为所述当前数据的数据翻转信号,其中,所述第一数据翻转信号指示所述当前数据需要翻转;所述信号处理电路用于在所述第二比较信号输出所述第二状态、且在所述第一比较信号输出所述第一状态时,输出第二数据翻转信号作为所述当前数据的数据翻转信号,其中,所述第二数据翻转信号指示所述当前数据不需要翻转。4.根据权利要求3所述的电路,其特征在于,所述比较结果包括2n个所述子结果,其中,前n个所述子结果形成第一组数据信号,后n个所述子结果形成第二组数据信号;所述预处理电路包括:第一预处理电路和第二预处理电路;所述第一预处理电路包括第一模块和第二模块;所述第一模块用于接收所述第一组数据信号,并基于所述第一组数据信号输出第一输出信号;所述第二模块用于接收所述第一输出信号,并基于所述第一输出信号输出第二输出信号;所述第二预处理电路包括第三模块和第四模块;所述第三模块用于接收所述第二组数据信号,并基于所述第二组数据信号输出第三输出信号;所述第四模块用于接收所述第三输出信号,并基于所述第三输出信号输出第四输出信号。

5.根据权利要求4所述的电路,其特征在于,所述第一比较电路用于接收所述第二输出信号和所述第四输出信号,并基于所述第二输出信号和所述第四输出信号输出所述第一比较信号;所述第二比较电路用于接收所述第二输出信号和所述第四输出信号,并基于所述第二输出信号和所述第四输出信号输出所述第二比较信号。6.根据权利要求5所述的电路,其特征在于,所述第一模块和所述第三模块均包括n/2个逻辑组件;其中,所述第一组数据信号中的每两个不重复的数据信号作为所述第一模块中的n/2个逻辑组件的输入端;所述第二组数据信号中的每两个不重复的数据信号作为所述第三模块中的n/2个逻辑组件的输入端。7.根据权利要求6所述的电路,其特征在于,n等于4,所述第一模块包括第一逻辑组件和第二逻辑组件;所述第一组数据信号包括第一数据信号、第二数据信号、第三数据信号和第四数据信号;所述第一逻辑组件包括第一与非门和第一或非门,所述第一与非门接收所述第一数据信号和所述第二数据信号,并对所述第一数据信号和所述第二数据信号进行与非运算,得到第一结果;所述第一或非门接收所述第一数据信号和所述第二数据信号,并对所述第一数据信号和所述第二数据信号进行或非运算,得到第二结果;所述第二逻辑组件包括第二与非门和第二或非门,所述第二与非门接收所述第三数据信号和所述第四数据信号,并对所述第三数据信号和所述第四数据信号进行与非运算,得到第三结果;所述第二或非门接收所述第三数据信号和所述第四数据信号,并对所述第三数据信号和所述第四数据信号进行或非运算,得到第四结果;所述第一结果、所述第二结果、所述第三结果和所述第四结果构成所述第一输出信号。8.根据权利要求7所述的电路,其特征在于,所述第三模块包括第三逻辑组件和第四逻辑组件;所述第二组数据信号包括第五数据信号、第六数据信号、第七数据信号和第八数据信号;所述第三逻辑组件包括第三与非门和第三或非门,所述第三与非门接收所述第五数据信号和所述第六数据信号,并对所述第五数据信号和所述第六数据信号进行与非运算,得到第五结果;所述第三或非门接收所述第五数据信号和所述第六数据信号,并对所述第五数据信号和所述第六数据信号进行或非运算,得到第六结果;所述第四逻辑组件包括第四与非门和第四或非门,所述第四与非门接收所述第七数据信号和所述第八数据信号,并对所述第七数据信号和所述第八数据信号进行与非运算,得到第七结果;所述第四或非门接收所述第七数据信号和所述第八数据信号,并对所述第七数据信号和所述第八数据信号进行或非运算,得到第八结果;所述第五结果、所述第六结果、所述第七结果和所述第八结果构成所述第三输出信号。9.根据权利要求8所述的电路,其特征在于,所述第二模块包括第五或非门、第一或门、第二或门、第五与非门、第六与非门、第六或非门和第七与非门;所述第五或非门接收所述第一结果和所述第三结果,并对所述第一结果和所述第三结果进行或非门运算,得到第九结果;所述第一或门接收所述第一结果和所述第四结果,所述第二或门接收所述第二结果和

所述第三结果,所述第一或门的输出端和所述第二或门的输出端均与所述第五与非门连接,所述第五与非门用于对所述第一或门的输出结果和所述第二或门的输出结果进行与非运算,得到第十结果;所述第六与非门接收所述第一结果和所述第三结果,并对所述第一结果和所述第三结果进行与非门运算,得到第十一结果;所述第六或非门接收所述第二结果和所述第四结果,并对所述第二结果和所述第四结果进行或非门运算,得到第十二结果;所述第七与非门接收所述第二结果和所述第四结果,并对所述第二结果和所述第四结果进行与非门运算,得到第十三结果;所述第九结果、所述第十结果、所述第十一结果、所述第十二结果和所述第十三结果构成所述第二输出信号。10.根据权利要求9所述的电路,其特征在于,所述第四模块包括第七或非门、第三或门、第四或门、第八与非门、第九与非门、第八或非门和第十与非门;所述第七或非门接收所述第五结果和所述第七结果,并对所述第五结果和所述第七结果进行或非门运算,得到第十四结果;所述第三或门接收所述第五结果和所述第八结果,所述第四或门接收所述第六结果和所述第七结果,所述第三或门的输出端和所述第四或门的输出端均与所述第八与非门连接,所述第八与非门用于对所述第三或门的输出结果和所述第四或门的输出结果进行与非运算,得到第十五结果;所述第九与非门接收所述第五结果和所述第七结果,并对所述第五结果和所述第七结果进行与非门运算,得到第十六结果;所述第八或非门接收所述第六结果和所述第八结果,并对所述第六结果和所述第八结果进行或非门运算,得到第十七结果;所述第十与非门接收所述第六结果和所述第八结果,并对所述第六结果和所述第八结果进行与非门运算,得到第十八结果;所述第十四结果、所述第十五结果、所述第十六结果、所述第十七结果和所述第十八结果构成所述第四输出信号;所述第二输出信号和所述第四输出信号构成所述预处理信号。11.根据权利要求10所述的电路,其特征在于,所述第一比较电路包括第五逻辑组件、第六逻辑组件、第七逻辑组件和第三与门;所述第五逻辑组件包括第一与门、第二与门和第九或非门;所述第一与门接收第九结果和所述第十八结果,所述第二与门接收所述第十三结果和所述第十四结果,第九或非门与所述第一与门的输出端和所述第二与门的输出端连接,所述第九或非门用于对所述第一与门的输出结果和所述第二与门的输出结果进行或非运算,得到第十九结果;所述第六逻辑组件包括第五或门和第十一与非门;所述第五或门接收所述第十一结果和所述第十二结果,所述第十一与非门与所述第五或门的输出端连接,并接收所述第十五结果,所述第十一与非门用于对所述第五或门的输出结果和所述第十五结果进行与非运算,得到第二十结果;所述第七逻辑组件包括第六或门和第十二与非门;所述第六或门接收所述第十六结果

和所述第十七结果,所述第十二与非门与所述第六或门的输出端连接,并接收所述第十结果,所述第十二与非门用于对所述第六或门的输出结果和所述第十结果进行与非运算,得到第二十一结果;所述第三与门接收所述第十九结果、所述第二十结果和所述第二十一结果,并对所述第十九结果、所述第二十结果和所述第二十一结果进行与运算得到所述第一比较信号。12.根据权利要求11所述的电路,其特征在于,所述第二比较电路包括第十或非门、第八逻辑组件、第九逻辑组件和第十四与非门;所述第十或非门接收所述第九结果和所述第十四结果,并对所述第九结果和所述第十四结果进行或非运算,得到第二十二结果;所述第八逻辑组件包括第四与门、第五与门和第十一或非门;所述第四与门接收所述第十结果和所述第十八结果,所述第五与门接收所述第十五结果和所述第十三结果,所述第十一或非门与所述第四与门的输出端和所述第五与门的输出端连接,所述第十一或非门用于对所述第四与门的输出结果和所述第五与门的输出结果进行或非运算,得到第二十三结果;所述第九逻辑组件包括第七或门、第八或门和第十三与非门;所述第七或门接收所述第十一结果和所述第十二结果,所述第八或门接收所述第十六结果和所述第十七结果,所述第十三与非门与所述第七或门的输出端和所述第八或门的输出端连接,所述第十三与非门用于对所述第七或门的输出结果和所述第八或门的输出结果进行与非运算,得到第二十四结果;所述第十四与非门接收所述第二十二结果、所述第二十三结果和所述第二十四结果,并对所述第二十二结果、所述第二十三结果和所述第二十四结果进行与非运算得到所述第二比较信号。13.根据权利要求3所述的电路,其特征在于,所述信号处理电路包括第十五与非门和第十六与非门;所述第十五与非门接收所述第二比较信号和所述前一笔数据的数据翻转信号,并对所述第二比较信号和所述前一笔数据的数据翻转信号进行与非处理,得到第二十五结果;所述第十六与非门接收所述第二十五结果和所述第一比较信号,并对所述第二十五结果和所述第一比较信号进行与非处理,输出第二十六结果;所述第二十六结果包括:所述当前数据的数据翻转信号、所述第一数据翻转信号和所述第二数据翻转信号中的任意一种。14.一种存储器,其特征在于,包括:存储器单元、以及如权利要求1至13任一项所述的数据总线翻转电路。

技术总结

本公开实施例提供一种数据总线翻转电路和存储器,其中,数据总线翻转电路包括:预处理电路,用于接收当前数据与前一笔数据的比较结果,并对比较结果进行预处理,输出预处理信号;第一比较电路,用于接收预处理信号,并基于预处理信号输出第一比较信号;第一比较信号用于判断比较结果中预设值的数量是否大于等于第一值,预设值表征当前数据与前一笔数据的对应位数据不同;第二比较电路,用于接收预处理信号,并基于预处理信号输出第二比较信号;第二比较信号用于判断预设值的数量是否大于等于第二值;信号处理电路,用于接收第一比较信号、第二比较信号和前一笔数据对应的数据翻转信号,并输出当前数据的数据翻转信号。并输出当前数据的数据翻转信号。并输出当前数据的数据翻转信号。

技术研发人员:吴瑾

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:2022.09.01

技术公布日:2022/12/16

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。