1.本技术涉及半导体制造技术领域,尤其涉及一种半导体机台的气密性检测方法。

背景技术:

2.动态随机存储器(dynamic random access memory,dram)是计算机等电子设备中常用的半导体结构,其由多个存储单元构成,每个存储单元通常包括晶体管和电容器。所述晶体管的栅极与字线电连接、源极与位线电连接、漏极与电容器电连接,字线上的字线电压能够控制晶体管的开启与关闭,从而通过位线能够读取存储在电容器中的数据信息,或者将数据信息写入到电容器中。

3.炉管机台等半导体机台是动态随机存储器等半导体器件制备过程中的重要机台之一,用于在半导体结构表面形成膜层。炉管机台等半导体机台的气密性对半导体制程的影响很大。当炉管机台等半导体机台的气密性不好时,会在半导体结构表面沉积的膜层中产生缺陷。因此,对炉管机台等半导体机台的气密性进行检查,是确保半导体制程持续稳定进行、以及确保半导体结构良率的重要步骤。然而,当前检测炉管机台等半导体机台的气密性的方法成本较高、测试时间较长、应用范围较窄、且检测的准确度较低。

4.因此,如何提高半导体机台气密性检测的准确度,并降低半导体机台气密性检测的成本,缩短半导体机台气密性检测的时间,确保半导体结构的良率,是当前亟待解决的技术问题。

技术实现要素:

5.本技术的一些实施例提供了一种半导体机台的气密性检测方法,用于解决当前半导体机台的气密性检测准确度较低的问题,并降低半导体机台气密性检测的成本,缩短半导体机台气密性检测的时间,以确保半导体产品的良率。

6.根据本技术的一些实施例,本技术提供了一种半导体机台的气密性检测方法,包括如下步骤:

7.形成测试芯片,所述测试芯片包括衬底以及位于所述衬底上的测试膜层,所述测试膜层具有化学反应活性;

8.获取所述测试芯片的第一电阻;

9.放置所述测试芯片至半导体机台内部;

10.于所述半导体机台内部建立真空环境;

11.获取自所述半导体机台内部取出后的所述测试芯片的第二电阻;

12.判断所述第二电阻是否大于所述第一电阻,若是,则确认所述半导体机台的气密性差。

13.在一些实施例中,形成测试芯片的具体步骤包括:

14.提供所述衬底;

15.沉积还原性材料于所述衬底表面,形成所述测试膜层。

16.在一些实施例中,所述还原性材料为金属材料或者金属化合物材料。

17.在一些实施例中,所述测试膜层的厚度为10nm~50nm。

18.在一些实施例中,所述测试膜层的材料为tin。

19.在一些实施例中,获取所述测试芯片的第一电阻的具体步骤包括:

20.获取所述测试芯片中所述测试膜层的第一电阻。

21.在一些实施例中,所述测试芯片的数量为多片;获取所述测试芯片的第一电阻的具体步骤包括:

22.获取与多片所述测试芯片一一对应的多个所述第一电阻。

23.在一些实施例中,放置所述测试芯片至半导体机台内部的具体步骤包括:

24.将多片所述测试芯片间隔放置于所述半导体机台内部的反应腔室内。

25.在一些实施例中,将多片所述测试芯片间隔放置于所述半导体机台内部的反应腔室内的具体步骤包括:

26.沿所述反应腔室的轴线方向,将多片所述测试芯片平行放置于所述反应腔室内。

27.在一些实施例中,所述测试芯片的数量为2片;将多片所述测试芯片间隔放置于所述半导体机台内部的反应腔室内的具体步骤包括:

28.将两片所述测试芯片分别放置于所述反应腔室的底部和顶部。

29.在一些实施例中,于所述机台内部建立真空环境的具体步骤包括:

30.降低所述半导体机台内部的压力至预设压力以下;

31.对所述半导体机台内部进行加热。

32.在一些实施例中,所述预设压力为1torr。

33.在一些实施例中,判断所述第二电阻是否大于所述第一电阻的具体步骤包括:

34.判断每片所述测试芯片的所述第二电阻是否均大于所述第一电阻,若否,则确认所述半导体机台的气密性差。

35.在一些实施例中,还包括:

36.判断所述第二电阻是否大于所述第一电阻,若否,则确认所述半导体机台的气密性好。

37.在一些实施例中,获取自所述半导体机台内部取出后的所述测试芯片的第二电阻之后,还包括如下步骤:

38.去除所述衬底上的所述测试膜层。

39.本技术一些实施例中提供的半导体机台的气密性检测方法,通过形成包括衬底和测试膜层的测试芯片,并获取所述测试芯片在进入半导体机台前后电阻阻值的变化情况,来判断所述半导体机台的气密性好坏,操作简单,测试成本低廉,缩短了半导体机台气密性检测的时间,降低了半导体机台气密性检测的成本,并提高了半导体机台气密性检测的准确度,为确保半导体产品的良率奠定了基础。本技术一些实施例中提供的半导体机台的气密性检测方法不受限于半导体机台的类型,适用范围广。

附图说明

40.附图1是本技术具体实施方式中半导体机台的气密性检测方法流程图;

41.附图2是本技术具体实施方式中测试芯片的结构示意图;

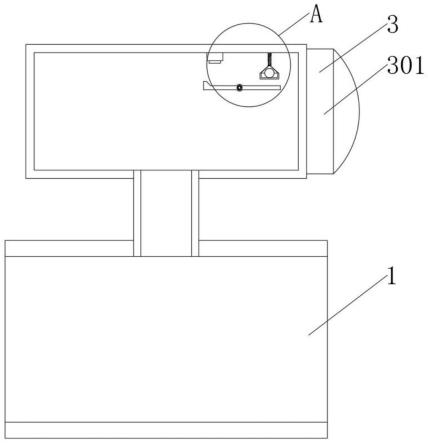

42.附图3是本技术具体实施方式中将测试芯片放入半导体机台内部后的结构示意图。

具体实施方式

43.下面结合附图对本技术提供的半导体机台的气密性检测方法的具体实施方式做详细说明。

44.本具体实施方式提供了一种半导体机台的气密性检测方法,附图1是本技术具体实施方式中半导体机台的气密性检测方法流程图,附图2是本技术具体实施方式中测试芯片的结构示意图,附图3是本技术具体实施方式中将测试芯片放入半导体机台内部后的结构示意图。如图1-图3所示,所述半导体机台的气密性检测方法,包括如下步骤:

45.步骤s11,形成测试芯片30,所述测试芯片30包括衬底20以及位于所述衬底20上的测试膜层21,所述测试膜层21具有化学反应活性。

46.本具体实施方式中所述测试膜层21具有化学反应活性是指,所述测试膜层21能够与空气发生化学反应,例如能够与空气中的一种或者两种以上的成分发生氧化还原反应或者其他类型的化学反应。

47.在一些实施例中,形成测试芯片30的具体步骤包括:

48.提供所述衬底20;

49.沉积还原性材料于所述衬底20表面,形成所述测试膜层21。

50.具体来说,所述衬底20可以是但不限于硅衬底,本具体实施方式以所述衬底20为硅衬底为例进行说明。在其他示例中,所述衬底20可以为氮化镓、砷化镓、碳化镓、碳化硅或soi等半导体衬底。在所述测试芯片30进入待测的所述半导体机台内部之前,在待测的所述半导体机台的外部采用化学气相沉积工艺、物理气相沉积工艺、或者原子层沉积工艺于所述衬底20表面沉积还原性材料,形成所述测试膜层21。

51.本具体实施方式在待测所述半导体机台的外部完成所述测试芯片30的形成工艺,无需向所述半导体机台内部进行所述测试芯片30或者所述测试膜层21的形成工艺,一方面,缩短了所述半导体机台气密性测试的时间,提高了所述半导体机台气密性测试的效率,而且减少了所述半导体机台因气密性测试而造成的停机时间,有助于提高所述半导体机台的产能;另一方面,无需向所述半导体机台内部传输用于形成所述测试芯片30或者所述测试膜层21的原料气体,降低了对所述半导体机台内部造成污染的概率,节省了清洁所述半导体机台的时间。

52.在本具体实施方式中所述测试膜层21为单层结构,以简化所述测试芯片30的形成工艺。在其他示例中,所述测试膜层21也可以为多层结构,例如所述测试膜层21包括沿垂直于所述衬底20的顶面(即所述衬底20朝向所述测试膜层21的表面)的方向叠置的多个子膜层,从而提高所述测试膜层21的化学反应活性,进而能够提高对待测的所述半导体机台气密性检测的精度。

53.在一些实施例中,所述还原性材料为金属材料或者金属化合物材料。

54.具体来说,金属材料或者金属化合物材料具有较高的还原性,若所述半导体机台气密性较差,外界的空气进入所述半导体机台,空气中的氧气就易于与具有较高还原性的金属材料或者金属化合物材料反应,从而使得所述测试芯片30或者所述测试膜层21的电阻

发生改变。其中,所述金属化合物材料可以是但不限于金属氮化物材料。

55.在一些实施例中,所述测试膜层21的材料为tin。

56.所述测试膜层21的厚度不宜过大,否则所述测试膜层21电阻的微小变化不易检测出,从而影响气密性检测结果的准确度。所述测试膜层21的厚度也不宜过小,否则与进入所述半导体机台的空气发生反应后生成的产物的量较少,也会导致所述测试膜层21电阻的变化较小、不易被检测到,从而也会影响气密性检测结果的准确度。在一些实施例中,所述测试膜层21的厚度为10nm~50nm。例如,所述测试膜层21的厚度h为10nm、15nm、25nm、35nm或者40nm。

57.步骤s12,获取所述测试芯片30的第一电阻。

58.在一些实施例中,获取所述测试芯片30的第一电阻的具体步骤包括:

59.获取所述测试芯片30中所述测试膜层21的第一电阻。

60.具体来说,在形成所述测试芯片30之后,于所述半导体机台的外部获取所述测试芯片30中所述测试膜层21的方块电阻,作为所述第一电阻。其中,获取所述测试芯片30中所述测试膜层21的方块电阻的具体方法,本领域技术人员可以根据实际需要进行选择,只要能得到所述第一电阻的阻值即可。

61.在另外一些实施例中,可以直接获取所述测试芯片30的电阻,并以所述测试芯片30整体的电阻值作为所述第一电阻,以简化所述第一电阻的获取操作。

62.在一些实施例中,所述测试芯片30的数量为多片;获取所述测试芯片30的第一电阻的具体步骤包括:

63.获取与多片所述测试芯片30一一对应的多个所述第一电阻。

64.具体来说,通过形成多片所述测试芯片30,后续可以将多片所述测试芯片30同时置于所述半导体机台内部,可以对所述半导体机台内部多个位置的气密性情况同步进行检测,有助于进一步提高所述半导体机台气密性检测的效率。本具体实施方式中的多片是指两片以上。

65.步骤s13,放置所述测试芯片30至半导体机台内部。

66.所述半导体机台可以是但不限于炉管机台。本具体实施方式以所述半导体机台为炉管机台为例进行说明。所述炉管机台的结构如图3所示,包括壳体33、有所述壳体33围绕形成的炉管腔室31、位于所述炉管腔室31内的多条晶圆槽、以及位于所述炉管腔室31底部、用于封闭所述炉管腔室31的底盖32。所述晶圆槽用于承载晶圆,且多条所述晶圆槽沿所述炉管腔室31的轴线方向平行排布。可以通过机械手臂等传输结构将所述测试芯片30传输至所述炉管机台的炉管腔室31内,并放置于所述晶圆槽上。

67.在一些实施例中,放置所述测试芯片30至半导体机台内部的具体步骤包括:

68.将多片所述测试芯片30间隔放置于所述半导体机台内部的反应腔室内。

69.在一些实施例中,将多片所述测试芯片30间隔放置于所述半导体机台内部的反应腔室内的具体步骤包括:

70.沿所述反应腔室的轴线方向,将多片所述测试芯片30平行放置于所述反应腔室内。

71.在一些实施例中,所述测试芯片30的数量为2片;将多片所述测试芯片30间隔放置于所述半导体机台内部的反应腔室内的具体步骤包括:

72.将两片所述测试芯片30分别放置于所述反应腔室的底部和顶部。

73.以下以所述半导体机台为炉管机台、所述测试芯片30的数量为2片为例进行说明。通过机械手臂等传输结构将一片所述测试芯片30放置于所述炉管腔室31内最底层的所述晶圆槽中、另一片所述测试芯片30放置于所述炉管腔室31内最顶层的所述晶圆槽中,如图3所示。这是由于所述炉管腔室31的底部是晶圆进出的通道,在晶圆进入所述炉管腔室31之后,再通过所述底盖32封闭所述炉管腔室31,因此,所述炉管腔室31的底部是易影响整个所述炉管腔室气密性的部分。而所述炉管腔室31的顶部是废气排出的通道,也是易影响整个所述炉管腔室气密性的部分。将两片所述测试芯片30分别放置于所述炉管腔室31的底部和顶部,能够同时对所述炉管腔室31内多个位置的气密性情况同步进行检测,有助于进一步提高所述半导体机台气密性检测的效率。

74.步骤s14,于所述半导体机台内部建立真空环境。

75.在一些实施例中,于所述机台内部建立真空环境的具体步骤包括:

76.降低所述半导体机台内部的压力至预设压力以下;

77.对所述半导体机台内部进行加热。

78.在一些实施例中,所述预设压力为1torr。

79.举例来说,将所述测试芯片30放置于所述炉管腔室31之后,通过所述底盖32封闭所述炉管腔室31。然后,对所述炉管腔室31抽气,使得所述炉管腔室31内的压力降低所述预设压力以下。接着,停止对所述炉管腔室31抽气,对所述炉管腔室31进行加热,关闭与所述炉管腔室31连接的所有阀件,并保持预设时间(例如1分钟~10分钟)。

80.步骤s15,获取自所述半导体机台内部取出后的所述测试芯片30的第二电阻。

81.步骤s16,判断所述第二电阻是否大于所述第一电阻,若是,则确认所述半导体机台的气密性差。

82.在一些实施例中,判断所述第二电阻是否大于所述第一电阻的具体步骤包括:

83.判断每片所述测试芯片30的所述第二电阻是否均大于所述第一电阻,若否,则确认所述半导体机台的气密性差。

84.在一些实施例中,所述半导体机台的气密性检测方法还包括:

85.判断所述第二电阻是否大于所述第一电阻,若否,则确认所述半导体机台的气密性好。

86.以下以所述测试膜层21的材料为tin、所述半导体机台为炉管机台为例进行说明。当所述炉管机台的气密性好时,于所述炉管机台内部建立真空环境的步骤相当于给所述测试膜层21加热,会除去所述测试膜层21中的杂质元素,例如氯元素、碳元素、氧元素中的一种或两种以上,使得所述测试膜层21的电阻降低,即使得所述第二电阻小于所述第一电阻。若所述测试膜层21的纯度较高,不含有杂质元素,则所述第二电阻等于所述第一电阻。

87.当所述炉管机台的气密性差时,在所述炉管机台内部建立真空环境、并对所述炉管机台进行加热的过程中,进入所述炉管机台的氧气会与所述测试膜层21发生如下反应:

88.2tin 2o2=2tio2 n289.tio2的生成会使得所述测试膜层21的电阻增大,即使得所述第二电阻大于所述第一电阻。

90.若确定所述半导体机台的气密性差,则对所述半导体机台进行气体吹扫之后,对

所述半导体机台进行维护。在维护之后,再次通过阻值检测的方式检测所述半导体机台的气密性,直至所述第二电阻等于或者小于所述第一电阻。

91.在一些实施例中,获取自所述半导体机台内部取出后的所述测试芯片的第二电阻之后,还包括如下步骤:

92.去除所述衬底20上的所述测试膜层21。

93.具体来说,在完成所述半导体机台的气密性检测之后,可以采用湿法清洗的方式去除所述衬底20上的所述测试膜层21,实现所述衬底20的循环使用,从而进一步降低所述半导体机台气密性检测的成本。例如,当所述测试膜层21的材料为tin时,在完成对所述半导体机台的气密性检测之后,可以采用酸性溶液(例如h2so4溶液)去除所述衬底20上的所述测试膜层21。

94.本具体实施方式中提供的半导体机台的气密性检测方法,通过形成包括衬底和测试膜层的测试芯片,并获取所述测试芯片在进入半导体机台前后电阻阻值的变化情况,来判断所述半导体机台的气密性好坏,操作简单,测试成本低廉,缩短了半导体机台气密性检测的时间,降低了半导体机台气密性检测的成本,并提高了半导体机台气密性检测的准确度,为确保半导体产品的良率奠定了基础。本技术一些实施例中提供的半导体机台的气密性检测方法不受限于半导体机台的类型,适用范围广。

95.以上所述仅是本技术的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本技术原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本技术的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。