使用底部填充的电压调节模块设计

1.相关申请的交叉引用

2.本技术要求2021年1月22日提交的标题为“底部填充的电压调节模块设计(voltage regulating module design for underfill)”的美国临时专利申请第63/140,547号的权益,该专利申请的公开内容通过引用整体并入本文并且用于所有目的。

技术领域

3.本公开总体涉及电子器件,并且更特别地,涉及电压调节模块(vrm)。

背景技术:

4.多芯片模块可以包含多个专用集成电路(asic)设备和多个vrm,该多个vrm被配置为向asic中的每个供电。给定的vrm可以经由球栅阵列(bga)电耦合到asic设备中的一个asic设备。为了保护bga,可以使用底部填料来封装bga。

技术实现要素:

5.在一个方面,提供了一种电压调节模块(vrm),其包括:第一层,其被配置为输出基于逐步降低的电压的调节电压,该第一层具有第一凹部;第二层,其与该第一层堆叠,该第二层包括多个有源部件,该多个有源部件被配置为接收电压,基于该电压生成该逐步降低的电压,并且将该逐步降低的电压提供给该第一层,该第二层具有与该第一凹部重叠的第二凹部,该第一凹部具有比该第二凹部更大的占用空间;以及多个触头,其在第一层上并且被配置为输出调节电压。

6.多个触头可以包含球栅阵列。

7.球栅阵列可以用底部填料封装。

8.vrm还可以包括与第一层和第二层堆叠的第三层,该第三层可以包括多个有源元件。

9.第三层可以具有第三凹部,该第三凹部具有基本上为第二凹部的面积的面积。

10.第一层可以包括多个分立部件,该多个分立部件被配置为倍增逐步降低的电压的电流。

11.分立部件可以包括无源电路元件。

12.在另一个方面,提供了一种多芯片模块,其包括:多个集成电路(ic)管芯;电压调节模块(vrm)阵列,其中vrm阵列被布置成使得在vrm阵列的一组邻近vrm之间存在包含埋头孔的开口,并且其中多个vrm中的每个都与多个ic管芯中的相应ic管芯堆叠;以及紧固件,其位于vrm阵列的邻近vrm组之间的开口中。

13.vrm阵列中的每个vrm可以包含封装在底部填料中的球栅阵列。

14.该组vrm中的每个vrm都可以具有第一层和第二层,其中第一层与紧固件的间隙大于第二层,并且其中第一层包含无源部件并且第二层包含无源部件。

15.在又一个方面,一种多芯片模块,其包括:多个集成电路(ic)管芯;多个电压调节

模块(vrm),其中vrm中的每个vrm与多个ic管芯中的相应ic管芯堆叠;以及多个紧固件,其位于多个vrm的vrm之间的开口中;其中该多个vrm中的第一vrm包括:第一层,其被配置为输出基于逐步降低的电压的调节电压,该第一层具有第一凹部;第二层,其与第一层堆叠,第二层包括多个有源部件,该多个有源部件被配置为接收电压并且将逐步降低的电压提供给第一层,第二层具有与第一凹部重叠的第二凹部,第一层与多个紧固件中的第一紧固件的间隙比第二层大,第一紧固件位于开口的第一开口中,第一开口至少部分地由第一凹部和第二凹部限定;以及多个触头,其在第一层上并且电连接到与第一vrm堆叠的多个ic管芯中的第一ic管芯,该多个触头被配置为向第一ic管芯提供调节电压。

16.多个触头可以包含球栅阵列。

17.bah栅格阵列可以用底部填料封装。

18.第一层的间隙可被配置为阻止或防止底部填料堵塞第一凹部。

19.底部填料可以形成从第一层的边缘朝向紧固件延伸的圆角。

20.圆角从第一层的边缘朝向紧固件延伸的距离可以小于第一层间隙和第二层间隙之间的距离。

21.第一层可以包括多个无源电路元件,该多个无源电路元件被配置为倍增逐步降低的电压的电流。

22.紧固件可以包括螺栓。

23.多芯片模块还可以包括冷却系统,该冷却系统被配置为主动冷却vrm。

24.晶片上系统(sow)可以包含ic管芯。

25.多芯片模块还可以包括散热结构,该散热结构形成于sow的与第一层和第二层相对的一侧上。

附图说明

26.图1为根据本公开内容的各个方面构建的多芯片模块的一个实施例的侧截面框图。

27.图2a和图2b图示了根据本公开的各方面的处理系统。

28.图3为图2a和图2b的晶片上系统模块的局部横截面视图。

29.图4a和图4b图示了根据本公开的各方面的包含用于螺栓的凹部的vrm的局部平面图。

30.图4c图示了根据本公开的各方面的布置成阵列的多个vrm的平面图。

31.图5a和图5b图示了根据本公开的各方面的用于底部填充的vrm设计的横截面视图。

32.图6图示了根据本公开的各方面的安装到asic的vrm的横截面视图。

具体实施方式

33.某些实施例的以下具体实施方式呈现了特定实施例的各种描述。然而,本文所描述的创新可以以多种不同的方式(例如,根据权利要求所限定和涵盖的方式)来实施。在本说明书中,参考了附图,其中相同的附图标记和/或术语可以指示相同或功能类似的元件。应理解的是,图中所示的元件不一定是按比例绘制的。此外,应理解的是,某些实施例可以

包含比附图中所示更多的元件和/或附图中所示元件的子集。此外,一些实施例可以结合来自两个或更多附图的特征的任何合适的组合。

34.在某些实现方式中,除多个专用集成电路(asic)设备外,基板上系统的机械架构还涉及基板上电压调节模块(vrm)的高密度封装。存在许多影响基板上vrm的尺寸、布局、密度、间距等的设计权衡和/或挑战。一个特别的挑战涉及在vrm内层中为有源和无源部件、用于将vrm紧固到基板的带肩螺栓以及底部填充分配空间。本公开提供了针对此类挑战的技术解决方案。

35.本公开涉及vrm设计,该vrm设计在vrm的底部球栅阵列(bga)附着层上具有凹部区域,此设计的某些优点包含有助于节省vrm布局内的物理空间,使得vrm可以满足底部填充和螺栓间隙规范,这是使能后端组装过程的重要因素。此外,本公开的方面还可以保持vrm内层空间规格,特别是对于有源部件,并且基板上的整体vrm封装密度不会受到显著影响。

36.前几代bga型vrm不具有能够使能高封装密度的灵活设计。制造挑战很多,范围从工具对准和钻孔真实位置公差。相比之下,根据本公开的方面的设计是独特的并且还没有被用于解决前述挑战。

37.本公开的各方面涉及可以集成到涉及具有相对高封装密度的后端组件的产品中的vrm架构。该架构可以集成到紧邻放置的产品中。在某些实现方式中,vrm可以由能够承受机加工以实现尺寸稳定性的材料形成。可以用于vrm的材料的非限制性示例包含:印刷电路板(pcb)、有机基板和/或用工程成型化合物包覆成型的pcb或有机基板。vrm架构可以包含凹部的埋头孔特征,该凹部的埋头孔特征可以改善部件放置和/或使能后端组装。vrm的机械结构是可以影响增强和/或最佳asic性能的功率传输的一个方面。例如,vrm的较低封装密度可能导致asic性能的显著劣化。

38.vrm可以包含多个层,该多个层至少包含第一层和第二层。这些层中的一层或多层可以包含有源部件,诸如晶体管。有源元件可以降低接收到的电压并且输出逐步降低的电压。vrm的另一个层可以包含无源部件,诸如电容器和/或电感器。此层可以向其上的电触头(诸如球栅阵列)输出调节的电压。调节电压基于逐步降低的电压。

39.具有无源部件的层具有与具有有源部件的一层或多层中的每一层的凹部重叠的凹部。具有无源部件的层的凹部可以比具有有源元件的层的对应凹部具有更大的占用空间。因此,与具有有源元件的层的凹部的占用空间相比,具有无源部件的层的凹部的占用空间在下层元件上具有更大的面积。具有无源部件的层的凹部可以提供与紧固件(诸如螺栓)的更大间隙,该紧固件定位在至少部分由vrm层中的凹部限定的开口中。此类vrm的阵列可以包含在多芯片模块中。例如,vrm可以与相应的asic堆叠并且向其提供调节电压。至少部分地由vrm拐角处和邻近vrm之间的凹部限定的用于紧固件开口可各自形成埋头孔特征。例如,在4个vrm的拐角处的凹部可以限定开口。作为另一个示例,在4个vrm和一个或多个中间结构的拐角处的凹部可以限定开口。具有无源部件的vrm层具有带有较大紧固件间隙的凹部,可以至少部分地限定埋头孔特征。利用埋头孔特征,vrm可以被密集封装,而不牺牲包含有源部件的一个或多个vrm层的面积。

40.本公开的实施例涉及多芯片模块的vrm设计。在一些实施例中,多芯片模块可以安装到晶片上系统(sow)的再分布层或集成扇出(info)封装。在一个实施例中,多芯片模块包含模块化直接夹紧结构,该模块化直接夹紧结构允许安装多个ic或插口,该多个ic或插口

被安装到散热结构上并且机械耦合到散热结构以热冷却多芯片模块中的集成电路(ic)管芯。在一个实施例中,ic管芯或插口安装在info基板的与散热结构相对的一侧上。

41.将多芯片模块安装至info基板和/或散热结构时,可使用被配置为固定多个芯片的框架。例如,框架的尺寸和形状可以被设定为保持2个、4个、6个、8个、10个、12个或更多个ic管芯,如下文更详细地描述的。在又一些实施例中,由框架可以帮助16、25或36个ic管芯。在一个实施例中,框架是矩形或正方形的以围绕ic管芯的每一侧并且为多芯片模块提供稳定的安装系统或器件。在模块内的ic管芯的每个角处,可以是框架中的通孔以允许安装pm、螺钉或其它紧固件将框架安装到基板和冷却系统。如图中所示,可以使用一个或多个角夹将多芯片模块框架固定到封装的剩余部分。

42.图1是图示根据本公开的各方面构建的处理系统100的侧截面视图。处理系统100可以是多芯片模块。图1的处理系统100。图1包含安装在基板结构104上的多个高功率vrm 102。vrm 102由直流(dc)电源电压108(例如40伏、48伏或另一相对高的电压)供电,并且相应地向相应的多个ic管芯106提供调节电压。在一些实施例中,多个vrm 102中的每个产生约0.8伏的输出并且向相应的多个ic管芯106提供约600瓦或更多的功率。然而,本公开的各方面不限于此并且根据实施例,vrm 102可以产生约0.6伏至1.3伏范围内、0.8伏至1.1伏范围内或另一个合适电压范围内的输出。因此,在某些实施例中,多个vrm 102中的每个向多个ic管芯106产生超过约100安培的电流。在某些应用中,vrm可以向多个ic管芯106提供范围从400安培到800安培的电流。

43.图2a和图2b显示了根据本公开的各方面的处理系统200。图2a是处理系统200的分解图。图2b是处理系统200的组装图。本公开的特征可以在处理系统200和/或任何其它合适的处理系统中实现。处理系统200可以具有高计算密度并且可以消散由处理系统200生成的热量。在某些应用中,处理系统200可以每秒执行数万亿次操作。处理系统200可以用于和/或专门配置用于高性能计算和/或计算密集型应用,诸如神经网络训练和/或处理、机器学习、人工智能等。在实施例中,处理系统200可以用于神经网络训练。处理系统200可以实现冗余。在一些应用中,处理系统200可以用于神经网络训练以生成供车辆(例如,汽车)的自动驾驶系统使用的数据。

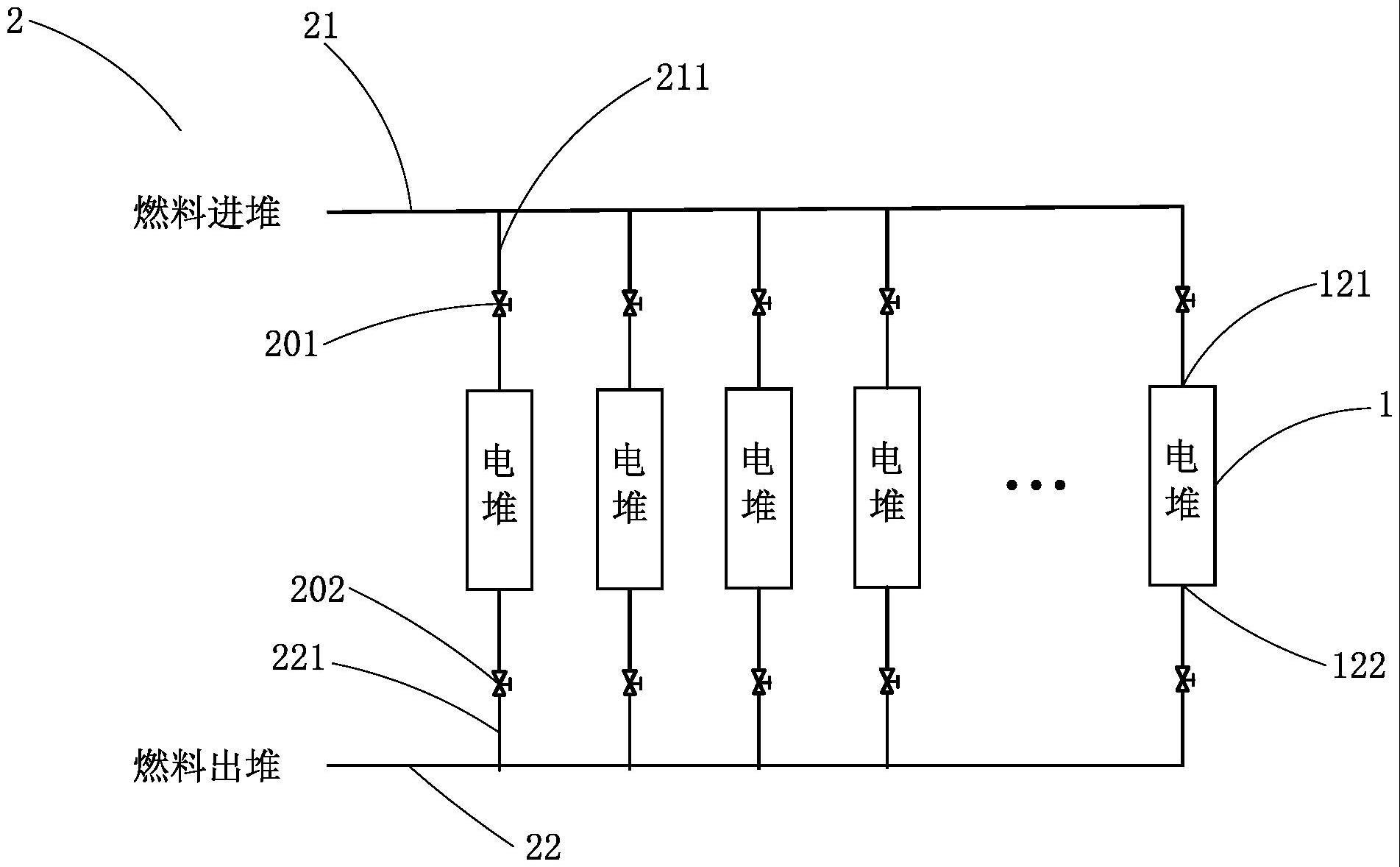

44.如图2a所示,加工系统200包含散热结构202、sow 204、边缘加强件206、vrm 208、冷却系统210和控制板212。图2b示出了相对于图2a颠倒的处理系统200。图2b中示出了没有控制板212的处理系统200。

45.散热结构202可以消散来自sow 204的热量。散热结构202可以包含散热器。此类散热器可以包含金属板。备选地或另外地,散热结构可以包含散热器。散热结构202可以包含金属,诸如铜和/或铝。散热结构202可以备选地或另外地包含具有期望的散热特性的任何其它合适的材料。在某些应用中,散热结构202可以包含铜散热器和铝散热器。热接口材料可以包含在散热结构202和sow 204之间以降低和/或最小化传热阻力。

46.sow 204可以包含ic管芯阵列。ic管芯可以嵌入成型材料中。sow 204可以具有高计算密度。ic管芯可以是半导体管芯,诸如硅管芯。ic管芯阵列可以包含任何合适数量的ic管芯。例如,ic管芯阵列可以包含16个ic管芯、25个ic管芯、36个ic管芯或49个ic管芯。例如,sow 204可以是info晶片。info晶片可以包含ic管芯阵列上方的多个布线层。例如,在某些应用中,info晶片可以包含4个、5个、6个、8个或10个布线层。info晶片的布线层可以提供

ic管芯之间和/或到外部部件的信号连接。sow 204可以具有相对大的直径,诸如在10英寸至15英寸范围内的直径。作为一个示例,sow 204可以具有12英寸的直径。

47.边缘加强件206可以有助于加工系统200的结构完整性。边缘加强件206可以为vrm 208提供支撑并且将vrm 208保持在适当的位置。

48.可以将vrm 208定位成使每个vrm与sow 204的ic管芯堆叠在一起。在处理系统200中,存在vrm 208的高密度封装。因此,vrm 208会消耗大量功率。vrm 208被配置为接收直流(dc)电源电压并且向sow 204的对应ic管芯供应较低的输出电压。

49.冷却系统210可以为vrm 208提供主动冷却。冷却系统210可以为控制板212提供主动冷却。冷却系统210可以包含具有用于传热流体流过的流动路径的金属。作为一个示例,冷却系统210可以包含机加工的金属,诸如铜。冷却系统210可以包含用于高冷却效率的钎焊散热片阵列。在组装好的处理系统200中,冷却系统210可以用螺栓固定到散热结构202。这可以为sow 204提供结构支撑和/或可以减少sow 204破裂的机会。热接口材料可以包含在冷却系统210和控制板212之间以降低和/或最小化传热阻力。

50.控制板2.12可以包含电气部件。控制板2.12的电子器件可以为vrm 208提供控制信号。控制板212可以包含电子设备来控制sow204的操作。

51.图3为图2a和图2b的sow模块200的局部横截面视图。参考图3,sow模块200包含散热结构202、sow 204、vrm 208和冷却系统210。sow模块200还包含vrm 208和冷却系统210之间的热接口结构214以及被配置为将vrm 208紧固在适当位置的多个螺栓216。

52.图4a和4b图示了根据本公开的各方面的包含用于螺栓306的凹部308的vrm 302的局部平面图。图4c图示了根据本公开的方面的布置成阵列300的多个vrm 302的平面图。如图4c中所示,四个邻近vrm 302的凹部308可以形成螺栓孔310,螺栓可以放置在该螺栓孔中。在图4c中,螺栓孔310至少部分由四个vrm 302的凹部308限定。螺栓孔310是至少部分由vrm 302的凹部308限定的开口的示例。此类开口可以由vrm 302的凹部308之间的空间形成。此类开口可以由vrm 302的凹部308内的一个或多个中间结构之间的空间形成。

53.参考图4a和图4b,凹部308限定禁止区以便为一个或多个vrm 302邻近的螺栓306的插入和(一个或多个)vrm 302的固定提供间隙。例如,禁止区可以由vrm 302的边缘和螺栓306之间的最小距离或间隙d来限定。如图所示,螺栓306可以是带肩螺栓。可以使用任何其它合适的紧固件来代替螺栓。

54.同样如图4a中示出的,bga 304设置在vrm 302的一端以提供给sow 204的电连接(见图2a至图3)。bga 304可以与vrm 302的边缘间隔开最小距离或间隙e并且可以限定bga 304中的球之间在对角线方向上的节距f,如图所示。如上面所描述的,bga 304可以被施加底部填料,该底部填料被配置为当安装到sow 204上时封装bga 304并且向bga 304提供结构支撑,从而防止损坏bga 304。在一个实现方式中,间隙d可以是约600pm,间隙e可以是约500pm,并且节距f可以是约550pm。然而,在其它实施例中,这些距离中的每个都可以更大或更小。

55.可能存在可以影响由螺栓306和vrm 302边缘之间的间隙d确定的禁止区的尺寸多种竞争性设计考虑因素。例如,为了保护邻近凹部308的bga 304的球,底部填料可以占据bga 304和螺栓306之间的一定量的空间。在一些实施例中,底部填料可以包含以液体形式施加并且固化以封装bga 304的成型材料或聚合物,如果在vrm 302的边缘和螺栓306之间

没有足够的空间(例如,禁止区或间隙d),底部填料可能堵塞凹部308,这可能使得螺栓306穿过由一个或多个凹部308形成的螺栓孔310的插入变得困难或不可能。在某些实现方式中,可以规定提供由约1.1mm的间隙d限定的禁止区。间隙d可以是1.1mm /-约3%。根据实现情况,禁止区可以更大或更小。

56.用于增加禁止区尺寸的一个选项是在邻近vrm 302之间提供另外的间距。然而,这可能具有增加vrm 302占据的总面积的缺点。对于某些实现方式,可以放置vrm 302的区域(例如,在边缘加强件206内)是固定的,并且因此,在不减小单个vrm 302的尺寸或可以包含在多芯片模块中的vrm 302的数量的情况下,vrm 302之间的间距不能增加。例如,如图4c中所示,某些多芯片模块可以包含相应地耦合到vrm 302的asic阵列。如图所示,在图4c中有25个asic和25个vrm。为了保持vrm 302的尺寸并且提供足够大的禁止区以防止底部填充堵塞凹部308,在4

×

4阵列中asic和vrm 302的数量可以减少到16个。此减少将显著影响多芯片模块的整体性能。

57.参考图4b,可以通过从最靠近凹部308的图4abga 304中移除三个球的行来增加禁止区的尺寸,从而增加间隙d。然而,在不牺牲vrm 302的一些功能的情况下减小各个vrm 302的尺寸或vrm 302的数量可能是困难的或不切实际的。例如,vrm 302的部件可以被密集地封装,使得部件不会全部装配在vrm 302的减小的区域内以提供足够大的禁止区以避免底部填充材料堵塞凹部308。例如,减少vrm 302的尺寸或vrm 302的数量可以减少可以传送到asic的功率量,导致asic性能的降低。在一些实现方式中,间隙d可以是1.1mm /-约3%并且间隙e可以是约550微米 /-约20%。

58.本公开的各方面涉及一种vrm 302设计,该vrm 302设计可阻止或基本上防止因底部填充造成的凹部308堵塞,而不会增加vrm 302之间的间距,也不会牺牲vrm 302的功能。图5a和图5b图示了根据本公开的各方面的用于底部填充的vrm设计的横截面视图。最靠近bga的vrm 400的层可以具有比vrm 400的有源层更大的凹部。因此,bga可以通过最靠近bga的层的足够间隙来保护并且有源层可以保持比最靠近bga的层更高的密度和更小的凹部。

59.参考图5a,vrm 400包含第一层402、第二层404、第三层406和bga 408。vrm 400还包含在vrm 400的拐角处形成的多个凹部412。例如,如图4c中所示,多个邻近vrm 400的凹部412可以形成螺栓孔。第二层404和第三层406相应地可以包含有源部件(例如,诸如晶体管的硅部件),该有源部件被配置为将输入电压逐步降低和/或重复到sow 204可以使用的电压。因此,第二层404和第三层406可以被称为有源层。在某些实现方式中,第二层404和/或第三层406的至少一部分可以使用asic设备来实现以降低输入电压,导致对这些层404和406的形状因子的限制。特别地,asic设备的使用可能限于第二层404和第三层406的某些占用空间。

60.在一个示例中,vrm 400可以接收48v的输入电压并且向sow204提供0.8v或1.1v的输出。根据实现方式,可以使用任何其它合适的输入电压和/或输出电压。因此,第二层404和第三层406可以被配置为用作降压变压器。在一些实现方式中,第二层404和第三层406可以包含一个或多个电流分配器和/或一个或多个电流倍增器,该一个或多个电流分配器和/或一个或多个电流倍增器被配置为逐步降低由vrm 400接收到的输入电压。

61.第一层402可以包括多个电流倍增器部件,该多个电流倍增器部件可为离散部件,而非包含在第二层404和第三层406中的有源部件。分立部件可以是无源电路元件。例如,第

一层402的分立部件可以包含一个或多个电阻器、一个或多个电容器、一个或多个电感器或其任何合适的组合。与有源部件相比,分立部件的放置可以具有更大的灵活性,从而与第二层404和第三层406相比,第一层402的部件的布局设计能够具有更大的灵活性。通过分立部件的某种放置,可以减小第一层402的面积。因此,可以减小第一层402的面积,而不会显著影响vrm 400的功能。

62.图5b图示了图5a的vrm 400的靠近凹部412的部分410的放大图。参考图5b,通过减小第一层402的尺寸而不调整第二层404和第三层406的尺寸,可以在凹部412中提供台阶或凹口414以增大邻近bga 408的螺栓周围的禁止区的尺寸,而不减小包含有源元件的第二层404和第三层406的尺寸。第一层402中的凹部比第二层404和第三层406中的凹部具有更大的占用空间。第一层402中的凹部可以提供比第二层404和第三层406中的凹部更大的螺栓间隙。由第一层402中的凹部形成的凹口414连同邻近vrm 400中的第二层404和第三层406中的凹部(例如,见图4g)一起可以形成埋头孔。因此,可以提供底部填料(例如,参见图6所示的底部填料502)来保护bga 408并且由第一层402中的凹口414提供的增大尺寸的禁止区可以防止底部填料堵塞凹部412。另外,由于施加底部填料以保护邻近第一层402的bga 408,所以可以维持第二层404和第三层406的尺寸,因为底部填料到达这些层404和406的风险很小甚至没有。因此,可以保持具有有源元件的第二层404和第三层406的尺寸以确保保持vrm 400的性能以及第二层404和第三层406的密度。

63.底部填料可以形成从第一层402的边缘朝向螺栓延伸的圆角。在一些实现方式中,圆角从第一层402的边缘向由凹部412和邻近vrm的类似凹部形成的螺栓孔的中心延伸的距离小于第二层404和第三层406处的凹部412的间隙和第一层402处的凹部412的间隙之间的距离。也就是说,与第二层404和第三层406朝向螺栓孔的中心延伸的距离相比,圆角朝向螺栓孔的中心延伸的距离不会更远。然而,在一些其它实施例中,圆角可以比第二层404和第三层406更进一步地朝向螺栓延伸。

64.图6图示了根据本公开的各方面的安装到asic 500的vrm 400的横截面视图。如图6中所示,vrm 400包含bga 408,该bga 408被配置为在vrm 400和asic 500之间提供多个电连接。bga 408由底部填料502封装,底部填料502为bga 408提供结构支撑并且物理保护bga 408。如图6中所示,底部填料502形成了从vrm 400的边缘沿着asic 500朝向vrm 400的拐角处的凹部412形成的螺栓孔延伸的圆角。如上面所描述的,由于凹口414的存在,由底部填料502形成的圆角不会像不包含凹口414的类似vrm中那样向螺栓孔的中心延伸得那么远。

65.小结

66.前述公开内容无意将本公开内容限制在所公开的精确形式或特定使用领域。因此,鉴于本公开可以考虑对本公开的各种替代实施例和/或修改,无论是本文明确描述的还是暗示的,都是可能的。已经如此描述了本公开的实施例,本领域普通技术人员将认识到,在不脱离本公开的范围的情况下,可以在形式和细节上进行改变。因此,本公开仅受权利要求的限制。

67.在前述说明书中,已参考特定实施例对本公开进行了描述。然而,如本领域技术人员将意识到的,在不脱离本公开的精神和范围的情况下,可以修改本文公开的各种实施例或以各种其它方式实现。因此,此描述被认为是说明性的并且是为了教导本领域技术人员制造和使用所公开的通风口组件的各种实施例的方式。应理解的是,本文示出和描述的公

开形式将被视为代表性实施例。等效的元件、材料、过程或步骤可以替代本文代表性地图示和描述的那些。此外,本公开的某些特征可以独立于其它特征的使用而被利用,所有这些对于受益于本公开的描述的本领域技术人员来说都是显而易见的。用于描述和要求本公开内容的诸如“包含”、“包括”、“并入”、“由

……

组成”、“具有”、“是”的表达旨在以非排他性的方式来解释,即允许未明确描述的项目、部件或元件也存在。对单数的引用也应被解释为涉及复数。

68.此外,本文公开的各种实施例应被理解为说明性和解释性的,并且决不应被解释为对本公开的限制。所有的连结参考(例如,附接、固定、耦合、连接等)仅用于帮助读者理解本公开,并且不会产生限制,特别是关于本文公开的系统和/或方法的位置、取向或使用。因此,如果有的话,连结参考应被广义地解释。此外,此类连结参考不一定意味着两个元件彼此直接连接。另外,所有数字术语,诸如但不限于“第一”、“第二”、“第三”、“初级”、“次级”、“主要”或任何其它普通和/或数字术语,也应仅被视为识别符以辅助读者理解本公开的各种要素、实施例、变型和/或修改,并且不可产生任何限制,特别是关于相对于或超过另一个要素、实施例、变型和/或修改的任何要素、实施例、变型和/或修改的顺序或偏好。

69.还应认识到,附图/图中描绘的一个或多个元件也可以通过更加分离或集成的方式实现,或甚至在某些情况下移除或使其不可操作,如根据特定应用是有用的。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。