像素驱动电路、显示面板的制作方法

- 国知局

- 2024-06-21 13:37:47

本技术涉及显示,具体涉及一种像素驱动电路、显示面板。

背景技术:

1、现有阈值电压偏移的外部补偿所需时间较长,通常在开机阶段通过ee模块实现vth的侦测,通过ic将信号写入data信号中实现补偿,但仅开机补偿一次,不能实现实时补偿。为解决上述问题,又开发了一种基于阈值电压偏移的内部补偿电路,通过驱动电路设计可实现实时补偿,但补偿范围会受到电路架构的限制,补偿范围较小,并且像素驱动电路由于目前阈值电压的偏移有批次性差异,单一时序的内部补偿电路难以完全补偿全部批次的阈值电压偏移。

2、因此,现有像素驱动电路存在无法兼顾实时补偿与较大补偿范围的技术问题。

技术实现思路

1、本技术实施例提供一种像素驱动电路、显示面板,可以缓解现有像素驱动电路存在无法兼顾实时补偿与较大补偿范围的技术问题。

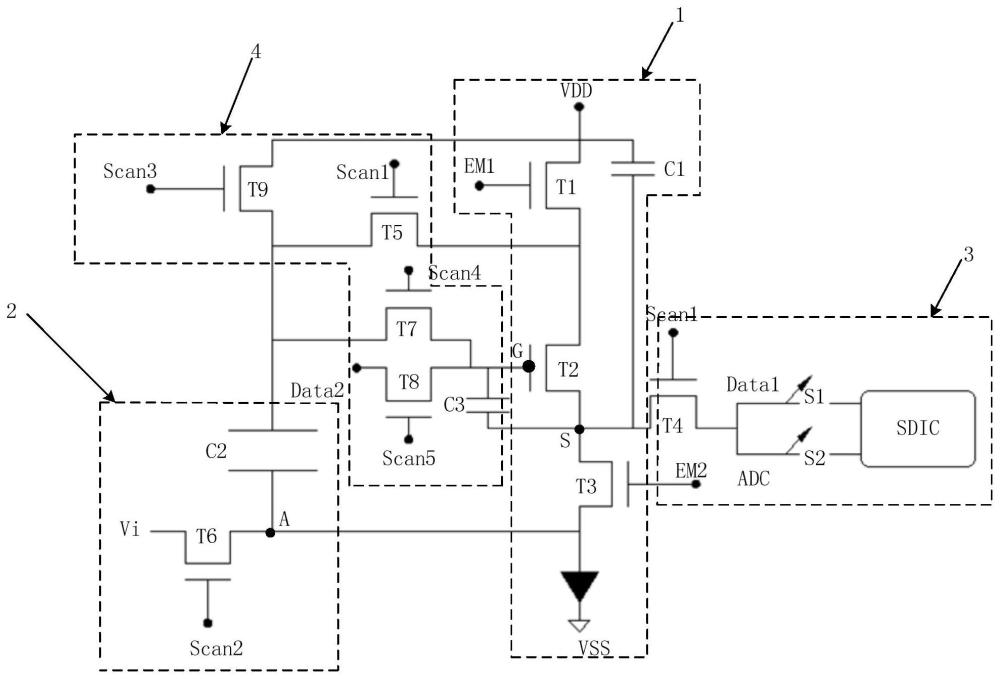

2、本技术实施例提供一种像素驱动电路,包括发光模块、外部侦测模块、内部补偿模块,所述发光模块与所述外部侦测模块、所述内部补偿模块电连接;其中,

3、所述发光模块包括第二晶体管和发光单元,所述第二晶体管的第一极与电源高电频信号电连接,所述第二晶体管的第二极与发光单元电连接;

4、所述外部侦测模块被配置为在显示面板开机时获取所述第二晶体管的阈值电压,并预测所述阈值电压的偏移方向;

5、所述内部补偿模块被配置为在所述阈值电压的偏移方向为正偏时,采用第一时序补偿所述阈值电压;所述内部补偿模块被配置为在所述阈值电压的偏移方向为负偏时,采用第二时序补偿所述阈值电压;所述第一时序与所述第二时序不同。

6、可选的,在本技术的一些实施例中,当所述阈值电压大于或等于0时,所述内部补偿模块被配置为采用第一时序补偿所述阈值电压,所述阈值电压的补偿范围为第一范围;当所述阈值电压小于0时,所述内部补偿模块被配置为采用第二时序补偿所述阈值电压,所述阈值电压的补偿范围为第二范围,所述第一范围与所述第二范围不同。

7、可选的,在本技术的一些实施例中,所述第一范围为0至4v,所述第二范围为-3v至2v。

8、可选的,在本技术的一些实施例中,所述像素驱动电路为9t3c电路,所述发光模块还包括第一晶体管、第三晶体管以及第一电容,所述第一晶体管的栅极接入第一发光信号,所述第一晶体管的第一极接入所述电源高电频信号,所述第一晶体管的第二极与第二晶体管的第一极连接,所述第二晶体管的第二极与所述第三晶体管的第二极连接,所述第三晶体管的第一极与所述发光单元的阳极连接,所述第三晶体管的栅极接入第二发光信号,所述发光单元的阴极接入电源低电频信号,所述第一电容的一端与所述第一晶体管的第一极连接,所述第一电容的另一端与所述第二晶体管的第二极连接;所述外部侦测模块包括第一开关、第二开关、芯片、所述第四晶体管,所述第四晶体管的栅极接入第一扫描信号,所述第四晶体管的第二极与所述第二晶体管的第二极电连接,所述第四晶体管的第一极通过并联设置的第一支路和第二支路分别与所述芯片连接,所述第一支路包括所述第一开关,所述第二支路包括所述第二开关;所述内部补偿模块包括第三电容、第五晶体管、第七晶体管、第八晶体管以及第九晶体管,所述第三电容的一端连接所述第二晶体管的栅极,所述第三电容的另一端连接所述第二晶体管的第二极,所述第五晶体管的栅极接入第一扫描信号,所述第五晶体管的第二极与所述第九晶体管的第二极电连接,所述第五晶体管的第一极与所述第一晶体管的第二极连接,所述第九晶体管的第一极与所述第一晶体管的第一极连接,所述第九晶体管的栅极接入第三扫描信号,所述第七晶体管的第二极与所述第九晶体管的第二极连接,所述第七晶体管的第一极与所述第二晶体管的栅极电连接,所述第七晶体管的栅极接入第四扫描信号,所述第八晶体管的栅极接入第五扫描信号,所述第八晶体管的第一极接入第二数据信号,所述第八晶体管的第二极连接于所述第二晶体管的栅极。

9、可选的,在本技术的一些实施例中,所述像素驱动电路还包括复位模块,所述复位模块包括第六晶体管和第二电容,所述第六晶体管的栅极接入第二扫描信号,所述第六晶体管的第二极与所述发光单元的阳极、所述第二电容连接,所述第六晶体管的第一极接入复位信号。

10、可选的,在本技术的一些实施例中,所述外部侦测模块的工作阶段包括初始化阶段、存储阶段和侦测阶段;在所述初始化阶段,所述外部侦测模块对所述第二晶体管的栅极的g点电位以及第二极的s点电位进行复位,在所述存储阶段,所述外部侦测模块对所述第二晶体管的第二极进行充电使所述第二晶体管关断,在所述侦测阶段,所述外部侦测模块读取所述第二晶体管的阈值电压。

11、可选的,在本技术的一些实施例中,在所述初始化阶段,所述第一扫描信号和所述第五扫描信号为高电位,所述第四晶体管打开、所述第八晶体管打开,所述第二数据信号处于低电位,所述第二晶体管的栅极g点写入所述第二数据信号的低电位vdatal,第二晶体管的第二极s点写入恒定的参考电压vref,此时,g点的电位vg、s点的电位vs初始化,其中,vs=vref,vg=vdatal;

12、在所述存储阶段,所述第五扫描信号为高电位,所述八晶体管打开,所述第二数据信号处于高电位,此时,g点写入所述第二数据信号的高电位vdatah,所述第二晶体管打开,s点开始充电,当vs=vdatah-vth时,所述第二晶体管关闭,其中,所述第二晶体管的阈值电压为vth,s点的电位充电至vs=vdatah-vth;

13、在所述侦测阶段,所述第一扫描信号为高电位,所述第四晶体管打开,所述第一开关关闭,所述第一数据信号不输入,所述第二开关打开,以使所述芯片读取s点的电位,并获取第二晶体管的阈值电压vth。

14、可选的,在本技术的一些实施例中,当所述vth>0时,所述内部补偿模块采用第一时序补偿所述阈值电压,所述第一时序的工作阶段包括第一复位阶段、写入与补偿阶段和第一发光阶段;

15、在所述第一复位阶段,所述第三扫描信号、所述第四扫描信号为高电位,所述第七晶体管、所述第九晶体管打开,g点写入电源高电频信号vdd,所述第二扫描信号为高电位,所述第六晶体管打开,所述第二电容与所述第六晶体管的第一极连接的a点写入复位信号vi,此时,g点的电位vg=vdd,a点的电位va=vi;

16、在所述写入与补偿阶段,所述第一发光信号、所述第一扫描信号、所述第二扫描信号、所述第四扫描信号、所述第五扫描信号为高电位,所述第一开关、所述第一晶体管、所述第二晶体管、所述第四晶体管、所述第五晶体管、所述第六晶体管、所述第七晶体管均打开,此时,s点写入第一数据信号的高电位vdatah’,此时,g点的电位为s点电位与第二晶体管的阈值电压之和,此时a点电位保持为vi;

17、在第一发光阶段,所述第一发光信号、所述第二发光信号、所述第二数据信号、所述第五扫描信号为高电位,所述第一晶体管、所述第二晶体管、所述第三晶体管打开,a点的电位va等于所述发光单元的电压vf,led、所述电源低电频信号vss以及连接a点与发光单元的走线的电压vir(vss)之和,所述第四扫描信号为高电位,所述第七晶体管打开,g点的电位被a点的电位通过所述第二电容升高,此时,g点电位为vg=vdatah’+vth-vinit+vf,led+vss+vir(vss),s点的电位vs等于所述发光单元的电压vf,led、第三晶体管的分压vt3、电源低电频信号的电压vss以及连接s点与发光单元的走线的电压vir(vss)’之和。

18、可选的,在本技术的一些实施例中,当vth<0时,所述内部补偿模块采用第二时序补偿所述阈值电压,所述第二时序的工作阶段包括第二复位阶段、提取与存储阶段、数据写入阶段、第二发光阶段;

19、在所述第二复位阶段,所述第一扫描信号、所述第五扫描信号为高电位,所述第一开关打开,所述第四晶体管打开,所述第一数据信号将vneg信号写入s点的电位,所述第八晶体管打开,所述第二数据信号将vpre信号写入g点的电位,以初始化g点、s点的电位,其中,vg=vpre,vs=vneg;

20、在所述提取与存储阶段,所述第一扫描信号、所述第四扫描信号、所述第五扫描信号、所述第二数据信号为高电位,所述第二晶体管、所述第五晶体管、第七晶体管打开,s点的电位充电至vs=vpre-vth之后,所述第二晶体管关闭,s点停止充电,s点的电位保持为vs=vpre-vth;

21、在所述数据写入阶段,所述第二数据信号输入高电位vdata2,所述第五扫描信号为高电位,所述第八晶体管打开,g点的电位为vdata2,打开第二晶体管,g点通过所述第三电容的耦合使s点的电位升高,此时,s点的电位vs=(vpre-vth)+(vdata2-vpre)*c3/(c1+c3),g点与s点的电位差vgs=(vdata2-vpre)*c1/(c1+c3)+vth,其中,c1为所述第一电容的电容值,c3为所述第三电容的电容值;

22、在所述第二发光阶段,g点与s点电位保持,所述第一发光信号、所述第二发光信号、所述第二数据信号、所述第五扫描信号为高电位,所述第一晶体管、所述第二晶体管、所述第三晶体管打开,使所述发光单元发光。

23、本技术实施例提供一种显示面板,包括上述任一实施例所述的像素驱动电路。

24、有益效果:通过提供一种包括外部侦测模块和内部补偿模块的像素驱动电路,通过外部侦测模块侦测开机时阈值电压的偏移方向,当所述阈值电压的偏移方向为正偏时,所述内部补偿模块被配置为采用第一时序补偿阈值电压;当所述阈值电压的偏移方向为负偏时,所述内部补偿模块被配置为采用第二时序补偿阈值电压;通过不同时序的内部补偿实现更准确和更大补偿范围的内部实时补偿,缓解了现有像素驱动电路存在无法兼顾实时补偿与较大补偿范围的技术问题。

本文地址:https://www.jishuxx.com/zhuanli/20240618/33557.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表