显示屏的像素电路的制作方法

- 国知局

- 2024-06-21 13:43:03

本发明涉及一种显示屏的像素电路,尤其涉及一种可消除临界电压偏移的显示屏的像素电路结构。

背景技术:

1、在各种次世代显示技术中,微型有机发光二极管(micro organic lightemitting diode,micro-oled)面板的重要性近年来逐渐提升。有别于传统发光二极管或有机发光二极管面板其屏幕构建在玻璃基板上的方式,微型有机发光二极管面板的屏幕是直接贴装在硅晶圆上,这种硅基(silicon-based)实施方式可实现大量好处,如体积小、重量轻、功耗低、发光效率高、对比度高、像素密度高等。凭借以上优势,微型有机发光二极管面板特别适用于扩增实境(augmented reality,ar)和虚拟实境(virtual reality,vr)的应用。

2、然而,在硅基实施方式中,用来控制像素中驱动晶体管的数据电压落在大约200mv~300mv的操作范围,远小于相同像素结构下基于薄膜晶体管(thin-film transistorbased,tft-based)的数据电压的操作范围,这是因为硅基实施方式中晶体管的组件迁移率(mobility)较高,意即用来产生相同驱动电流所需的电压摆荡范围变得较小。较小的电压摆荡范围需要更细的分辨率来实现相同的灰度及伽玛等级,其伴随的是较高的设计困难度和电路成本。举例来说,在256灰度的应用中,若操作电压范围在200mv及300mv之间,表示每一灰度的步阶电压约为1mv,其容易因为不理想的灰度与电压对应关系而产生数据电压上的误差。鉴于此,现有技术实有改进的必要。

技术实现思路

1、因此,本发明的主要目的即在于提出一种用于有机发光二极管(organic lightemitting diode,oled)面板(特别是微型有机发光二极管(micro-oled)面板)的新式像素电路,以解决上述问题。

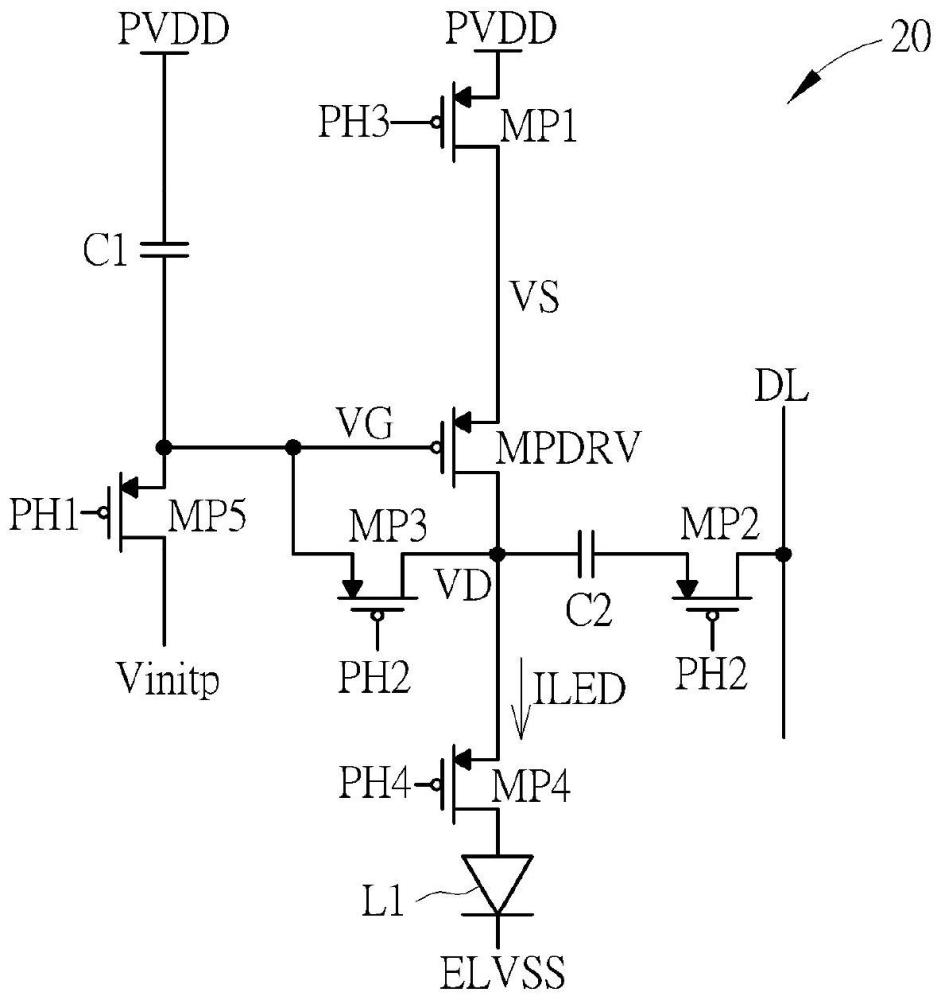

2、本发明的一实施例公开了一种显示屏的像素电路,其包括一驱动晶体管、一第一电容、一第二电容、一第一晶体管、一第二晶体管、一第三晶体管、一第四晶体管、一第五晶体管及一发光组件。该驱动晶体管包括一第一端、一第二端及一栅极端。该第一电容耦接于该驱动晶体管的该栅极端。该第二电容连接于该驱动晶体管的该第一端。该第一晶体管耦接于该驱动晶体管的该第二端。该第二晶体管耦接于该第二电容。该第三晶体管耦接于该驱动晶体管的该第一端及该驱动晶体管的该栅极端之间。该第四晶体管耦接于该驱动晶体管的该第一端。该第五晶体管耦接于该驱动晶体管。该发光组件耦接于该第四晶体管。

3、本发明的另一实施例公开了一种显示屏的像素电路,其包括一驱动晶体管、一第一电容、一第二电容、一第一晶体管、一第二晶体管、一第三晶体管、一第四晶体管、一第五晶体管及一发光组件。该驱动晶体管包括一第一端、一第二端及一栅极端。该第一电容耦接于该驱动晶体管的该栅极端。该第二电容连接于该驱动晶体管的该第一端。该第一晶体管耦接于该驱动晶体管的该第一端。该第二晶体管耦接于该第二电容。该第三晶体管耦接于该驱动晶体管的该第一端及该驱动晶体管的该栅极端之间。该第四晶体管耦接于该驱动晶体管的该第二端。该第五晶体管耦接于该第一电容及该第四晶体管。该发光组件耦接于该第四晶体管。

技术特征:1.一种显示屏的像素电路,其特征在于,包括:

2.如权利要求1所述的像素电路,其特征在于,该第二晶体管还耦接至一数据线,以接收一显示数据。

3.如权利要求2所述的像素电路,其特征在于,该显示数据通过该第二电容耦合至该驱动晶体管。

4.如权利要求2所述的像素电路,其特征在于,该显示数据是以根据该第一电容及该第二电容所决定的一比例耦合至该驱动晶体管。

5.如权利要求1所述的像素电路,其特征在于,该第二电容包括:

6.如权利要求1所述的像素电路,其特征在于,该第一电容包括:

7.如权利要求1所述的像素电路,其特征在于,该第五晶体管耦接于该驱动晶体管的该栅极端,以传送一初始电压至该驱动晶体管。

8.如权利要求1所述的像素电路,其特征在于,该第五晶体管耦接于该驱动晶体管的该第一端,以传送一初始电压至该驱动晶体管。

9.如权利要求1所述的像素电路,其特征在于,该第一晶体管还耦接至一电源供应端,以接收一电源供应电压。

10.如权利要求1所述的像素电路,其特征在于,该驱动晶体管的该第一端为该驱动晶体管的一漏极端,且该驱动晶体管的该第二端为该驱动晶体管的一源极端。

11.如权利要求1所述的像素电路,其特征在于,在一初始阶段中,该第二晶体管、该第三晶体管及该第五晶体管导通,且该第一晶体管及该第四晶体管断开。

12.如权利要求11所述的像素电路,其特征在于,一初始电压是在该初始阶段中通过该第五晶体管输入该像素电路。

13.如权利要求1所述的像素电路,其特征在于,在一补偿阶段中,该第一晶体管、该第二晶体管及该第三晶体管导通,且该第四晶体管及该第五晶体管断开。

14.如权利要求13所述的像素电路,其特征在于,一补偿信息是在该补偿阶段中写入该第一电容及该第二电容当中至少一者。

15.如权利要求1所述的像素电路,其特征在于,在一扫描阶段中,该第二晶体管及该第三晶体管导通,且该第一晶体管、该第四晶体管及该第五晶体管断开。

16.如权利要求15所述的像素电路,其特征在于,一显示数据是在该扫描阶段中通过该第二晶体管输入该像素电路。

17.如权利要求1所述的像素电路,其特征在于,在一发光阶段中,该第一晶体管及该第四晶体管导通,且该第二晶体管、该第三晶体管及该第五晶体管断开。

18.如权利要求17所述的像素电路,其特征在于,该第四晶体管将一驱动电流从该驱动晶体管传送至该发光组件,以控制该发光组件在该发光阶段中进行发光。

19.一种显示屏的像素电路,其特征在于,包括:

20.如权利要求19所述的像素电路,其特征在于,该第二晶体管还耦接至一数据线,以接收一显示数据。

21.如权利要求20所述的像素电路,其特征在于,该显示数据通过该第二电容耦合至该驱动晶体管。

22.如权利要求20所述的像素电路,其特征在于,该显示数据是以根据该第一电容及该第二电容所决定的一比例耦合至该驱动晶体管。

23.如权利要求19所述的像素电路,其特征在于,该第二电容包括:

24.如权利要求19所述的像素电路,其特征在于,该第一电容包括:

25.如权利要求19所述的像素电路,其特征在于,该第五晶体管传送一初始电压至该发光组件。

26.如权利要求19所述的像素电路,其特征在于,该第一晶体管还耦接至一电源供应端,以接收一电源供应电压。

27.如权利要求19所述的像素电路,其特征在于,该驱动晶体管的该第一端为该驱动晶体管的一漏极端,且该驱动晶体管的该第二端为该驱动晶体管的一源极端。

28.如权利要求19所述的像素电路,其特征在于,在一初始阶段中,该第一晶体管、该第二晶体管、该第三晶体管及该第五晶体管导通,且该第四晶体管断开。

29.如权利要求28所述的像素电路,其特征在于,一初始电压是在该初始阶段中通过该第五晶体管输入该像素电路。

30.如权利要求19所述的像素电路,其特征在于,在一补偿阶段中,该第二晶体管、该第三晶体管、该第四晶体管及该第五晶体管导通,且该第一晶体管断开。

31.如权利要求30所述的像素电路,其特征在于,一补偿信息是在该补偿阶段中写入该第一电容及该第二电容当中至少一者。

32.如权利要求19所述的像素电路,其特征在于,在一扫描阶段中,该第二晶体管、该第三晶体管及该第五晶体管导通,且该第一晶体管及该第四晶体管断开。

33.如权利要求32所述的像素电路,其特征在于,一显示数据是在该扫描阶段中通过该第二晶体管输入该像素电路。

34.如权利要求19所述的像素电路,其特征在于,在一发光阶段中,该第一晶体管及该第四晶体管导通,且该第二晶体管、该第三晶体管及该第五晶体管断开。

35.如权利要求34所述的像素电路,其特征在于,该第四晶体管将一驱动电流从该驱动晶体管传送至该发光组件,以控制该发光组件在该发光阶段中进行发光。

技术总结本发明公开了一种显示屏的像素电路,包括一驱动晶体管、一第一电容、一第二电容、一第一晶体管、一第二晶体管、一第三晶体管、一第四晶体管、一第五晶体管及一发光组件。该驱动晶体管包括一第一端、一第二端及一栅极端。该第一电容耦接于该驱动晶体管的栅极端。该第二电容连接于该驱动晶体管的第一端。该第一晶体管耦接于该驱动晶体管的第二端。该第二晶体管耦接于该第二电容。该第三晶体管耦接于该驱动晶体管的第一端及栅极端之间。该第四晶体管耦接于该驱动晶体管的第一端。该第五晶体管耦接于该驱动晶体管。该发光组件耦接于该第四晶体管。技术研发人员:萧圣文受保护的技术使用者:联咏科技股份有限公司技术研发日:技术公布日:2024/5/12本文地址:https://www.jishuxx.com/zhuanli/20240618/34139.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表