一种具备自动复位机制的多级时间数字转换器

- 国知局

- 2024-07-30 09:36:11

1.本发明涉及时间数字转换器技术领域,具体为一种具备自动复位机制的多级时间数字转换器。背景技术:2.时间数字转换器(time-to-digital converter,tdc)可以将一个或多个触发事件之间的时间间隔转化为数字信号,以方便进行量化处理,其已经被广泛应用于高能物理实验、生物医学成像以及3d成像中的激光测距等科研和工业生产领域。3.文献[1](markovic b,tisa s,villa f a,et al.a high-linearity,17ps precision time-to-digital converter based on a single-stage vernier delay loop fine interpolation[j].ieee transactions on circuits and systems i:regular papers)提出的基于延迟锁相环的多级量化结构是目前比较流行的一种时间数字转换器的实现方式,可以在得到较高的时间分辨率的同时,还能实现较大的动态范围。然而,此类方式所采用的复位方式只能对宽度较大的触发信号进行连续地测量,必须要提出一种新的复位机制,来满足tdc对各种宽度信号的测量需求。技术实现要素:[0004]本发明针对现有方案存在的问题,提供了一种具备自动复位机制的多级时间数字转换器,具体包括:依次级联的第一级量化结构、第二级量化结构和第三级量化结构。[0005]所述第一级量化结构包括:一个n位二进制计数器。[0006]所述第二级量化结构包括:并行的多相时钟插值采样电路和同步电路。[0007]所述第三级量化结构包括:加入自动复位电路的游标延迟环。[0008]所述加入自动复位电路的游标延迟环包括:[0009]第一输入上升沿检测电路和第二输入上升沿检测电路,第一输入上升沿检测电路的输入端与外部触发信号asyn相连,第二输入上升沿检测电路的输入端与外部触发信号到来之后的第一个多相时钟信号syn相连,第一输入上升沿检测电路和第二输入上升沿检测电路的输出端均与异或门的一个输入端相连。[0010]第一脉冲展宽电路和第二脉冲展宽电路,第一脉冲展宽电路的输入端与和第一输入上升沿检测电路连接的异或门的输出端相连,第二脉冲展宽电路的输入端与和第二输入上升沿检测电路连接的异或门的输出端相连。[0011]自动复位电路,其输入端分别与第一脉冲展宽电路和第二脉冲展宽电路的输出端相连。[0012]进一步的,所述第一输入上升沿检测电路和第二输入上升沿检测电路均包括:[0013]第一反相器,其输入端即为对应的输入上升沿检测电路的输入端。[0014]第一与门,其一个输入端与第一反相器的输出端相连,其另一个输入端与对应的输入上升沿检测电路的输入信号相连,其输出端即为对应的输入上升沿检测电路的输出端。[0015]进一步的,所述第一脉冲展宽电路和第二脉冲展宽电路均包括:[0016]sr锁存器,其r端即为对应的脉冲展宽电路的输入端,其s端通过两个延迟为τ2的延迟单元与对应的脉冲展宽电路的输入信号相连,其q端即为对应的脉冲展宽电路的输出端。[0017]进一步的,所述自动复位电路包括:[0018]d触发器,其clk端与第一脉冲展宽电路的输出端相连,其d端与第二脉冲展宽电路的输出端相连,其d端还与第一缓冲器相连。[0019]多路选择器,其i0端与全局复位信号reset相连,其i1端通过第二反相器与d触发器的q端相连,其i1端还与第一脉冲展宽电路内的sr锁存器的reset端和第二脉冲展宽电路内的sr锁存器的reset端同时相连,其s端通过一个延迟为τ2的延迟单元与全局复位信号reset相连。[0020]d触发器的复位端通过两个延迟为τ2的延迟单元与多路选择器m的输出端相连。[0021]进一步的,所述加入自动复位电路的游标延迟环还包括:[0022]第二与门,其一个输入端与全局复位信号reset相连,其另一个输入端通过四个延迟为τ2的延迟单元与第一脉冲展宽电路内的sr锁存器的q端相连,其输出端与和第一输入上升沿检测电路连接的异或门的另一个输入端相连。[0023]第三与门,其一个输入端与全局复位信号reset相连,其另一个输入端通过一个延迟为τ1和三个延迟为τ2的延迟单元与第二脉冲展宽电路内的sr锁存器的q端相连,其输出端与和第二输入上升沿检测电路连接的异或门的另一个输入端相连。[0024]脉冲计数器,其输入端通过第二缓冲器与d触发器的clk端相连,其复位端与全局复位信号reset相连,其输出端为加入自动复位电路的游标延迟环的输出端。[0025]进一步的,所述第一级量化结构中的n位二进制计数器利用寄存器组对数据进行自动复位。[0026]进一步的,所述第二级量化结构中的多相时钟插值采样电路利用寄存器组对数据进行自动复位。[0027]与现有技术相比,本发明提供了一种具备自动复位机制的多级时间数字转换器,其有益效果是:[0028]本发明针对现有的基于延迟锁相环的多级量化结构进行了改进,加入了一种自动复位机制,使其对不同宽度的、连续到来的外部触发信号都能正确地完成量化;本发明提出的具有自动复位机制的时间量化结构不仅保证了较好的分辨率、线性度等性能指标,还增加了对连续脉冲到达时间的进行测量的功能,适合应用于辐射探测器前端读出系统等各种时间测量领域。附图说明[0029]图1为文献[1]提出的多级时间数字转换器的结构图;[0030]图2为文献[1]提出的多级时间数字转换器的时间测量时序图;[0031]图3为文献[1]采用的传统游标延迟环的结构图;[0032]图4为文献[1]采用的传统游标延迟环的关键节点时序图;[0033]图5为本发明提出的加入自动复位机制的游标延迟环结构示意图;[0034]图6为本发明提出的自动复位电路的关键节点示意图;[0035]图7为本发明提出的具有自动复位机制的游标延迟环关键节点时序图;[0036]图8为本发明提出的具有连续时间测量功能的计数器时序图;[0037]图9为本发明提出的具有连续测量功能的多级tdc的第二级量化电路结构图;[0038]图10为本发明提出的具有连续测量功能的多级tdc的第二级量化电路测量时序图;[0039]图11为本发明提出的具有自动复位机制的游标延迟环测量时序图。具体实施方式[0040]下面结合附图1至图11,对本发明的具体实施方式作进一步描述。以下实施例仅用于更加清楚地说明本发明的技术方案,而不能以此来限制本发明的保护范围。[0041]实施例1:本发明提供的一种具备自动复位机制的多级时间数字转换器,具体包括:依次级联的第一级量化结构、第二级量化结构和第三级量化结构。[0042]所述第一级量化结构包括:一个n位二进制计数器。[0043]所述第二级量化结构包括:并行的多相时钟插值采样电路和同步电路。[0044]所述第三级量化结构包括:加入自动复位电路的游标延迟环。[0045]所述加入自动复位电路的游标延迟环包括:[0046]第一输入上升沿检测电路和第二输入上升沿检测电路,第一输入上升沿检测电路的输入端与外部触发信号asyn相连,第二输入上升沿检测电路的输入端与外部触发信号到来之后的第一个多相时钟信号syn相连,第一输入上升沿检测电路和第二输入上升沿检测电路的输出端均与异或门的一个输入端相连。[0047]第一脉冲展宽电路和第二脉冲展宽电路,第一脉冲展宽电路的输入端与和第一输入上升沿检测电路连接的异或门的输出端相连,第二脉冲展宽电路的输入端与和第二输入上升沿检测电路连接的异或门的输出端相连。[0048]自动复位电路,其输入端分别与第一脉冲展宽电路和第二脉冲展宽电路的输出端相连。[0049]进一步的,所述第一输入上升沿检测电路和第二输入上升沿检测电路均包括:[0050]第一反相器,其输入端即为对应的输入上升沿检测电路的输入端。[0051]第一与门,其一个输入端与第一反相器的输出端相连,其另一个输入端与对应的输入上升沿检测电路的输入信号相连,其输出端即为对应的输入上升沿检测电路的输出端。[0052]进一步的,所述第一脉冲展宽电路和第二脉冲展宽电路均包括:[0053]sr锁存器,其r端即为对应的脉冲展宽电路的输入端,其s端通过两个延迟为τ2的延迟单元与对应的脉冲展宽电路的输入信号相连,其q端即为对应的脉冲展宽电路的输出端。[0054]进一步的,所述自动复位电路包括:[0055]d触发器,其clk端与第一脉冲展宽电路的输出端相连,其d端与第二脉冲展宽电路的输出端相连,其d端还与第一缓冲器相连。[0056]多路选择器,其i0端与全局复位信号reset相连,其i1端通过第二反相器与d触发器的q端相连,其i1端还与第一脉冲展宽电路内的sr锁存器的reset端和第二脉冲展宽电路内的sr锁存器的reset端同时相连,其s端通过一个延迟为τ2的延迟单元与全局复位信号reset相连。[0057]d触发器的复位端通过两个延迟为τ2的延迟单元与多路选择器m的输出端相连。[0058]进一步的,所述加入自动复位电路的游标延迟环还包括:[0059]第二与门,其一个输入端与全局复位信号reset相连,其另一个输入端通过四个延迟为τ2的延迟单元与第一脉冲展宽电路内的sr锁存器的q端相连,其输出端与和第一输入上升沿检测电路连接的异或门的另一个输入端相连。[0060]第三与门,其一个输入端与全局复位信号reset相连,其另一个输入端通过一个延迟为τ1和三个延迟为τ2的延迟单元与第二脉冲展宽电路内的sr锁存器的q端相连,其输出端与和第二输入上升沿检测电路连接的异或门的另一个输入端相连。[0061]脉冲计数器,其输入端通过第二缓冲器与d触发器的clk端相连,其复位端与全局复位信号reset相连,其输出端为加入自动复位电路的游标延迟环的输出端。[0062]进一步的,所述第一级量化结构中的n位二进制计数器利用寄存器组对数据进行自动复位。[0063]所述第二级量化结构中的多相时钟插值采样电路利用寄存器组对数据进行自动复位。[0064]文献[1]提出的基于延迟锁相环的多级量化结构,是目前比较流行的一种时间数字转换器的实现方式,在得到较高的时间分辨率的同时,还能实现较大的动态范围。该结构的时间量化机制共分为三级:第一级量化结构为一个二进制计数器,它计算有效窗口内的时钟周期数量来得到量化结果;第二级量化结构为多相时钟插值器,它利用延迟锁相环产生的多相时钟对第一级量化的剩余时间进行测量;第三级量化结构为游标延迟环,它利用不同延迟锁相环的单位延迟之差对第二级量化的剩余时间进行测量。该多级时间数字转换器的结构如附图1所示,量化时序如附图2所示。[0065]总体的量化结果可以表示为:[0066]tin=tcont+tstart-tstop[0067]=ntclk+(tc1-tc2)+(tf1-tf2)+(te31-te32)[0068]其中,n代表第一级量化的计数器的输出值,tclk代表参考时钟的周期,tc1、tc2分别代表start和stop通道第二级量化的结果,tf1、tf2分别代表start和stop通道第三级量化的结果,te31、te32分别代表start和stop通道的量化误差。[0069]该多级tdc主要组成模块有计数器、多相时钟插值器、同步电路、游标延迟环以及延迟锁相环。tdc的动态范围由第一级的计数器决定,最高分辨率则由第三级的游标延迟环的bin size决定。延迟锁相环1为第二级量化的多相时钟插值器提供分布均匀、低抖动的多相时钟;延迟锁相环1和延迟锁相环2分别产生的控制电压vc1和vc2传送到游标延迟环中,用来实现小于门延迟的分辨率,同时也可以减轻pvt等非理想因素造成的延迟单元的延迟不均匀问题。[0070]该结构的第三级细量化部分采用游标延迟环来得到较高的时间分辨率,该测量方法是通过建立两种不同的传输路径,将输入延迟不断地缩短并采样来实现的。tdc中使用了两个延迟锁相环,二者的延迟链长度不同,因此能产生的多相时钟数和单个延迟单元的延迟大小也就不同,其中延迟锁相环1能产生16相时钟而延迟锁相环2中只有15相时钟。因此,延迟锁相环1提供的单位延迟τ1=tclk/16,延迟锁相环2提供的单位延迟τ2=tclk/15。该游标延迟环就是利用了这两种不同的单位延迟τ1、τ2来实现的。游标延迟环作为第三级时间量化结构,其测量时间是第二级量化的剩余时间,即第二级量化误差,其结构如附图3所示。输入信号asyn代表外部触发信号,syn代表触发之后的第一个多相时钟,两个信号之间的延迟tf就代表游标延迟环的测量时间。但是由于上面环路的信号传输路径延迟比下面环路的大τ2-τ1,每当两个环路完成一次循环,a1和a2两个节点之间的延迟减少τ2-τ1;假设a1和a2之间的初始延迟tf大于(n-1)*(τ2-τ1)且小于n*(τ2-τ1),当完成n次循环后,a1和a2所连接的d触发器输出一个复位电平,将上下环路中的sr触发器复位,此时游标延迟环的量化过程结束。循环次数n即为游标延迟环的量化结果,可以通过一个脉冲计数器得到n的数值;(τ2-τ1)即为游标延迟环的测量分辨率。[0071]游标延迟环主要节点的工作时序如附图4所示。可以观察到asyn和syn信号的上升沿之间存在大小为tf的延迟,而a1节点信号的变化周期(即上环路的路径延迟)为6τ2,而a2节点信号的变化周期(即下环路的路径延迟)为5τ2+τ1。这样若干次循环,两节点信号的上升沿重合或a2上升沿超过a1上升沿时,d触发器采样到高电平,经过反相器产生b节点的低电平,从而上下两个环路中的sr触发器复位,循环结束。正确的复位操作是游标延迟环的循环过程能够成功运行的关键,图3所示结构中有两个复位信号,其中reset代表全局复位信号,rstn代表内部复位信号。整个tdc系统开始运行之前,reset信号先拉到低电平再拉到高电平,完成全局复位操作。rstn在游标延迟环每次开始量化之前需要保持一段时间的低电平,将d触发器输出清零,从而将b节点的电平拉高,打开两个环路中的sr触发器;从触发信号开始后直到量化过程结束前,rstn必须保持高电平,这样才能检测到a2上升沿对齐或者超过a1上升沿(d触发器输出高电平)。[0072]在传统的游标延迟环中rstn信号是由外部提供的,一般是由全局复位信号reset将rstn拉低以对内部节点进行初始化,在触发信号asyn上升沿到来之后立刻将rstn拉高,由于asyn信号到达a1节点的路径延迟较大(约为2τ1),可以保证sr触发器开始工作时rstn已经变为高电平,可以开始循环;当asyn下降沿到来后将rstn拉低,对d触发器进行复位以保证下一次量化可以正常进行。当asyn的下一个上升沿和下降沿到来时,rstn也是像上面描述的情形一样变化,从而游标延迟环的量化可以不断地进行下去。然而,每次量化过程中游标延迟环都要完成若干次循环,死区时间最大为60ns,对于高电平保持时间较短(小于60ns)的asyn信号,rstn可能在循环结束之前就被asyn的下降沿拉高,循环结束之后被拉低,之后一直保持低电平,这样就无法进行下一次量化。因此,采用这种复位方式的游标延迟环只能对宽度较大的触发信号进行连续地测量,必须要提出一种新的复位机制,来满足tdc对各种宽度信号的测量需求。[0073]本发明提出的具有自动复位机制的时间数字转换器具有三级量化结构,第一级的计数器和第二级的多相时钟插值采样电路可以利用寄存器组对数据进行自动复位,重点对第三级游标延迟环的复位机制进行说明。该游标延迟环与附图3所示的传统结构具有类似功能和原理,都是用作多级tdc的第三级细量化部分,对tdc第二级量化部分的剩余时间进行测量。其输入信号asyn对应外部触发信号,输入信号syn对应触发信号到来之后的第一个多相时钟(由第二级量化采集到),reset代表全局复位信号。正常情况下asyn信号的上升沿比syn信号的上升沿靠前,所以将asyn信号输入到延迟较大的环路中,将syn信号输入到延迟较小的环路中,两个环路的延迟差为τ2-τ1。经过若干次循环后,a2节点信号的上升沿对齐或者超前于a1节点信号的上升沿,触发自动复位电路产生复位信号,结束循环并将电路自动恢复到可进行下一次测量的过程。该游标延迟环在一次测量过程中的循环次数就代表测量结果,两个环路的延迟差τ2-τ1代表测量分辨率。[0074]附图5所示为改进后的游标延迟环结构图,其具有上下两个几乎完全对称的环路结构,图中标注的第1部分由一个反相器和一个二输入与门组成,可以将输入信号asyn(或syn)的上升沿转化为一个较窄的脉冲,其宽度为一个反相器的传播延迟。第1部分后面连接的是二输入异或门,其输入端之一连接的是后面的与门的输出p1(或p2),而该与门的一端输入连接的是全局复位信号(在电路正常工作时保持高电平,因此p1节点信号与s1节点信号保持一致。这样,第一部分产生的窄脉冲就能顺利地传送到第2部分。第2部分由两个延迟单元和一个带异步复位端的sr锁存器构成,可以将第1部分产生的窄脉冲转化为高电平持续时间为2τ2(τ2为延迟单元的延迟大小)的脉冲信号。第2部分后面连接的四个延迟单元是为了将脉冲信号的周期控制为其高电平持续时间的两倍,以保证循环能够正常进行;为了实现游标测量,上面环路放置了4个延迟为τ2的延迟单元,下面环路的则是3个延迟为τ2的延迟单元和1个延迟为τ1的延迟单元。第2部分的输出同时还连接到本文提出的自动复位电路(第3部分),主要由1个带异步复位端的d触发器、1个多路选择器(2输入)、3个延迟为τ2的压控延迟单元和1个反相器构成;其功能是实现游标延迟环电路测量结束后的自动复位,详细的工作原理会在下面进行说明。上下环路中的第2部分电路的输出端都添加了缓冲器进行负载匹配和驱动能力的增强,其中一端连接到脉冲计数器,通过统计所产生脉冲的数目来得到循环的次数,此即为游标延迟环的数字输出。[0075]本发明提出的具有自动复位机制的游标延迟环相比于传统结构具有较强的连续测量能力,在每次测量结束后由结束标志信号自动将电路复位,无需外部干预。自动复位电路的各关键节点如附图6所示。改进后游标延迟环的工作过程共分为两个阶段,第一阶段为从全局复位有效开始到触发信号到来之前(即t1时刻之前,如图7所示),第二阶段为触发信号到来之后(即t1时刻之后)。第一阶段电路的工作过程为:全局复位信号reset连接到多路选择器的i0输入端,其首先为低电平,结束复位后变为高电平;c为reset经过τ2延迟之后的信号,连接到多路选择器的选择控制端,其初始为低电平将多路选择器的i0路径打开,随后又变为高电平将i1路径打开,之后就一直保持高电平;因此多路选择器的输出点d在初始时呈现图7所示的电平变化;rstn为d经过2τ2延迟之后的信号,其初始时的低电平将d触发器的输出节点清零(b点为高电平),随后在触发信号到来之前变为高电平,游标延迟环可以正常工作。第二阶段电路的工作过程为:触发信号到来之后,游标延迟环开始进行时间量化,当a1点信号的上升沿对齐或超前于a2点信号的上升沿时,量化过程结束,d触发器采样到高电平,将b点信号拉低;由于多路选择器的i1路径一直打开,d点信号被拉低,rstn在经过2τ2的延迟之后也被拉低,将d触发器复位,b、d、rstn信号依次被变为高电平,这样就完成了游标延迟环一次量化过程结束之后的复位操作,并自动跳转到可以进行下一次量化的状态。[0076]本发明提出的具有自动复位机制的时间数字转换器具有三级量化结构,具体实施过程为:[0077]第一级量化结构由一个n位的二进制计数器实现,如附图1所示,计数器在全局复位之后开始在参考时钟频率下进行工作,当每个触发信号(start或stop)的上升沿到来时,取出当前计数器的数据,并存放到该触发所在通道的一组寄存器中。图8为该计数器的工作时序图,其中data代表计数器的计数值,start_reg和stop_reg分别代表触发信号start和stop对应的寄存器中存放的数据。可以看到这种计数方式能够满足连续时间测量的需求。[0078]第二级量化结构由多相时钟插值采样电路和同步电路构成,如附图9所示,该结构测量触发信号hit上升沿和参考时钟上升沿之间的时间间隔,得到的n位独热码经过编码器转换为m位的二进制码,并且可以将hit和其后第一个多相时钟经过同步电路提取出来,输出到下一级中继续进行更高精度的量化,其中hit对应的是asyn,提取到的多相时钟对应的是syn。第二级量化的时序如附图10所示,这种测量结构的输出数据在每次触发信号到来时更新一次,可以对连续触发信号进行测量。[0079]第三级量化结构由附图5所示的具有自动复位机制的游标延迟环构成,该结构的测量过程时序如附图11所示,其中out为脉冲计数器的直接输出值,out_reg为脉冲计数器连接的寄存器的输出值。每次量化完成后,rstn信号被拉低,经过2τ2的延迟后由自动复位电路将rstn拉高。由于在rstn上升沿的时刻,脉冲计数器已经完成测量并保持稳定的输出,所以每当rstn上升沿到来时更新out_reg。rstn上升沿也可以作为多级tdc的整体数据采样信号,触发数据处理电路将三级量化的结果整理打包,存入片内存储结构或发送到片外。[0080]以上所述实施例仅为本发明较佳的具体实施方式,本发明的保护范围不限于此,任何熟悉本领域的技术人员在本发明披露的技术范围内,可显而易见地得到的技术方案的简单变化或等效替换,均属于本发明的保护范围。

本文地址:https://www.jishuxx.com/zhuanli/20240730/150142.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

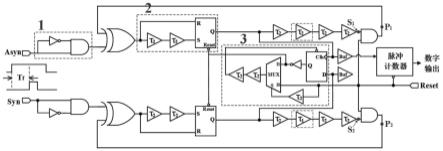

返回列表