一种两步多相时钟时间数字转换器的校正电路及校正方法

- 国知局

- 2024-07-30 10:22:13

本发明涉及时间数字转换,尤其涉及一种两步多相时钟时间数字转换器的校正电路及校正方法。

背景技术:

1、时间数字转换器(time-to-digital converter,tdc)是一种高精度的时间测量模块,时间信号通常通过时钟信号进行测量。两步多相时钟时间数字转换器是将测量时间信号t划分成两个不同步骤,通过两个粗细量化之间转换数据的衔接产生最后的数字信号。

2、请参阅图1所示,z_cnt信号表示到达粗量化模块的时间信号t,z_mod信号表示到达细量化模块的时间信号t,理想情况下z_cnt的下降沿和z_mod的上升沿重合,z_c nt的上升沿和z_mod的下降沿重合;将主时钟clk<0>分成2q等份,clk<0:2q-1>用于细量化模块,clk<2q-3>、clk<2q-2>、clk<3*2q-3>和clk<2q-1>表示滞后主时钟clk<0>45°、90°、135°和180°的时钟信号。假设第一步粗量化p bits,第二步细量化q bit s,粗细量化并行量化,粗量化计数以细量化所处时钟为准。

3、对于两步多相时钟时间数字转换器结构而言,输入信号被送入粗量化单元进行测量,同时量化误差被送入细量化单元进行精细测量。两步多相时钟时间数字转换器通过主时钟clk<0>对时间信号t计数实现粗量化,同时通过识别时间信号t翻转边沿处的clk<1:2q-1>的电平状态实现细量化。细量化的主要原理是利用不同clk之间的相位差,将原有粗量化的分辨率tclk变成tclk/2q。请参阅图2所示,在时间信号t翻转下降沿处,如果clk<1:2q-1>的电平为<000…00>,表示时间信号t翻转下降沿位于clk<0>与clk<1>之间,则细量化值0;如果clk<1:2q-1>的电平为<100…00>,表示现在时间信号t翻转下降沿位于clk<1>与clk<2>之间,则细量值为1;依次类推,如果clk<0:2q-1>的电平为<000…01>,表示现在时间信号t翻转下降沿位于clk<2q>与clk<0>之间,则细量值为2q-1。请参阅图3所示,t1为tstart端的电平识别解码后的细量化值,t2为tstop端电平识别解码后的细量化值,n*tclk为粗量化计数值,即:t=n*tclk+(tclk-t1)+(t2-tclk)=n*tclk-t1+t2。

4、两步多相时钟时间数字转换器中,d触发器扮演着重要的角色,d触发器具有记忆功能且具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元。d触发器常用于两步多相时钟时间数字转换器粗量化模块中的计数器,并在时钟信号边沿触发状态下更新。但是当d触发器处于亚稳态时,其输出状态可能会出现不稳定或无法确定的情况。亚稳态是指d触发器无法在某个规定的时间段内达到可以确认的状态,一旦d触发器进入亚稳态,则既无法预测d触发器的输出电平,也无法预测什么时候稳定在某个确认的电平上。

5、为了避免d触发器的亚稳态出现,现有技术中采用以下方法降低误码率:(1)在d触发器的输入端加入滤波电路,或者采用多级触发器来增加稳定性;(2)对粗细量化器数据同步校准解决误码问题。例如公开号为cn114265301a的专利文献公开了一种应用于两步式时间数字转换器中的数据同步校准方法,为了解决采用双计数机制工作的粗量化转换器面临的如何对粗量化值和细量化值进行同步以得到最终时间数字转换器数据的问题,该专利文献提供了通过选择器选取细量化器的n相位驱动时钟中的任意一个相位时钟的上升沿对正沿计数的第一粗计数器和负沿计数的第二粗计数器的数据结果进行锁存得到一对锁存值;然后再通过比较器对两个锁存值进行比较,比较结果返回状态机,状态机根据比较结果确定当前粗量化器和细量化器数据是否完成同步;通过控制选择器来选择下一个相位的驱动时钟作为保持模块的锁存时钟和同步器的控制信号,直到比较器返回结果为1,完成校准。

6、在时间信号t的始端和终端,由于粗细量化之间传输延时不匹配问题和d触发器的亚稳态问题,粗量化计数器的实际计数结果可能多计1或者少计1的情形。针对d触发器的亚稳态问题,上述方法在两步多相时钟时间数字转换器中不仅引入额外的滤波电路或者环形振荡器,而且不能对粗细量化引起的传输延时失配误差进行校正。针对粗细量化之间传输延时不匹配问题,在细量化中采用过量化一位的方法实现误差校正,而这种传统方法也意味着对细量化设计要求的提高,即以增加一倍的面积或者一倍的转换时间为代价。因此,如何同时解决d触发器亚稳态和传输延时不匹配引起的粗量化计数结果误差,成为亟待解决的问题。

技术实现思路

1、本发明通过提供一种两步多相时钟时间数字转换器的校正电路及校正方法,解决了现有技术中d触发器亚稳态和传输延时不匹配引起的粗量化计数结果误差问题,实现了d触发器的亚稳态误差和传输延时不匹配误差的校正。

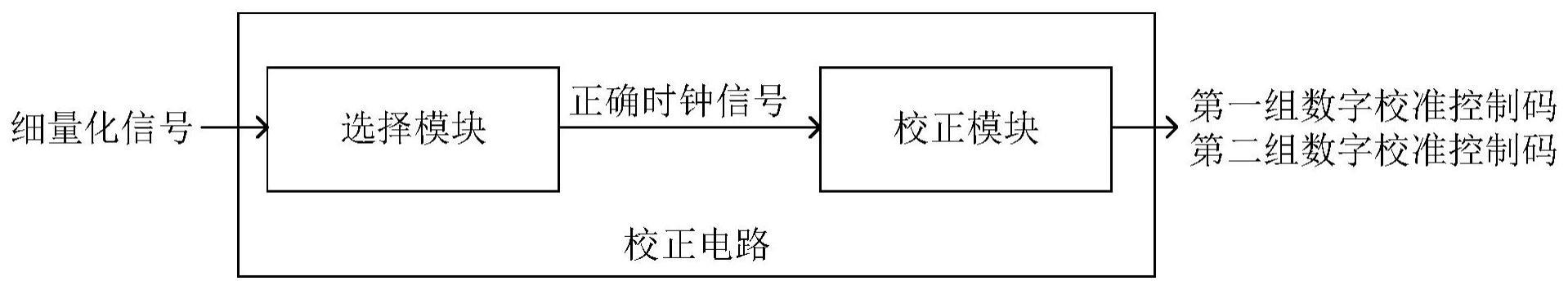

2、第一方面,本发明提供了一种两步多相时钟时间数字转换器的校正电路,包括选择模块和校正模块;

3、所述选择模块基于细量化信号翻转边沿所处的主时钟电平状态选择对应的正确时钟信号,所述选择模块将所述正确时钟信号输入所述校正模块;

4、所述校正模块接收所述正确时钟信号进行校正并产生两组数字校准控制码,以便于利用所述数字校准控制码对粗量化信号的粗量化计数值进行校正操作,其校正操作包括:保持、加一、加二、减一或减二。

5、结合第一方面,在本发明的一个实施例中,所述选择模块包括:双边沿d触发器d0、逻辑子模块sub1和传输门开关子模块sub2;

6、所述双边沿d触发器d0基于信号clk<2q-1>和所述细量化信号进行电平识别,所述细量化信号为信号z_mod;所述信号z_mod输入所述双边沿d触发器d0的时钟端,所述信号clk<2q-1>输入所述双边沿d触发器d0的数据端,所述双边沿d触发器d0的q端输出信号j并通过端输出信号j_inv,所述信号clk<2q-1>滞后主时钟180°;

7、所述逻辑子模块sub1基于所述细量化信号产生信号set1、信号set2、信号b和信号b_inv;

8、所述传输门开关子模块sub2基于所述信号clk<2q-1>、所述信号j、所述信号j_inv、所述信号b和所述信号b_inv选择正确时钟信号输入所述校正模块。

9、结合第一方面,在本发明的一个实施例中,所述逻辑子模块sub1包括:延时反相器i00、普通反相器i0、与门g1、与门g2、同或门g3和普通反相器i1;

10、所述延时反相器i00的输入端和所述同或门g3的第二个输入端连接所述信号z_mod,所述信号z_mod通过所述延时反相器i00反相处理后产生信号z_mod_delay,所述信号z_mod_delay连接所述同或门g3的第一个输入端,所述同或门g3输出信号a并连接所述普通反相器i1产生信号a_inv,所述信号a和所述信号a_inv连接所述传输门开关子模块sub2;

11、所述普通反相器i0的输入端和所述与门g2的第二个输入端连接所述信号z_mod,所述信号z_mod通过所述普通反相器i0反相处理产生信号z_mod_inv后连接所述与门g1的第二个输入端,所述与门g1的第一个输入端和所述与门g2的第一个输入端连接所述同或门g3的输出信号a,所述与门g1和所述与门g2对应输出置位信号se1、置位信号se2,所述置位信号se1和所述置位信号se2连接所述校正模块。

12、结合第一方面,在本发明的一个实施例中,所述传输门开关子模块sub2包括第一级传输门开关s11、第一级传输门开关s12、普通反相器i2、第二级传输门开关s21和第二级传输门开关s22;

13、所述第一级传输门开关s11的输入端和所述第一级传输门开关s12的输入端均连接所述信号clk<2q-2>,所述信号j和所述信号j_inv作为所述第一级传输门开关s11和所述第一级传输门开关s12的开关控制信号;所述信号clk<2q-2>滞后主时钟90°;

14、所述第一级传输门开关s12的输出端连接所述普通反相器i2的输入端,所述第一级传输门开关s11和所述普通反相器i2的公共端连接信号b,所述信号b连接所述第二级传输门开关s21的输入端;

15、所述逻辑子模块sub1输出的信号a和信号a_inv作为所述第二级传输门开关s21和所述第二级传输门开关s22的开关控制信号,所述第二级传输门开关s22的输入端连接恒定高电平信号;

16、所述第二级传输门开关s21和所述第二级传输门开关s22的公共端连接信号c,所述信号c为细量化信号边沿处电平对应的正确时钟信号,所述信号c输入所述校正模块。

17、结合第一方面,在本发明的一个实施例中,所述校正模块包括:第一触发子模块tri1、脉冲子模块sub3和第二触发子模块tri2;

18、所述第一触发子模块tri1基于所述细量化信号、所述粗量化信号、主时钟信号和所述正确时钟信号产生数字校准控制码mstart<1>和数字校准控制码mstop<1>,所述第一触发子模块tri1基于细量化时钟产生细量化信号同步信号z_mod_dtri,所述第一触发子模块tri1基于粗量化信号产生粗量化时钟同步信号z_cnt_dtr;

19、所述脉冲子模块sub3基于所述细量化时钟同步信号z_mod_dtri、所述粗量化时钟同步信号z_cnt_dtr、滞后主时钟45°的时钟信号clk<2q-3>和滞后主时钟135°的时钟信号clk<3*2q-3>产生脉冲信号l;

20、所述第二触发子模块tri2基于所述脉冲信号l、所述选择模块的双边沿d触发器d0输出的信号j、所述选择模块的逻辑子模块sub1输出的置位信号se1和置位信号se2产生两个所述数字校准控制码,两个所述数字校准控制码分别为数字校准控制码mstart<0>和数字校准控制码mstop<0>。

21、结合第一方面,在本发明的一个实施例中,所述第一触发子模块tri1包括上升沿d触发器d1、上升沿d触发器d2、双边沿d触发器d3和保持模块l1;

22、所述上升沿触发器d1的数据端接入所述细量化信号,时钟端接入所述选择模块输出的信号c,以使所述细量化信号与所述信号c进行时钟同步产生细量化时钟同步信号z_mod_dtri,所述信号c为细量化信号边沿处电平对应的正确时钟信号;

23、所述上升沿触发器d2的数据端接入所述粗量化信号,时钟端接入所述主时钟信号clk<0>,以使所述粗量化信号与所述主时钟信号clk<0>进行时钟同步产生粗量化时钟同步信号z_cnt_dtri;

24、所述双边沿触发器d3的数据端接入所述上升沿触发器d1 q端输出的所述信号z_mod_dtri,时钟端接入所述上升沿触发器d2 q端输出的信号z_cnt_dtri,以使所述细量化时钟同步信号z_mod_dtri对所述粗量化时钟同步信号z_cnt_dtri进行电平识别,所述双边沿触发器d3的端输出所述数字校准控制码mstop<1>,所述双边沿触发器d3的q端输出信号mn1;

25、所述保持模块l1连接所述双边沿触发器d3 q端输出的所述信号mn1,所述保持模块l1基于所述细量化信号及所述选择模块产生的信号z_mod_inv,输出所述数字校准控制码mstart<1>;

26、所述保持模块l1包括延时反相器i01、传输门开关s31和电容c1;

27、所述延时反相器i01的输入端连接所述双边沿触发器d3的q端,所述反相器i01的输出端通过所述传输门开关s31连接所述电容c1的正端,所述电容c1的负端接地;

28、所述传输门开关s31由所述细量化信号及所述选择模块的逻辑子模块sub1产生的信号z_mod_inv控制;

29、所述传输门开关s31和所述电容c1的公共端作为所述保持模块l1的输出端输出所述数字校准控制码mstart<1>。

30、结合第一方面,在本发明的一个实施例中,所述脉冲子模块包括同或门g4、或门g5、与门g6;

31、所述第一触发子模块tri1产生的所述细量化时钟同步信号z_mod_dtri和所述粗量化时钟同步信号z_cnt_dtri通过所述同或门g4产生信号e;

32、所述时钟信号clk<2q-3>和所述时钟信号clk<3*2q-3>通过所述或门g5产生信号f,所述时钟信号clk<2q-3>和所述时钟信号clk<3*2q-3>表示滞后主时钟信号clk<0>45°和135°;

33、所述信号e、所述信号f通过所述与门g6产生脉冲信号l,所述脉冲信号l连接所述第二触发子模块tri2。

34、结合第一方面,在本发明的一个实施例中,所述第二触发子模块tri2包括上升沿d触发器d4、上升沿d触发器d5、同或门g7、同或门g8、保持模块l2;

35、所述上升沿触发器d4的数据端接入所述上升沿触发器d4的端,所述上升沿触发器d4的时钟端接入所述脉冲子模块sub3的输出脉冲信号l,所述上升沿触发器d4的置位端接入所述选择模块输出的所述置位信号se1,以统计所述脉冲信号l在时间信号tstop端附近的脉冲个数,脉冲个数为1所述上升沿触发器d4的q端输出低电平,脉冲个数为2所述上升沿触发器d4的q端输出高电平;

36、所述上升沿触发器d5的数据端接入所述上升沿触发器d5的端,所述上升沿触发器d5的时钟端接入所述脉冲子模块sub3输出的脉冲信号l,所述上升沿触发器d5的置位端接入所述选择模块输出的所述置位信号se2,以统计所述脉冲信号l在时间信号tstart端附近的脉冲个数,脉冲个数为1所述上升沿触发器d5的q端输出低电平,脉冲个数为2所述上升沿触发器d5的q端输出高电平;

37、所述同或门g7的两个输入端分别连接所述上升沿触发器d4的q端和所述选择模块的输出信号j,所述同或门g7输出所述数字校准控制码mstop<0>;

38、所述同或门g8的两个输入端分别连接所述上升沿触发器d5的q端和所述选择模块的输出信号j,所述同或门g8输出所述数字校准控制码mn0;

39、所述保持模块l2连接所述同或门g8的输出端,基于所述细量化信号及所述选择模块产生的信号z_mod_inv,输出所述数字校准控制码mstart<0>;

40、所述保持模块l2包括延时反相器i02、传输门开关s32和电容c2;

41、所述延时反相器i02的输入端连接所述同或门g8的输出端,所述反相器i02的输出端通过所述传输门开关s32连接所述电容c2的正端,所述电容c2的负端接地;

42、所述传输门开关s32由细量化信号及所述选择模块产生的信号z_mod_inv控制;

43、所述传输门开关s32和所述电容c2的公共端作为所述保持模块l2的输出端输出所述数字校准控制码mstart<0>。

44、第二方面,本发明提供了一种两步多相时钟时间数字转换器的校正方法,包括:

45、选择模块选择信号z_mod边沿所处主时钟电平状态对应的正确时钟信号c输入校正模块;

46、校正模块接收正确时钟信号并产生两组数字校准控制码;

47、根据两组数字校准控制码对粗量化信号对应的粗量化计数结果进行对应的保持、加一、加二、减一或减二的校正操作。

48、结合第二方面,在本发明的一个实施例中,根据两组数字校准控制码对粗量化信号对应的粗量化计数结果进行保持、加一、加二、减一或减二操作,包括:

49、校正模块产生的数字校准控制码mstart<1:0>为11,对粗量化计数结果补偿加一;

50、校正模块产生的数字校准控制码mstart<1:0>为00,对粗量化计数结果补偿减一;

51、校正模块产生的数字校准控制码mstart<1:0>为10或者01,不对粗量化计数结果进行补偿;

52、校正模块产生的数字校准控制码mstop<1:0>为11,对粗量化计数结果补偿加一;

53、校正模块产生的数字校准控制码mstop<1:0>为00,对粗量化计数结果补偿减一;

54、校正模块产生的数字校准控制码mstop<1:0>为10或者01,无需对粗量化计数结果进行补偿;

55、其中,1表示高电平,0表示低电平;校正模块产生数字校准控制码mstart<1:0>和数字校准控制码mstop<1:0>解决时间信号t的tstart端和tstop端的d触发器的亚稳态误差和传输延时失配误差,数字校准控制码mstart<1:0>和数字校准控制码mstop<1:0>形成的补偿结果累加传输至粗量化模块进行保持、加一、加二、减一、减二操作。

56、本发明中提供的一个或多个技术方案,至少具有如下技术效果或优点:

57、本发明通过选择模块选择细量化器中细量化信号对应的正确时钟信号输入至校正模块,利用校正模块产生校准信号,校准信号通过逻辑模块生成的数字校准控制码对粗量化器产生的粗量化计数值进行保持、加一、加二、减一、减二操作,有效解决了现有技术中d触发器亚稳态和传输延时不匹配引起的粗量化计数结果误差问题,实现了d触发器的亚稳态误差和传输延时不匹配误差的校正。

本文地址:https://www.jishuxx.com/zhuanli/20240730/152489.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表