一种时间数字转换电路及时间数字转换方法

- 国知局

- 2024-07-30 10:22:52

本发明涉及数模混合集成电路,尤其涉及到一种时间数字转换电路及时间数字转换方法。

背景技术:

1、高性能时间数字转换器(time-to-digital converters,tdc)在所有模拟和数字锁相环、模拟数字转换器(analog-to-digital converters,adc)、飞行时间(timeofflight,tof)测量、和仪器测量等应用领域中变得越来越重要。尤其是在激光雷达的飞行时间测量应用领域中,高性能时间数字转换器是必不可少的技术,随着激光雷达对测距精度要求的不断提高,对时间数字转换电路的精度要求达到了皮秒量级。但是,要同时满足低功耗、高线性度、精细分辨率、大动态范围和紧凑性的要求是很困难的。

2、最传统的tdc使用反相器或缓冲延迟单元来量化时间,并且能够在cmos技术中实现15-30ps的分辨率,但是反相器或缓冲延迟单元存在最小的延迟极限,不能应用于更高性能的tdc。其后提出的采用游标结构的tdc存在单元不匹配的问题,基于缓冲延迟链或游标延迟链的tdc具有非常有限的动态范围,多种基于时间放大器的tdc存在检测范围有限和功耗高的问题,为了实现宽动态范围和高分辨率开发的基于游标环形差分延迟振荡器的tdc则译码复杂且功耗高。

3、因此,提供一种能够在低功耗的情况下实现高分辨率和宽动态范围的时间数字转换器成为亟待解决的问题。

技术实现思路

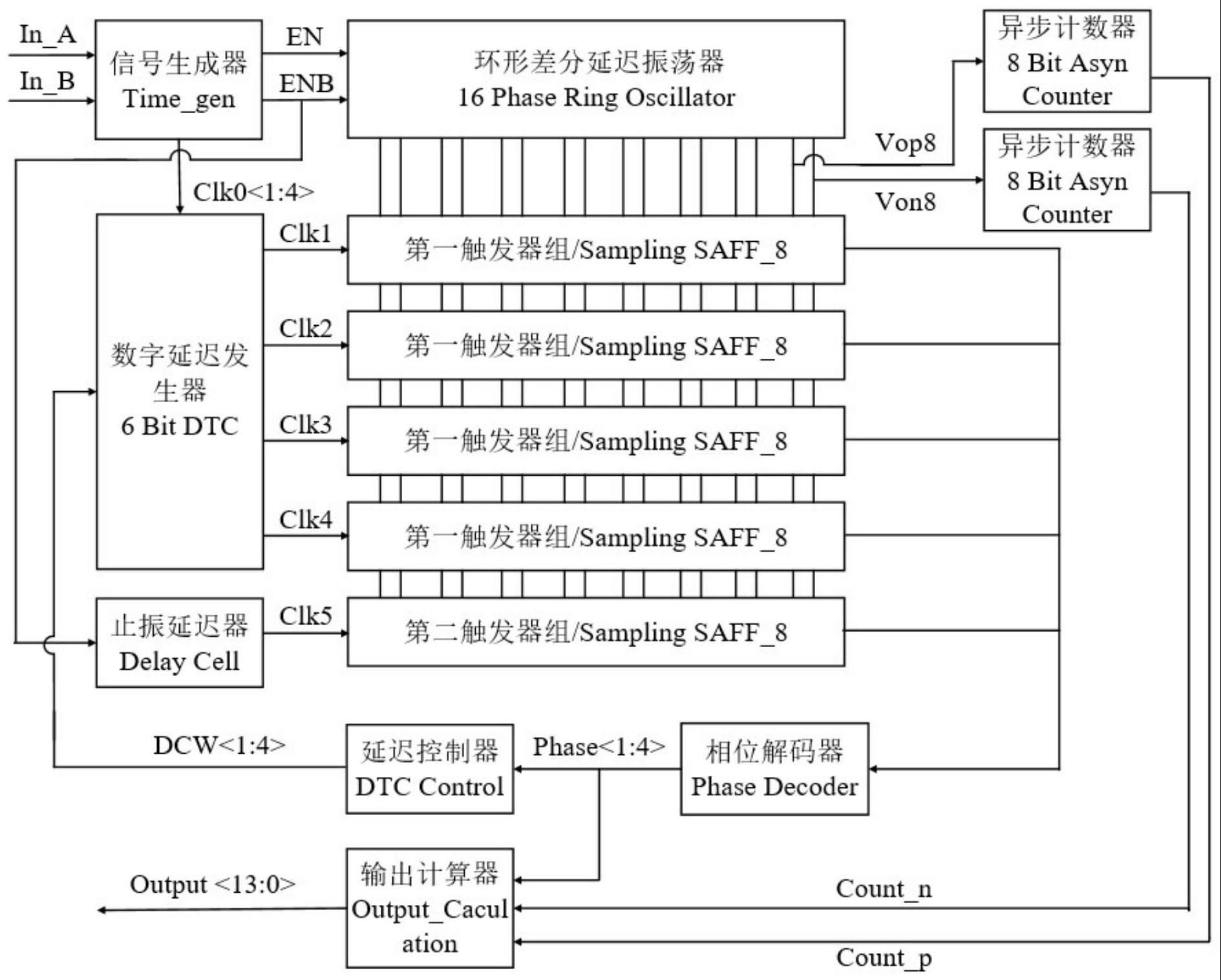

1、因此,为了解决现有技术中出现的上述问题,本技术提供了一种基于并联采样环振荡器和多触发器采样的、能够实现动态元件匹配进而能够在低功耗的情况下实现高分辨率和大动态范围的时间数据转换电路,以及与该时间数据转换电路对应的时间数据转换方法。

2、根据第一方面,本发明提供了一种时间数字转换电路,包括:

3、信号生成器,用于接收第一输入信号和第二输入信号,并基于第一输入信号和第二输入信号生成使能信号,基于第二输入信号生成采样信号;且用于在接收到第二输入信号经过预设时间差后生成禁用信号;

4、环形差分延迟振荡器,用于在使能信号控制下启振生成差分延迟脉冲;环形差分延迟振荡器在禁用信号的控制下止振,并在下一次时间间隔量化开始时自禁用位置启振;

5、两个异步计数器,用于对差分延迟脉冲进行延迟单元计数,得到的第一计数结果;

6、多个数字延迟发生器,用于对采样信号进行延迟,生成多个第一延迟采样信号;多个第一延迟采样信号相对于采样信号的延迟量的以预设延迟差逐级递增;

7、多个第一触发器组,与多个数字延迟发生器对应设置,每个第一触发器组均用以在对应的第一延迟采样信号的触发下采集环形差分延迟振荡器的相位状态;

8、止振延迟器,用于延迟禁用信号,生成第二延迟采样信号;

9、第二触发器组,用于在第二延迟采样信号的触发下采集环形差分延迟振荡器的禁用时的相位状态;

10、相位解码器,用于根据多个第一触发器组采集的相位状态生成第二计数结果;还用于根据第二触发器采集的环形差分延迟振荡器的禁用时的相位状态生成下一次时间间隔量化的起始位置标记;

11、输出计算器,用以根据第一计算结果、第二计算结果和起始位置标记输出第一输入信号和第二输入信号之间的时间间隔量化结果。

12、在可选的实施方式中,环形差分延迟振荡器包括:

13、多个依次连接的延时单元,一级延时单元的正输出端连接其后一级延迟单元的正输入端,负输出端连接其后一级延迟单元的负输入端;且最后一级延时单元的正输出端连接第一级延迟单元的负输入端,最后一级延时单元的负输出端连接第一级延迟单元的正输入端;延时单元包括差分延迟模块、控制模块和锁存模块,差分延迟模块与控制模块相连接,锁存模块和差分延迟模块相连接;控制模块用于接收使能信号和禁用信号,差分延迟模块用于在使能信号的控制下接收差分输入电压并生成差分输出电压,锁存模块用于锁存差分延迟模块的电平状态。

14、在可选的实施方式中,环形差分延迟振荡器包括:

15、第一pmos管和第一nmos管,二者的源极分别连接驱动电源的高电平输出端和低电平输出端;

16、第二pmos管和第二nmos管,二者的栅极相互连接并接入第一差分输入电压,二者的漏极相互连接并连接至第一差分电压输出端,第二pmos管的源极与第一pmos管的漏极相连接,第二nmos管的源极与第一nmos管的漏极相连接;

17、第三pmos管和第三nmos管,二者的栅极相互连接并接入第二差分输入电压,二者的漏极相互连接并连接至第二差分电压输出端,第三pmos管的源极与第一pmos管的漏极相连接,第三nmos管的源极与第一nmos管的漏极相连接;

18、第四pmos管和第四nmos管,二者的源极分别连接驱动电源的高电平输出端和低电平输出端,二者的漏极相互连接并连接至第一差分电压输出端,二者的栅极相互连接并连接至第二差分电压输出端;

19、第五pmos管和第五nmos管,二者的源极分别连接驱动电源的高电平输出端和低电平输出端,二者的漏极相互连接并连接至第二差分电压输出端,二者的栅极相互连接并连接至第一差分电压输出端。

20、在可选的实施方式中,第一触发器组和第二触发器组内的触发器均为基于感测放大器的d触发器。

21、在可选的实施方式中,时间数字转换电路还包括:

22、数字延迟控制器,设置于相位解码器和数字延迟发生器之间,用于根据多个第一触发器组采集的相位状态调节多个数字延迟发生器的延迟,直至多个数字延迟发生器之间逐级递增的预设延迟差τclk=τbuf/n,其中,n是指数字延迟发生器的个数,τbuf是指环形差分延迟振荡器中一个延迟单元的延迟量。

23、在可选的实施方式中,数字延迟发生器包括:

24、二进制码到温度计码转换器,用于接收数字延迟控制器的控制信号,并将控制信号转换为热表码输出;

25、pmos负载阵列,其内的各个pmos负载的源极均与其自身的漏极短接,且各pmos负载的源极分别与二进制码到温度计码转换器的各个输出端相连接;

26、输入反相器,其输入端接入采样信号,输出端连接至第一缓冲反相器组、第二缓冲反相器组和第三缓冲反相器组的输出端;第一缓冲反相器组包括一个缓冲反相器,第二缓冲反相器组包括两个缓冲反相器,第三缓冲反相器组包括四个缓冲反相器;

27、第一输出反相器,pmos负载阵列内各个pmos负载的栅极、第一缓冲反相器组的输出端均与第一输出反相器的输入端相连接,且第二缓冲反相器组的输出端经过第一选择控制开关后、第三缓冲反相器组的输出端经过第二选择控制开关后也均与第一输出反相器的输入端相连接;

28、第二输出反相器,输入端与第一输出反相器的输出端相连接,输出端输出第一延迟采样信号。

29、根据第二方面,本发明还提供了一种时间数字转换方法,包括如下步骤:

30、将第一时间信号和第二时间信号输入上述第一面任意一种实施方式中的时间数字转换电路内,得到第一时间信号和第二时间信号之间的时间间隔量化结果。

31、根据第三方面,本发明还提供了一种时间数字转换方法,包括如下步骤:

32、多次将第一时间信号和第二时间信号输入上述第一面任意一种实施方式中的时间数字转换电路内,得到第一时间信号和第二时间信号之间的多个初步时间间隔量化结果;

33、本发明提供的技术方案,具有如下优点:

34、1、本发明提供的时间数字转换电路,通过对应设置多个数字延迟发生器和多个第一触发器组,对环形差分延迟振荡器的相位状态进行多次延迟采样,能够将该时间数字转换电路的时间分辨率提高到环形差分延迟振荡器中的分辨率的n分之一(n即为数字延迟发生器的个数),且数字延迟发生器和触发器组消耗的功率远远低于核心的环振荡器和计数器消耗的功率,因而,能够在低功耗的情况下实现高分辨率;而通过设置振荡器为环形差分延迟振荡器并对应设置两个异步计数器,能够大大减小计数器锁存的第一计数结果错误的可能性,通过设置环形差分延迟振荡器在电路接收到第二输入信号一段时间后禁用(相应地,两个异步计数器也不工作),且在下一次时间间隔量化开始时从先前停止的位置开始振荡(也即环形差分延迟振荡器可以从其中的任何延迟单元开始振荡),能够在进一步电路功耗的同时实现动态元件匹配,随机化由于缓冲元件失配而生成的线性误差解决了现有技术中大量延迟单元失配所造成高积分非线性的问题,使该数字转换电路具有良好的线性度和宽动态范围。

35、2、本发明提供的时间数字转换电路,通过设置第一触发器组和第二触发器组内的触发器均为基于感测放大器的d触发器(saffs),可以将环形差分延迟振荡器发生在时钟上升沿附近时采样数据所生成的亚稳态最小化,能够进一步提高时间数字转换电路的量化数据准确度。

36、3、本发明提供的时间数字转换方法,由于不同的延迟单元不匹配导致不同的测量结果,随机误差可能表现为单发精度测试中输出代码的变化,因而通过对多个初步时间间隔量化结果进行平均,能够减少减少输出的变化,进一步提高最终得到的时间间隔量化结果的准确性。

本文地址:https://www.jishuxx.com/zhuanli/20240730/152560.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表