一种基于FPGA与恒温晶振的同步守时模块的制作方法

- 国知局

- 2024-07-30 10:24:53

本发明涉及电子设备,尤其涉及一种基于fpga与恒温晶振的同步守时模块。

背景技术:

1、许多领域需要同步时钟,并且对精度要求很高,比如时间同步服务器、授时设备、电力系统设备等等,这些设备不仅对时间同步的要求高,而且需要具有守时功能,比如卫星信号丢失或者同步设备掉电等,在这种情况下要求同步设备能够凭“记忆”自我同步。目前市面上的同步守时的功能很多是以设备的形式面市,即使以模块的形式面市,价格也较为昂贵。

技术实现思路

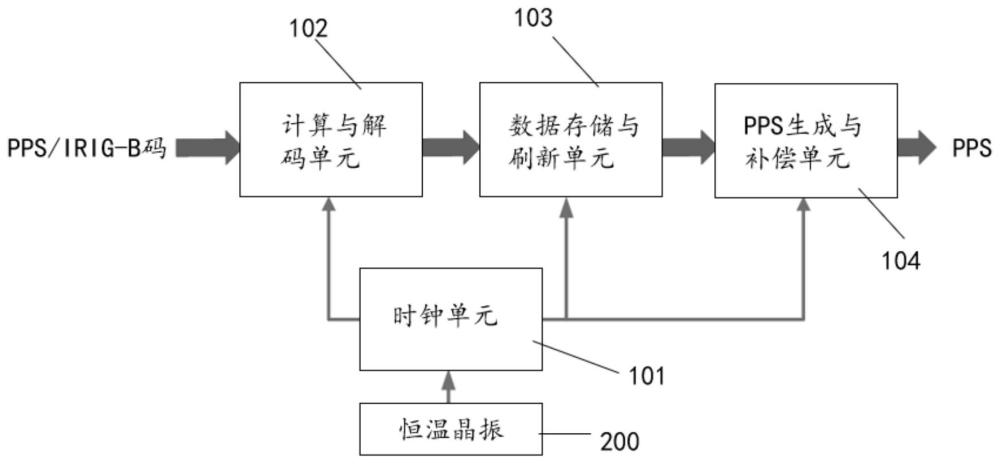

1、为解决现有技术中的上述问题中的至少一部分问题,本发明的任务是提供一种基于fpga与恒温晶振的同步守时模块,包括:

2、恒温晶振,其被配置为向fpga模块提供时钟;

3、fpga模块,其包括:

4、时钟单元,其被配置为接收恒温晶振的时钟,并向计算与解码单元、数据存储与刷新单元及pps生成与补偿单元提供时钟;

5、计算与解码单元,其被配置为接收外部同步设备的pps信号或irig-b码,并能够将irig-b码解码出pps信号和实时时间,根据时钟单元提供的时钟计算pps间隔所对应的秒间隔步长,动态计算每个同步周期的时钟数,并且计算同步后的变化趋势以及预测趋势,作为同步数据;

6、数据存储与刷新单元,其被配置为存储生成pps所需要的默认数据及所述计算与解码单元计算的同步数据,并提供给pps生成与补偿单元;以及

7、pps生成与补偿单元,其被配置为根据时钟单元提供的时钟生成pps信号,并将所述数据存储与刷新单元提供的秒间隔步长和趋势预测作为pps生成与补偿单元的秒间隔步长。

8、进一步地,当外部同步设备的pps信号的上升沿或者irig-b码的上升沿到达所述计算与解码单元时,所述计算与解码单元确认该上升沿为同步脉冲,所述计算与解码单元开始计算所述时钟单元输入的时钟数,在下一个pps信号或者irig-b码的上升沿到达时,所计算的时钟数为一次秒间隔步长。

9、进一步地,在irig-b码的上升沿到达所述计算与解码单元开始,所述计算与解码单元进行时钟计数计算秒间隔步长之外,还按照irig-b码的格式解析出当前的具体时间。

10、进一步地,所述计算与解码单元动态存储秒间隔步长,并且计算同步后的变化趋势以及预测趋势,并将秒间隔步长、变化趋势以及预测趋势数据存储入所述数据存储与刷新单元。

11、进一步地,所述数据存储与刷新单元存储有生成pps信号所需要的默认数据,在没有外部同步信号或者外部同步信号所存储的数据不足以作为生成pps信号的数据源时,将以所述默认数据提供给所述pps生成与补偿单元;

12、在外部同步信号存在时,所述数据存储与刷新单元接收并存储来所述计算与解码单元的同步数据,将所存储的数据提供给pps生成与补偿单元。

13、进一步地,所述同步守时模块初始化时,所述数据存储与刷新单元预存的秒间隔步长对应的时钟数为根据所述同步守时模块的时钟所产生的默认计数数据;

14、在外部同步信号存在时,所述数据存储与刷新单元存储外部同步信号的秒间隔步长所对应的同步守时模块的时钟的计数值,最近一段同步时间存入的数据与默认数据同时存储在所述数据存储与刷新单元。

15、进一步地,在守时情况下,将根据所述数据存储与刷新单元的标志位来决定以默认数据还是以最近一段同步时间存储的同步数据作为秒间隔步长的数据源,从而根据所述数据存储与刷新单元中存储的数据对pps信号进行校准和补偿。

16、进一步地,在外部同步信号存在时,所述pps生成与补偿单元能识别到输入pps信号的上升沿,所述pps生成与补偿单元输出的pps信号的上升沿能够与外部同步信号的上升沿同步。9.根据权利要求8所述的同步守时模块,其特征在于,当外部同步信号丢失时,所述计算与解码单元将通知所述pps生成与补偿单元,整个同步守时模块进入守时状态,所述pps生成与补偿单元将根据所述数据存储与刷新单元在有外部同步信号的情况下的存储的数据自动调整产生的pps信号,得到同步pps信号;

17、在守时状态又接收到外部同步信号时,所述计算与解码单元通知所述pps生成与补偿单元,在过度缓冲时间内逐步退出守时状态进入同步状态。

18、进一步地,在重新接收到外部同步信号时,所述计算与解码单元通知所述pps生成与补偿单元,同时所述计算与解码单元计算进入同步的秒间隔步长和预测趋势;

19、所述pps生成与补偿单元将根据守时的秒间隔步长与同步的秒间隔步长进行比较,如果差值超过设置的阈值,将逐秒调整pps信号的步长长度,使其逐渐接近实际的秒间隔步长,当同步的秒间隔步长与守时的秒间隔步长之间的误差小于设置的阈值时,将切换到同步模式。

20、本发明至少具有下列有益效果:本发明公开的一种基于fpga与恒温晶振的同步守时模块,该同步守时模块既满足解决高精度同步与守时的技术需求,也可以以模块的方式嵌入在设备或者单独作为gps信号与被同步设备之间的转接设备,且该同步守时模块的设计简单,成本低。

技术特征:1.一种基于fpga与恒温晶振的同步守时模块,其特征在于,包括:

2.根据权利要求1所述的同步守时模块,其特征在于,当外部同步设备的pps信号的上升沿或者irig-b码的上升沿到达所述计算与解码单元时,所述计算与解码单元确认该上升沿为同步脉冲,所述计算与解码单元开始计算所述时钟单元输入的时钟数,在下一个pps信号或者irig-b码的上升沿到达时,所计算的时钟数为一次秒间隔步长。

3.根据权利要求2所述的同步守时模块,其特征在于,在irig-b码的上升沿到达所述计算与解码单元开始,所述计算与解码单元进行时钟计数计算秒间隔步长之外,还按照irig-b码的格式解析出当前的具体时间。

4.根据权利要求2所述的同步守时模块,其特征在于,所述计算与解码单元动态存储秒间隔步长,并且计算同步后的变化趋势以及预测趋势,并将秒间隔步长、变化趋势以及预测趋势数据存储入所述数据存储与刷新单元。

5.根据权利要求4所述的同步守时模块,其特征在于,所述数据存储与刷新单元存储有生成pps信号所需要的默认数据,在没有外部同步信号或者外部同步信号所存储的数据不足以作为生成pps信号的数据源时,将以所述默认数据提供给所述pps生成与补偿单元;

6.根据权利要求5所述的同步守时模块,其特征在于,所述同步守时模块初始化时,所述数据存储与刷新单元预存的秒间隔步长对应的时钟数为根据所述同步守时模块的时钟所产生的默认计数数据;

7.根据权利要求6所述的同步守时模块,其特征在于,在守时情况下,将根据所述数据存储与刷新单元的标志位来决定以默认数据还是以最近一段同步时间存储的同步数据作为秒间隔步长的数据源,从而根据所述数据存储与刷新单元中存储的数据对pps信号进行校准和补偿。

8.根据权利要求6所述的同步守时模块,其特征在于,在外部同步信号存在时,所述pps生成与补偿单元能识别到输入pps信号的上升沿,所述pps生成与补偿单元输出的pps信号的上升沿能够与外部同步信号的上升沿同步。

9.根据权利要求8所述的同步守时模块,其特征在于,当外部同步信号丢失时,所述计算与解码单元将通知所述pps生成与补偿单元,整个同步守时模块进入守时状态,所述pps生成与补偿单元将根据所述数据存储与刷新单元在有外部同步信号的情况下的存储的数据自动调整产生的pps信号,得到同步pps信号;

10.根据权利要求9所述的同步守时模块,其特征在于,在重新接收到外部同步信号时,所述计算与解码单元通知所述pps生成与补偿单元,同时所述计算与解码单元计算进入同步的秒间隔步长和预测趋势;

技术总结本发明涉及一种基于FPGA与恒温晶振的同步守时模块,包括:恒温晶振,其被配置为向FPGA模块提供时钟;FPGA模块,其包括:时钟单元,其被配置为接收恒温晶振的时钟,并向计算与解码单元、数据存储与刷新单元及PPS生成与补偿单元提供时钟;计算与解码单元,其被配置为接收外部同步设备的PPS信号或IRIG‑B码,并能够将IRIG‑B码解码出PPS信号和实时时间,根据时钟单元提供的时钟计算PPS间隔所对应的秒间隔步长,动态计算每个同步周期的时钟数,并且计算同步后的变化趋势以及预测趋势,作为同步数据;数据存储与刷新单元,其被配置为存储生成PPS所需要的默认数据及所述计算与解码单元计算的同步数据,并提供给PPS生成与补偿单元;以及PPS生成与补偿单元。技术研发人员:林少钦,钱辰鹏受保护的技术使用者:小华半导体有限公司技术研发日:技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240730/152759.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表