一种基于频率保护的北斗同步时钟输入接口电路的制作方法

- 国知局

- 2024-07-30 10:26:32

本技术涉及一种基于频率保护的北斗同步时钟的应用接口电路,提供了一路原子钟的频率输入通道,属于通信。

背景技术:

1、北斗同步时钟是通过北斗卫星授时模块进行同步授时的一种设备,在正常工作时,设备能够满足授时精度要求。但如果在北斗卫星源受到干扰或者卫星信号源丢失时,设备将进行保持状态,此时依靠自身的tcxo或ocxo的保持能力,时间输出精度将不能保证。这时,通过接入更高一级的铷钟、铯钟、氢钟等原子钟输出的稳定的高质量的频率信号,来保持北斗同步时钟在卫星信号源丢失或卫星受到干扰时的高稳定性的输出,不失是一种很好的方法。

2、目前大多数北斗授时设备没有采用原子钟的输入保护的接口,采用这种方式将能使北斗同步时钟在丢失卫星的情况下,能稳定的提供稳定可靠的授时信号,且保持高质量的输出精度。

技术实现思路

1、本实用新型的目的是解决北斗卫星授时设备在北斗卫星源受到干扰或者卫星源丢失时,授时设备输出精度不能达到要求的问题,借助于原子钟的频率输出,进行频率保护。

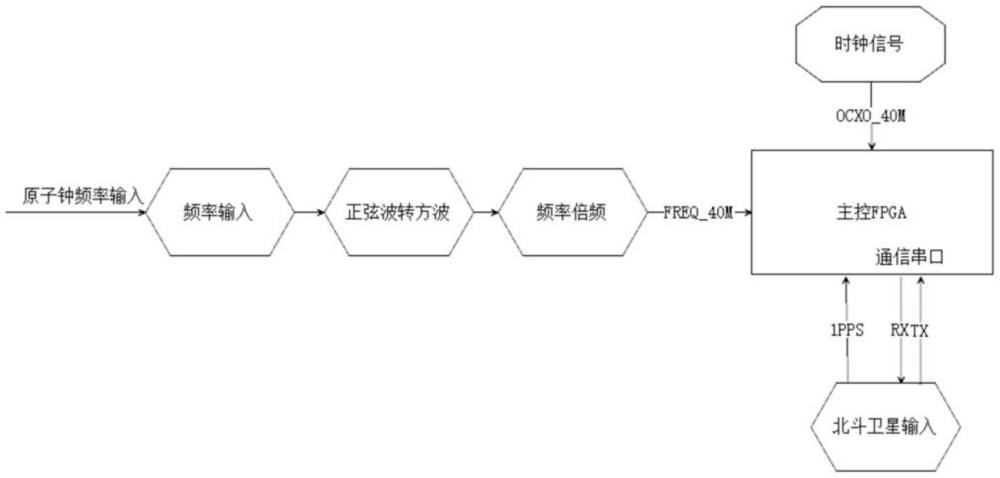

2、为了达到上述目的,本实用新型的技术方案是提供了一种基于频率保护的北斗同步时钟输入接口电路,其特征在于,包括主控fpga模块,主控fpga模块同时接受由时钟信号产生单元输出的时钟信号、北斗卫星接口电路输出的1pps信号、原子钟频率输出模块输出的原子钟频率信号。

3、优选地,所述原子钟频率输出模块包括用于接收原子钟频率输入的频率输入电路,频率输入电路的输出端连接正弦波转方波电路的输入端,正弦波转方波电路的输出端与频率倍频电路的输入端相连,频率倍频电路的输出端连接所述主控fpga模块。

4、优选地,所述主控fpga模块基于型号为ep3c10-e144的主控fpga芯片实现。

5、优选地,所述北斗卫星接口电路基于型号为bd7702的北斗卫星模块实现,其中:北斗卫星模块的3脚、5脚分别经由电阻r904、r955与所述主控fpga芯片的75脚、76脚相连;北斗卫星模块的6脚串接电阻r955后与所述主控fpga芯片的77脚相连;北斗卫星模块的8脚串接电阻r903接入电源地。

6、优选地,所述频率输入电路基于型号为hr601680的信号隔离变压器实现,其中:信号隔离变压器的1脚、3脚并接一个阻抗匹配电阻r935;信号隔离变压器的14脚串接电阻r923后接入数字地,16脚串接电阻r957后与电阻r907的一端以及隔直电容c922的一端相连,电阻r907的另一端接入数字地,隔直电容c922的另一端为所述频率输入电路的输出端。

7、优选地,所述正弦波转方波电路包括型号为max6102的电压参考芯片和型号为lt1720的高速电压比较器,其中:

8、电压参考芯片的1脚接5v电压输入;电压参考芯片的2脚接地;电压参考芯片的2脚接旁路电容c919,接高速电压比较器的2脚、串接电阻r913后接频率输入电路的输出端;

9、高速电压比较器的1脚串接电阻r914接入频率输入电路的输出端;高速电压比较器的8脚接5v电源、5脚为电源地;高速电压比较器的7脚和1脚并接一个反馈电阻r952,高速电压比较器的7脚接电阻r950的一端,电阻r950的另一端为所述正弦波转方波电路的输出端。

10、优选地,所述频率倍频电路基于型号为ics501的频率倍频芯片实现,其中:频率倍频芯片的1脚接所述正弦波转方波电路的输出端;频率倍频芯片的2脚接3.3v的电源输入、3脚为电源输入地,频率倍频芯片的2脚、3脚间并接旁路电容c924;频率倍频芯片的4脚、6脚接地;频率倍频芯片的5脚串接一个限流电阻r931和电容c920后接入所述主控fpga芯片的89脚。

11、本实用新型通过提供一路原子钟频率输入技术,对北斗同步时钟的稳定运行提供一种保护,在北斗卫星同步出现问题时,依靠稳定的原子钟频率输入,通过fpga内部的锁相环时钟切换,稳定地切换到原子钟频率输入,最终能够实现稳定地输出时钟信号。

技术特征:1.一种基于频率保护的北斗同步时钟输入接口电路,其特征在于,包括主控fpga模块,主控fpga模块同时接受由时钟信号产生单元输出的时钟信号(ocxo_40m)、北斗卫星接口电路输出的1pps信号、原子钟频率输出模块输出的原子钟频率信号(freq_40m)。

2.如权利要求1所述的一种基于频率保护的北斗同步时钟输入接口电路,其特征在于,所述原子钟频率输出模块包括用于接收原子钟频率输入的频率输入电路,频率输入电路的输出端连接正弦波转方波电路的输入端,正弦波转方波电路的输出端与频率倍频电路的输入端相连,频率倍频电路的输出端连接所述主控fpga模块。

3.如权利要求2所述的一种基于频率保护的北斗同步时钟输入接口电路,其特征在于,所述主控fpga模块基于型号为ep3c10-e144的主控fpga芯片(u700)实现。

4.如权利要求3所述的一种基于频率保护的北斗同步时钟输入接口电路,其特征在于,所述北斗卫星接口电路基于型号为bd7702的北斗卫星模块(u906)实现,其中:北斗卫星模块(u906)的3脚、5脚分别经由电阻r904、r955与所述主控fpga芯片(u700)的75脚、76脚相连;北斗卫星模块(u906)的6脚串接电阻r955后与所述主控fpga芯片(u700)的77脚相连;北斗卫星模块(u906)的8脚串接电阻r903接入电源地。

5.如权利要求3所述的一种基于频率保护的北斗同步时钟输入接口电路,其特征在于,所述频率输入电路基于型号为hr601680的信号隔离变压器(t900)实现,其中:信号隔离变压器(t900)的1脚、3脚并接一个阻抗匹配电阻r935;信号隔离变压器(t900)的14脚串接电阻r923后接入数字地,16脚串接电阻r957后与电阻r907的一端以及隔直电容c922的一端相连,电阻r907的另一端接入数字地,隔直电容c922的另一端为所述频率输入电路的输出端。

6.如权利要求3所述的一种基于频率保护的北斗同步时钟输入接口电路,其特征在于,所述正弦波转方波电路包括型号为max6102的电压参考芯片(d908)和型号为lt1720的高速电压比较器(d910),其中:

7.如权利要求3所述的一种基于频率保护的北斗同步时钟输入接口电路,其特征在于,所述频率倍频电路基于型号为ics501的频率倍频芯片(u903)实现,其中:频率倍频芯片(u903)的1脚接所述正弦波转方波电路的输出端;频率倍频芯片(u903)的2脚接3.3v的电源输入、3脚为电源输入地,频率倍频芯片(u903)的2脚、3脚间并接旁路电容c924;频率倍频芯片(u903)的4脚、6脚接地;频率倍频芯片(u903)的5脚串接一个限流电阻r931和电容c920后接入所述主控fpga芯片(u700)的89脚。

技术总结本技术涉及一种基于频率保护的北斗同步时钟输入接口电路,其特征在于,包括主控FPGA模块,主控FPGA模块同时接受由时钟信号产生单元输出的时钟信号、北斗卫星接口电路输出的1PPS信号、原子钟频率输出模块输出的原子钟频率信号。本技术通过提供一路原子钟频率输入技术,对北斗同步时钟的稳定运行提供一种保护,在北斗卫星同步出现问题时,依靠稳定的原子钟频率输入,通过FPGA内部的锁相环时钟切换,稳定地切换到原子钟频率输入,最终能够实现稳定地输出时钟信号。技术研发人员:王海嵩,邱祖雄,方国盛受保护的技术使用者:上海泰坦通信工程有限公司技术研发日:20230717技术公布日:2024/2/19本文地址:https://www.jishuxx.com/zhuanli/20240730/152914.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表