一种带校准环路的高精度数字时间转换器电路

- 国知局

- 2024-07-30 10:31:17

本发明属于混合信号集成电路设计领域,具体涉及一种带校准环路的高精度数字时间转换器电路。

背景技术:

1、uwb(ultra wide band,超宽带)雷达是一种使用超宽带信号进行探测和成像的雷达技术。它具有高分辨率、低功耗、抗干扰等优点,被广泛应用于军事、安全、工业、医疗等领域。而等效时间采样结构使其通过利用多相位时钟采样,然后经过合成可以实现多倍于采样时钟的采样率,能够应用于直接射频采样系统,该种结构简化了rf信号链,降低了每个通道的成本以及通道密度。

2、此外,uwb雷达开始广泛进入iot(internet of things,物联网)领域,对于接收机芯片的整体功耗提出了更高的要求。传统的多相位时钟由锁相环电路产生,虽然时钟质量有保证,但是功耗大、面积大,不适合低功耗低成本的场景。

技术实现思路

1、为了解决现有技术中存在的上述问题,本发明提供了一种带校准环路的高精度数字时间转换器电路。本发明要解决的技术问题通过以下技术方案实现:

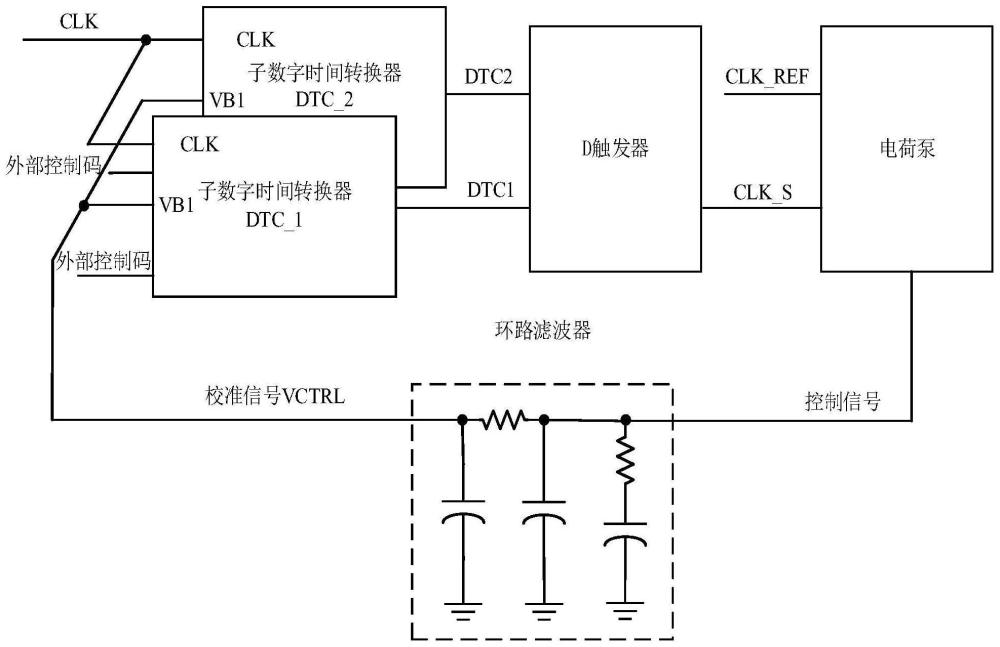

2、一种带校准环路的高精度数字时间转换器电路,包括:脉冲产生电路和校准环路;其中,

3、所述脉冲产生电路包括:子数字时间转换器dtc_1、子数字时间转换器dtc_2和d触发器;

4、所述子数字时间转换器dtc_1和所述子数字时间转换器dtc_2对外部控制码和第一参考信号clk进行处理,分别产生信号dtc1和信号dtc2;

5、所述d触发器根据所述信号dtc1和所述信号dtc2生成脉冲信号clk_s;

6、通过改变所述外部控制码实现对所述脉冲信号clk_s的上升沿进行相位移动;

7、所述校准环路包括:电荷泵和环路滤波器;

8、所述电荷泵对所述脉冲信号clk_s和第二参考信号clk_ref进行比较,根据比较结果产生控制所述环路滤波器进行充电或放电的控制信号;

9、所述环路滤波器根据所述控制信号输出校准信号vctrl至所述脉冲产生电路,所述校准信号vctrl对所述脉冲产生电路的充电电流进行调整,以将所述脉冲信号clk_s的脉宽调节至与所述第二参考信号clk_ref的脉宽相等,输出调整完成的脉冲信号clk_s,完成数字信号到时间信号的转换。

10、在本发明的一个实施例中,在所述脉冲产生电路中,

11、所述子数字时间转换器dtc_1的第一输入端接入所述第一参考信号clk,所述子数字时间转换器dtc_1的第二输入端接入所述外部控制码,所述子数字时间转换器dtc_1的第三输入端接入所述校准信号vctrl,所述子数字时间转换器dtc_1的输出端与所述d触发器的第一输入端连接;

12、所述子数字时间转换器dtc_2的第一输入端接入所述第一参考信号clk,所述子数字时间转换器dtc_2的第二输入端接入所述外部控制码,所述子数字时间转换器dtc_2的第三输入端接入所述校准信号vctrl,所述子数字时间转换器dtc_2的输出端与所述d触发器的第二输入端连接;

13、所述d触发器的输出端与所述校准环路的输入端连接。

14、在本发明的一个实施例中,子数字时间转换器dtc_1和所述子数字时间转换器dtc_2中任意一个的电路结构,包括:

15、电流源、复位模块、调节模块、dac电容阵列、比较器和或门;其中,

16、所述电流源的第一输入端接入电源电压,所述电流源的第一控制端vb1接入所述校准信号vctrl,所述电流源的第二控制端vb2接入外加偏置电压,所述电流源的输出端与所述复位模块的输入端连接;

17、所述复位模块的控制端接入复位信号clk_r,所述复位模块的输出端与所述dac电容阵列的第一输入端连接;

18、所述调节模块的第一输入端接入外部控制信号dac_p,所述调节模块的第二输入端接入外部控制信号dac_n,所述调节模块的输出端与所述复位模块的输入端连接;

19、所述dac电容阵列的第二输入端接入参考电压vref,所述dac电容阵列的第三输入端接地,所述dac电容阵列的输出端与所述比较器的正向输入端连接;

20、所述比较器的负向输入端接入外部固定电压vth;

21、所述或门的第一输入端接入信号clk_out,所述或门的第二输入端与所述比较器的输出端连接,所述或门的输出端作为子数字时间转换器的输出端。

22、在本发明的一个实施例中,电流源包括:mos管m1和mos管m2;其中,

23、所述mos管m1的源极接入所述电源电压,所述mos管m1的栅极接入所述校准信号vctrl,所述mos管m1的漏极与所述mos管m2的源极连接;

24、所述mos管m2的栅极接入所述外加偏置电压,所述mos管m2的漏极与所述复位模块的输入端连接。

25、在本发明的一个实施例中,复位模块包括:mos管m3、mos管m4、第一开关;其中,

26、所述mos管m3的源极与所述mos管m2的漏极连接,所述mos管m3的栅极接入所述复位信号clk_r,所述mos管m3的漏极与所述mos管m4的漏极连接;

27、所述mos管m4的源极接地,所述mos管m4的栅极接入所述复位信号clk_r;

28、所述第一开关的第一控制端接入所述复位信号clk_r,所述第一开关的第二控制端接入所述复位信号clk_r的反向信号clk_rn,所述第一开关的第一端与所述mos管m3的源极连接,所述第一开关的第二端接地。

29、在本发明的一个实施例中,调节模块包括15个相同的电流调节单元currentcell;所述15个相同的电流调节单元current cell采用并联的方式相互连接;所述15个相同的电流调节单元current cell中任意一个的电路结构包括:

30、第二开关、第三开关、mos管m5、mos管m6、mos管m7和mos管m8;其中,

31、所述第二开关的第一控制端接入所述外部控制信号dac_p,所述第二开关的第二控制端接入所述外部控制信号dac_n,所述第二开关的第一端接入所述校准信号vctrl,所述第二开关的第二端与所述mos管m5的漏极连接;

32、所述第三开关的第一控制端接入所述外部控制信号dac_p,所述第三开关的第二控制端接入所述外部控制信号dac_n,所述第三开关的第一端接入所述外加偏置电压,所述第三开关的第二端与所述mos管m7的漏极连接;

33、所述mos管m5的源极接入所述电源电压,所述mos管m5的栅极接入所述外部控制信号dac_p,所述mos管m5的漏极与所述mos管m6的栅极连接;

34、所述mos管m6的源极接入所述电源电压,所述mos管m6的漏极与所述mos管m8的源极连接;

35、所述mos管m7的源极接入所述电源电压,所述mos管m7的栅极接入所述外部控制信号dac_p,所述mos管m7的漏极与所述mos管m8的栅极连接;

36、所述mos管m8的漏极与所述mos管m3的源极连接。

37、在本发明的一个实施例中,dac电容阵列包括:

38、第一电容c0、第二电容c1、第三电容c2、第四电容c3、第五电容c4、第六电容c5、第七电容c6、第八电容c7、第九电容c8、第十电容c9、第一切换开关s0、第二切换开关s1、第三切换开关s2、第四切换开关s3、第五切换开关s4、第六切换开关s5、第七切换开关s6、第八切换开关s7、第九切换开关s8和第十切换开关s9;其中,

39、所述第一电容c0的第一端与所述比较器的正向输入端连接,所述第一电容c0的第二端与所述第一切换开关s0的第一端连接;

40、所述第二电容c1的第一端与所述第一电容c0的第一端连接,所述第二电容c1的第二端与所述第二切换开关s1的第一端连接;

41、所述第三电容c2的第一端与所述第二电容c1的第一端连接,所述第三电容c2的第二端与所述第三切换开关s2的第一端连接;

42、所述第四电容c3的第一端与所述第三电容c2的第一端连接,所述第四电容c3的第二端与所述第四切换开关s3的第一端连接;

43、所述第五电容c4的第一端与所述第四电容c3的第一端连接,所述第五电容c4的第二端与所述第五切换开关s4的第一端连接;

44、所述第六电容c5的第一端与所述第五电容c4的第一端连接,所述第六电容c5的第二端与所述第六切换开关s5的第一端连接;

45、所述第七电容c6的第一端与所述第六电容c5的第一端连接,所述第七电容c6的第二端与所述第七切换开关s6的第一端连接;

46、所述第八电容c7的第一端与所述第七电容c6的第一端连接,所述第八电容c7的第二端与所述第八切换开关s7的第一端连接;

47、所述第九电容c8的第一端与所述第八电容c7的第一端连接,所述第九电容c8的第二端与所述第九切换开关s8的第一端连接;

48、所述第十电容c9的第一端与所述第九电容c8的第一端连接,所述第十电容c9的第一端还与所述mos管m4的漏极连接,所述第十电容c9的第二端与所述第十切换开关s9的第一端连接;

49、所述第一切换开关s0的第二端接入所述参考电压vref,所述第一切换开关s0的第三端接地;

50、所述第二切换开关s1的第二端接入所述参考电压vref,所述第二切换开关s1的第三端接地;

51、所述第三切换开关s2的第二端接入所述参考电压vref,所述第三切换开关s2的第三端接地;

52、所述第四切换开关s3的第二端接入所述参考电压vref,所述第四切换开关s3的第三端接地;

53、所述第五切换开关s4的第二端接入所述参考电压vref,所述第五切换开关s4的第三端接地;

54、所述第六切换开关s5的第二端接入所述参考电压vref,所述第六切换开关s5的第三端接地;

55、所述第七切换开关s6的第二端接入所述参考电压vref,所述第七切换开关s6的第三端接地;

56、所述第八切换开关s7的第二端接入所述参考电压vref,所述第八切换开关s7的第三端接地;

57、所述第九切换开关s8的第二端接入所述参考电压vref,所述第九切换开关s8的第三端接地;

58、所述第十切换开关s9的第二端接入所述参考电压vref,所述第十切换开关s9的第三端接地;

59、所述第一切换开关s0、所述第二切换开关s1、所述第三切换开关s2、所述第四切换开关s3、所述第五切换开关s4、所述第六切换开关s5、所述第七切换开关s6、所述第八切换开关s7、所述第九切换开关s8和所述第十切换开关s9在所述外部控制码的控制下进行切换。

60、在本发明的一个实施例中,d触发器根据所述信号dtc1和所述信号dtc2生成脉冲信号clk_s的工作过程,包括:

61、所述d触发器将所述信号dtc1的上升沿作为生成的脉冲信号clk_s的上升沿,将所述信号dtc2的上升沿作为生成的脉冲信号clk_s的下降沿,进而组合生成所述脉冲信号clk_s。

62、在本发明的一个实施例中,电荷泵的电路结构包括:

63、mos管m9、mos管m10、mos管m11、mos管m12、mos管m13、mos管m14、mos管m15、mos管m16、mos管m17、mos管m18、mos管m19、mos管m20、mos管m21、mos管m22、mos管m23、第一运算放大器、第二运算放大器、第四开关、第五开关、第六开关、第七开关、p组电流单元currentcell_p和n组电流单元current cell_n;其中,

64、所述mos管m9的源极接入所述电源电压,所述mos管m9的栅极与所述mos管m10的栅极连接,所述mos管m9的漏极与所述mos管m10的源极连接;

65、所述mos管m10的漏极与所述mos管m10的栅极连接;

66、所述mos管m11的源极接入所述电源电压,所述mos管m11的栅极与所述mos管m9的栅极连接,所述mos管m11的漏极与所述mos管m12的源极连接;

67、所述mos管m12的栅极与所述mos管m10的栅极连接,所述mos管m12的漏极与所述第一运算放大器的同相输入端连接;

68、所述mos管m13的源极接入所述电源电压,所述mos管m13的栅极与所述mos管m11的栅极连接,所述mos管m13的漏极与所述mos管m14的源极连接;

69、所述mos管m14的栅极与所述mos管m12的栅极连接,所述mos管m14的漏极与所述第四开关的第一端连接;

70、所述mos管m15的源极与所述mos管m16的漏极连接,所述mos管m15的栅极与所述mos管m15的漏极连接,所述mos管m15的漏极接入信号iref_50u;

71、所述mos管m16的源极接地,所述mos管m16的栅极与所述mos管m15的栅极连接;

72、所述mos管m17的源极与所述mos管m18的漏极接地,所述mos管m17的栅极与所述mos管m15的漏极连接,所述mos管m17的漏极接入信号iref_50u_1;

73、所述mos管m18的源极接地,所述mos管m18的栅极与所述mos管m17的漏极连接;

74、所述mos管m19的源极接地,所述mos管m19的栅极与所述mos管m18的栅极连接,所述mos管m19的漏极与所述mos管m10的漏极连接;

75、所述mos管m20的源极与所述mos管m21的漏极连接,所述mos管m20的栅极与所述mos管m17的栅极连接,所述mos管m20的漏极与所述第一运算放大器的同相输入端连接;

76、所述mos管m21的源极接地,所述mos管m21的栅极与所述mos管m19的栅极连接;

77、所述mos管m22的源极与所述mos管m23的漏极连接,所述mos管m22的栅极与所述mos管m20的栅极连接,所述mos管m22的漏极与所述第五开关的第二端连接;

78、所述mos管m23的源极接地,所述mos管m23的栅极与所述mos管m21的栅极连接;

79、所述第一运算放大器的反相输入端接入信号cp_out,所述第一运算放大器的输出端与所述mos管m11的栅极连接;

80、所述第二运算放大器的同相输入端与所述第六开关的第二端连接,所述第二运算放大器的反相输入端与所述第二运算放大器的输出端连接,所述第二运算放大器的输出端与所述第四开关的第二端连接;

81、所述第四开关的第一控制端接入信号up_n,所述第四开关的第二控制端接入信号up_p,所述第四开关的第一端与所述第六开关的第一端连接,所述第四开关的第二端与所述第五开关的第一端连接;

82、所述第五开关的第一控制端接入信号dn_n,所述第五开关的第二控制端接入信号dn_p,所述第五开关的第二端与所述第七开关的第二端连接;

83、所述第六开关的第一控制端接入所述信号up_p,所述第六开关的第二控制端接入所述信号up_n,所述第六开关的第二端接入所述信号cp_out;

84、所述第七开关的第一控制端接入所述信号dn_p,所述第七开关的第二控制端接入所述信号dn_n,所述第七开关的第一端与所述第六开关的第二端连接;

85、所述p组电流单元current cell_p的第一输入端接入信号cp_p,所述p组电流单元current cell_p的第二输入端接入信号cp_n,所述p组电流单元current cell_p的输出端与所述第四开关的第一端连接;

86、所述n组电流单元current cell_n的第一输入端接入所述信号cp_p,所述n组电流单元current cell_n的第二输入端接入所述信号cp_n,所述n组电流单元current cell_n的输出端与所述第五开关的第二端连接。

87、在本发明的一个实施例中,电荷泵对所述脉冲信号clk_s和所述第二参考信号clk_ref进行比较,根据比较结果产生控制所述环路滤波器进行充电或放电的控制信号的工作过程,包括:

88、所述电荷泵将所述脉冲信号clk_s转换为差分信号,作为所述信号up_n和所述信号up_p;

89、所述电荷泵将所述第二参考信号clk_ref转换为差分信号,作为所述信号dn_n和所述信号dn_p;

90、当所述信号up_n和所述信号up_p为高电平时,生成第一控制信号控制所述环路滤波器进行充电;

91、当所述信号dn_n和所述信号dn_p为高电平时,生成第二控制信号控制所述环路滤波器进行放电。

92、本发明的有益效果:

93、本发明实施例所提供的方案中,通过d触发器对两个子数字时间转换器生成的信号dtc1和dtc2进行组合,生成脉冲信号clk_s,通过这种结构减少了翻转点变化带来的误差;采用电荷泵对脉冲信号clk_s和第二参考信号clk_ref进行比较,根据比较结果生成控制信号对环路滤波器的电压进行调整,环路滤波器输出校准信号vctrl对脉冲信号clk_s的脉宽进行调节,使得脉冲信号clk_s的脉宽和第二参考信号clk_ref的脉宽相等;通过改变外部控制码进而使得脉冲信号的整体发生相移,省去了传统技术中的锁相环电路;在降低了电路的功耗和面积的同时,保证了较高的精度,降低了成本。

本文地址:https://www.jishuxx.com/zhuanli/20240730/153193.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表