一种应用于电子雷管的时钟快速校正方法与流程

- 国知局

- 2024-07-30 10:33:09

本发明涉及电子雷管,尤其涉及一种应用于电子雷管的时钟快速校正方法。

背景技术:

1、电子雷管芯片应用于爆破行业,因此,其各项指标必须稳定且可靠。其应用场景多样,部分应用场景甚至会产生强烈干扰,严重阻碍通信的准确性。不能产生稳定通信,电子雷管产生拒爆的概率会大大增加,对生产活动造成极大损害。稳定且准确的时钟是雷管能正确工作的首要保证。现有文献为cn103868416a的发明专利公开了一种对芯片原始振荡频率时钟进行校正的方法,其是基于所述的芯片包括一数字逻辑处理电路及与其相连的非易失性记忆体电路、振荡器时钟电路、电流反馈电路,所述的数字逻辑处理电路输出端口用于调整振荡器时钟电路的输出频率,并且在所述数字逻辑处理电路内部设有第一计数器及第二计数器,主机向芯片发送一修改所述输出端口的指令,该指令内含一数据,该数据存储于所述记忆体电路中,本发明的方法可实现了电子雷管内置控制芯片内置rc振荡器时钟电路的频率调整,使其与设计预期值高度一致。上述方案是不断修改时钟配置字,并继续计时反馈间隔的方法实现时钟的校正,但是上述方案的时钟读取精度低,同时校正过程中需要人员对时钟进行多次调整,提高了操作人员的负担,从而导致系统的稳健性以及可靠性低。

技术实现思路

1、本发明的目的是为了解决上述背景技术中提出的技术问题。

2、本发明采用了如下技术方案:一种应用于电子雷管的时钟快速校正方法,包括以下步骤:

3、s1:获取参考时间信号,使用一个准确可靠的时间源作为参考时间信号;

4、s2:传输参考时间信号,通过无线通信将参考时间信号传输到电子雷管系统中;

5、s3:接收参考时间信号,集成接收单元,以接收来自选定时间源的信号;

6、s4:比较和校正,将接收到的参考时间信号与电子雷管内部时钟进行比较;

7、s5:调整内部时钟,计算出的时钟偏差,调整电子雷管内部时钟;

8、s6:反馈和验证,通过比较内部时钟和参考时间信号来验证校正的效果;

9、s7:实时监测,校正后,实时监测内部时钟的稳定性;

10、s8:容错机制,引入容错机制,以应对干扰或错误。

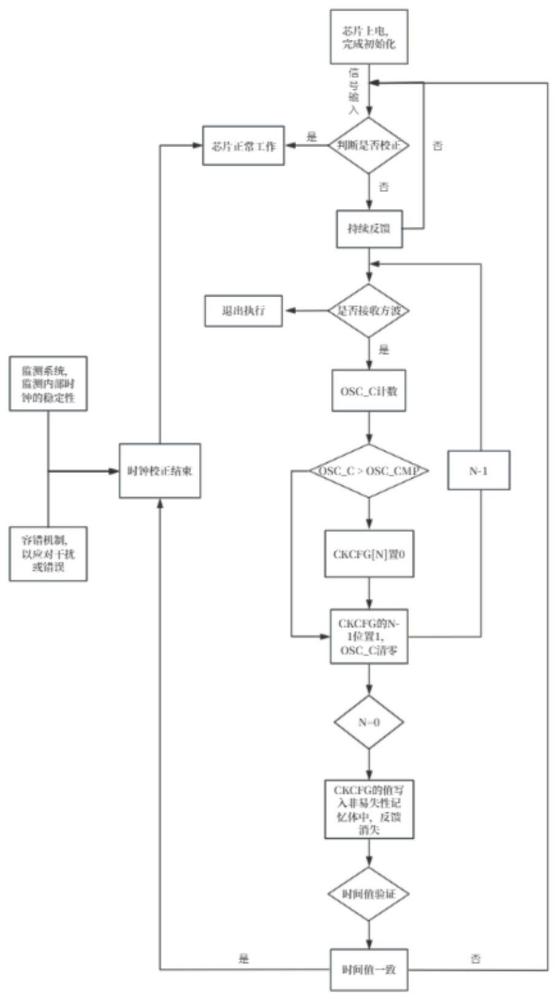

11、较佳的,所述s1-s3步骤中,时钟校正判断步骤为:

12、判断是否进行过时钟校正:

13、若结果为是,则电子雷管芯片正常工作;

14、若结果为否,持续反馈并等待接收持续高电平。

15、此处,系统能够自动判断是否进行过时钟校正,确保电子雷管芯片正常工作,并通过持续反馈等待接收持续高电平,提高稳定性。

16、较佳的,所述s1-s3步骤中,接收高电平的步骤为:

17、检测是否接收到持续超过设定值的时钟周期的持续高电平:

18、若判断结果为否,则等待接收指令;

19、若判断结果为是,则判断是否接收到方波,若判断结果为是,则进入计数步骤;若判断结果为否,则退出执行。

20、此处,引入了检测高电平的步骤,通过判断是否接收到持续高电平,有效防止错误操作,提高系统的稳健性。

21、较佳的,所述s4中,电子雷管芯片在方波的上升沿开始计数osc_c,下降沿时结束计数,则比较步骤为:

22、将osc_c的值和osc_cmp比较:

23、若osc_c>osc_cmp,则将ckcfg[n:0]的第n位置0;

24、若osc_c≤osc_cmp,则第n位不动。

25、将ckcfg的n-1位置1,osc_c清零,之后n自减1,重复计数步骤到自减步骤直到n=0,将寄存器ckcfg的值写入非易失性记忆体中,反馈消失。

26、此处,能够精确计算时钟偏差并调整内部时钟,确保电子雷管的时钟准确性。

27、较佳的,所述s6中,获取电子雷管内部时钟的当前值和来自参考时间信号的实际时间值进行比较,验证步骤为:

28、若两组时间值一致,则时钟校正准确;

29、若两组时间值不一致,则时钟校正不准确。

30、此处,实时比较内部时钟和参考时间信号,能够迅速验证时钟校正的准确性,确保系统时钟的可靠性。

31、较佳的,所述s6步骤中,时钟校正不正确,重复s1-s6步骤,直到时钟校正准确。此处,有助于提高时钟校正过程中的稳定性,提高时钟的精确度。

32、较佳的,所述s7中,建立实时监测系统,定期检查内部时钟的稳定性,设定稳定性阈值和警报机制,及时发现并响应时钟漂移或异常。此处,有助于及时发现和响应时钟漂移或异常,提高系统可靠性。

33、较佳的,所述s8中,设计系统能够自动修正时钟或发出警告,确保系统稳定性。此处,确保在出现异常情况下及时采取措施,增强系统稳定性。

34、与现有技术相比,本发明的优点和积极效果在于:

35、本发明中,引入时钟校正判断步骤,系统能够自动判断是否进行过时钟校正,有助于确保电子雷管芯片正常工作,与传统方法相比,这种自动判断机制减轻了操作人员的负担,提高了系统的自动化程度;引入检测高电平的步骤,有效防止错误操作,提高了系统的稳健性,可以防止误判和不正确的时钟信号输入,减少系统异常的可能性,相较于传统方法,这种检测机制提高了系统的可靠性;系统自动修正时钟或发出警告,确保了系统稳定性,这种主动响应机制有助于在出现异常情况下及时采取措施,增强了系统的稳定性和可靠性;建立实时监测系统,定期检查内部时钟的稳定性,设定稳定性阈值和警报机制,可以及时发现和响应时钟漂移或异常,提高了系统的可靠性。

技术特征:1.一种应用于电子雷管的时钟快速校正方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的应用于电子雷管的时钟快速校正方法,其特征在于:所述s1-s3步骤中,时钟校正判断步骤为:

3.根据权利要求1所述的应用于电子雷管的时钟快速校正方法,其特征在于:所述s1-s3步骤中,接收高电平的步骤为:

4.根据权利要求1所述的应用于电子雷管的时钟快速校正方法,其特征在于:所述s4中,电子雷管芯片在方波的上升沿开始计数osc_c,下降沿时结束计数,则比较步骤为:

5.根据权利要求1所述的应用于电子雷管的时钟快速校正方法,其特征在于:所述s6中,获取电子雷管内部时钟的当前值和来自参考时间信号的实际时间值进行比较,验证步骤为:

6.根据权利要求1所述的应用于电子雷管的时钟快速校正方法,其特征在于:所述s6步骤中,时钟校正不正确,重复s1-s6步骤,直到时钟校正准确。

7.根据权利要求1所述的应用于电子雷管的时钟快速校正方法,其特征在于:所述s7中,建立实时监测系统,定期检查内部时钟的稳定性,设定稳定性阈值和警报机制,及时发现并响应时钟漂移或异常。

8.根据权利要求1所述的应用于电子雷管的时钟快速校正方法,其特征在于:所述s8中,设计系统能够自动修正时钟或发出警告,确保系统稳定性。

技术总结本发明涉及电子雷管技术领域,具体为一种应用于电子雷管的时钟快速校正方法,包括获取参考时间信号,传输参考时间信号,接收参考时间信号,比较和校正,调整内部时钟,反馈和验证,实时监测,容错机制。本发明中,系统能够自动判断是否进行过时钟校正,减轻了操作人员的负担,提高了系统的自动化程度,检测高电平可以防止误判和不正确的时钟信号输入,减少系统异常的可能性,系统自动修正时钟或发出警告,有助于在出现异常情况下及时采取措施,增强了系统的稳定性和可靠性,实时监测系统可以定期检查内部时钟的稳定性,设定稳定性阈值和警报机制,可以及时发现和响应时钟漂移或异常,提高了系统的可靠性。技术研发人员:吴志永,何锦,李叶森,韩世全,汤炜受保护的技术使用者:杭州晋旗电子科技有限公司技术研发日:技术公布日:2024/5/27本文地址:https://www.jishuxx.com/zhuanli/20240730/153376.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。