DVB-S2标准下的LDPC并行编码器结构及编码方法

- 国知局

- 2024-08-02 15:00:50

本发明属于无线通信系统的信道编码,特别涉及一种ldpc并行编码器,可用于卫星通信。

背景技术:

1、卫星通信具有传输容量大、灵活性高、传输业务多样的优点,广泛应用在应急通信、导航定位、指控侦测、航空航天等领域。为实现高速且可靠的信息传输,如何在空、天、地等差异极大的信道环境中保持更低的传输时延和更好的传输性能,以及如何做到统一的多址和编码设计就显得尤为重要。为此,各个国家和地区陆续提出用于处理信息传输和错误恢复的协议以提高卫星通信服务质量。

2、在2004年6月,数字电视广播dvb组织发布了dvb-s2标准。相比于第一代的dvb-s标准,dvb-s2标准在数据传输性能、服务支撑能力等方面都有明显改善。其应用了纠错能力更强的低密度奇偶校验码ldpc和bch码级联来实现纠错编码,有效地降低了系统解调门限;dvb-s2系统相较于dvb-s系统,其转发器的容量提高了接近一半。此后,低轨卫星通信大多数利用欧盟etsi的第二代数字卫星电视广播标准dvb-s2/dvb-s2x并做出改良。

3、dvb-s2标准定义了普通帧ldpc码和短帧ldpc码。普通帧对应ldpc码码长为64800,码率共11种,码率范围为1/4~9/10;短帧对应ldpc码码长为16200,码率共10种,码率范围为1/4~8/9)。在dvb-s2标准下的ldpc码是一种非规则重复累积码ira,其编码基于校验矩阵h进行。对于码长为n,信息比特长度为k的ldpc码,其校验矩阵如下。

4、

5、其中,h1是m×k阶的稀疏矩阵,h2是m×m阶的下双对角矩阵,m=n–k是校验比特长度。

6、虽然标准中定义的h1初始矩阵不具有准循环的结构,但是其具有分组构造的特点,按照每360列构成一个分组。在dvb-s2标准中只定义了每个分组中首列元素1的行地址,作为地址表在附录中给出。地址表中的每行元素是h1矩阵对应分组的首列非零元素的行地址信息,被称为初始地址;分组中剩余列的行地址则依据不同码率所决定的不同偏移值q来逐列跳转获得。

7、etsi的协议a83-1中定义了行地址的跳转规则:设分组中首列非零元素的行地址向量为a,第j列非零元素的行地址向量为aj,分别表示为:

8、a={a0,a1,...,ai,...,adv-1},aj={a(j,0),a(j,1),...,a(j,i),...,a(j,dv-1)}

9、其中:ai是首列第i个非零元素的行地址,i=0,1,…,dv-1,dv为行地址数;a(j,i)={ai+(j-1)*q}mod(n-k)是当前分组中第j列的行地址,j=2,3……360。

10、遍历地址表每行初始地址,最终获得h1矩阵,再将h1矩阵与m×m阶的下双对角矩阵拼接获得校验矩阵h。

11、dvb-s2标准的ldpc码采用校验矩阵h进行编码,其编码原理如下:

12、设编码码字为c=[u,p],其中u=(u0,u1,...,ug,...,uk-1)为信息比特向量,ug为信息比特,g=0,1…,k-1;p=(p0,p1,...,pl,...,pm-1)为校验比特向量,pl为校验比特,l=0,1,…,m-1,对ldpc编码就是求解编码方程hct=0的解,即将编码方程hct=0化为如下的m个等式:

13、

14、为了实现流水操作,定义中间值变量zl,g:

15、zl,g=zl,g-1+hl,gug

16、令中间值变量zl,g初始值为0,利用信息比特ug不断迭代更新zl,g直至得到z0,k-1,z1,k-1,…,zm-1,k-1,最后将z0,k-1,z1,k-1,…,zm-1,k-1代入编码方程中,得到如下简化的编码方程:

17、

18、利用化简的编码方程计算校验比特向量p=(p0,p1,...,pg,...,pm-1):首先令p0的值等于z0,k-1,p1等于z1,k-1与p0异或后的值,再由此后向迭代利用z2,k-1,z3,k-1,…,zm-1,k-1得到p2,p3,...,pm-1。

19、将信息序列u与校验序列p合并,最终得到编码后的码字c=[u0,u1,...,uk-1,p0,p1,...,pm-1]。

20、申请号cn201010125182.7的专利文献中公开了一种ldpc串行编码器,该编码器的工作原理如下:编码器将中间值变量存储在双口ram中,当编码使能为1,编码器内的校验地址计算单元产生校验地址,作为双口ram的读地址,读出对应的中间值变量,再将中间值变量与输入的信息比特进行异或后写回原来的位置;当中间值变量更新完毕后,进行后向迭代更新校验比特,最后输出编码后码字。这种串行编码器虽然简单,能够兼容多种码率的编码需求,但数据吞吐率较低,难以满足现代卫星通讯中飞速增长的对于信息传输速率的需要。

21、申请号cn202110579879的专利文献中公开了一种ldpc并行编码器,该编码器使用寄存器来存储中间值变量,当信息比特并行输入时,可以灵活的读取寄存器中的中间值变量并进行并行更新,更新完毕后再将中间值变量并行后向迭代得到校验比特,最后输出编码后码字。该方案存在如下几个方面的问题:1)在利用编码方程计算校验比特向量时,需要进行大量的与运算与异或运算,这将极大的消耗fpga逻辑资源;同时由于门电路之间存在延时,过多的使用异或门将导致触发器存在不稳定状态,严重影响编码系统性能。2)利用寄存器存储中间值变量会使得fpga布线过于复杂,降低了编码器的数据吞吐率,且由于没有利用到fpga内部丰富的内存资源,未能做到资源均衡。

技术实现思路

1、本发明的目的是在于克服以往上述并行编码器架构的不足,提出一种dvb-s2标准的ldpc并行编码器结构及编码方法,以降低资源消耗,提高吞吐量,且能兼容dvb-s2标准下ldpc码的全部码率。

2、实现本发明目的的技术思路是:通过将中间值变量以8位并行结构存储在双口ram中,同时对各种参数的计算流程进行优化,实现对资源消耗的降低的资源的均衡分配;通过将中间值地址的计算流程进行简化,减少逻辑门的级联与路径延迟,实现对编码器数据吞吐量及最大工作频率的提高;通过对编码器各个单元按照码率进行片选,实现内部功能模块的复用及所有码率的兼容。

3、根据上述思路,本发明的技术方案如下:

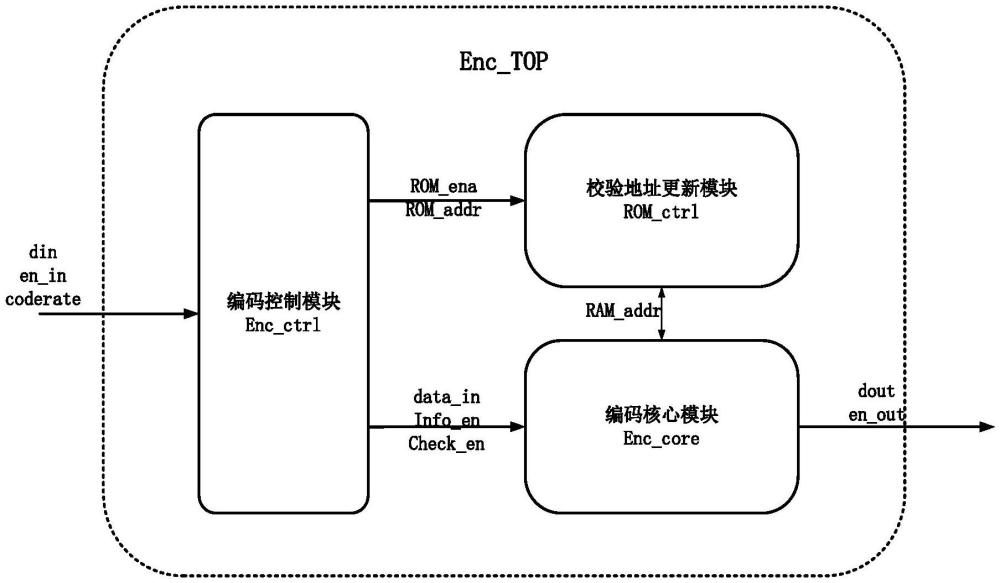

4、1.一种dvb-s2标准下的ldpc并行编码器,包括:编码控制模块,校验地址更新模块,编码核心模块,其特征在于:

5、所述编码控制模块,其包括编码状态单元,rom地址更新单元和延时单元,用于对编码的各个流程进行控制,以产生rom读地址信号,ram使能信号作为控制信号,并输出到其余两个模块,

6、所述校验地址更新模块,其包括地址表rom存储单元,地址表宽度切换单元和地址更新单元,用于通过输入码率和编码控制模块输出的rom读地址信号读取对应的校验矩阵压缩信息表,并由该表计算产生中间值地址与标志位信号输入给编码核心模块;

7、所述编码核心模块,其包括中间变量存储计算单元、校验比特更新单元和编码码字输出单元,用于根据从其他两个模块接收的中间值地址和ram使能信号完成关键的中间值变量的迭代计算,逐步恢复出完整的校验比特向量,同时进行信息比特和校验比特的并行输出。

8、进一步,所述编码状态单元,其输入为码率信号和输入使能信号,输出为信息有效位信号和校验有效位信号;该编码状态单元包括一个计数器和一块rom,rom中存储有每种码率对应的信息序列长度k与编码码字长度n,通过将计数器数值与rom输出数据进行比较,确定有效位信号的输出;

9、进一步,所述rom地址更新单元,其输入为输入使能信号,输出为rom使能信号、rom读地址信号和首地址标志位信号;该rom地址更新单元由一个计数器构成,根据计数器数值控制输出信号;

10、进一步,所述延时单元,其输入为使能信号和信息比特,输出为ram读写使能信号;该延时单元包括六组触发器,每组触发器含有8个触发器,用于当输入使能有效时,将8位信息比特延时6个时钟单位后输出到编码核心模块。

11、进一步,所述地址表rom存储单元,其输入为码率信号、rom使能信号和rom读地址信号,输出为初始地址信号;该地址表rom存储单元包括21块rom,每块rom用来存储dvb-s2标准中对应的地址表信息,并在输入信号控制下将地址表的初始地址输出到地址更新单元;

12、进一步,所述地址表宽度切换单元,用于在地址表rom中读取出的初始地址数量发生变化时,将标志位信号变为高电平,其输入为码率信号和rom读地址信号,输出为标志位信号;

13、进一步,所述地址更新单元,其输入为码率信号、初始地址信号和首地址标志位信号,输出为8路中间值地址向量;该地址更新单元包含8组缓存单元和两块rom;每组缓存单元含有13块缓冲寄存器,每块rom中分别存储码率信号对应的比较值和累加值,该地址更新单元根据比较值与缓冲寄存器输出的比较结果计算每个信息比特的中间值地址,并按顺序拼接得到8路中间值地址向量。

14、进一步,所述中间值变量存储计算单元,其输入为码率信号、标志位信号、ram读写使能信号和中间值地址向量,输出为8位中间值变量信号,该中间值变量存储计算单元包括8组双口ram,每组ram包含13块双口ram,每块双口ram的宽度为8bit,深度为6075,用来存储和更新中间值变量,并将更新后的中间值变量逐行读出,输出到校验比特更新单元;

15、进一步,所述校验比特更新单元,用于通过中间值变量迭代更新校验比特与校验保留值,同时输出校验比特,其输入为中间值变量信号,输出为8位校验比特信号;

16、进一步,所述编码码字输出单元,用于在有效位信号的控制下编码码字的输出,其输入为信息有效位、校验有效位、ram读写使能信号和校验比特信号,输出为8位编码输出信号。

17、2.一种利用dvb-s2标准下的ldpc并行编码器进行编码的方法,其特征在于,包括如下步骤:

18、1)编码控制模块通过输入使能和码率等信号产生rom读地址、rom使能与首标志位信号输出到校验地址更新模块,控制中间值地址的计算;同时产生ram读写使能以及有效位信号输出到编码核心模块,控制中间值变量的更新和编码码字的生成;

19、2)校验地址更新模块在码率信号以及编码控制模块控制下,选择地址表rom并读取初始地址信息,再根据初始地址并行计算得到8路中间值地址向量;同时,校验地址更新模块根据地址表内初始地址的分布情况,在码率信号与rom读地址信号的控制下产生标志位信号,并将该信号与中间值地址向量共同输出到编码核心模块;

20、3)编码核心模块在码率信号与标志位信号控制下选通部分双口ram;

21、4)编码核心模块利用选通的双口ram进行中间值变量与校验比特的迭代更新:

22、当信息有效位为1、校验有效位为0时,将ram读写使能信号作为每组ram的读写使能,中间值地址信息作为每组ram的读写地址和索引,更新中间值变量信息;

23、当信息有效位为0、校验有效位为1,将每块ram中的数据逐行读出,恢复中间值变量,并通过后向迭代得到并行8位校验比特信息。

24、本发明与现有技术相比,具有如下优点:

25、1.结构简单,内存资源利用少

26、传统编码器多采用串行结构存储中间值变量,为实现中间值变量的并行输出,需要额外消耗8倍的内存资源,且结构复杂。而本发明以8位并行结构将中间值变量顺序存储在双口ram中,当中间值变量更新完成后,再并行输出中间值变量以进行校验比特的迭代更新,不仅结构简单,而且节省了内存资源,能实现资源的平衡分配。

27、2.额外开销低

28、本发明由于对中间值地址更新公式进行了优化,在更新公式中的取余运算中减少了一个加法器的使用,相比现有技术降低了运算过程中的额外开销,同时减少模块间的级联,提高了工作时钟与系统吞吐率。

29、3.本发明较传统编码器由于在结构和流程上进行了优化,因此可在满足足够编码速率的情况下,能兼容dvb-s2标准下ldpc码的全部码率,实现全码率兼容。

本文地址:https://www.jishuxx.com/zhuanli/20240801/244650.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。