一种低温共烧叠层压电元件的电极结构和制造工艺的制作方法

- 国知局

- 2024-08-02 15:17:20

本发明涉及压电元件,具体是一种低温共烧叠层压电元件的电极结构和制造工艺。

背景技术:

1、低温共烧压电陶瓷内电极的连接基本两种方式:一种是打孔连接,一种是在一个端面涂覆外电极。第一种对制作工艺要求较高,需要精密的设备实现。第二种需要在一个端面同时存在三个电极,如果压电陶瓷尺寸较小,这种实现方式的难度会大大增加。

2、现有的技术问题包括:

3、1、设备要求高,精密设备的成本较高,对操作人员也提出更高的要求,人工成本增加;

4、2、受到内电极结构的影响,工艺控制要求较严格;

5、3、较小尺寸产品由于内电极结构复杂,合格率受到限制。

6、因此,我们提出了一种低温共烧叠层压电元件的电极结构和制造工艺来解决上述所提到的问题。

技术实现思路

1、本发明的目的在于提供一种低温共烧叠层压电元件的电极结构和制造工艺,以解决上述背景技术中提出的问题。

2、为实现上述目的,本发明提供如下技术方案:

3、一种低温共烧叠层压电元件的电极结构,其特征在于,包括第一压电陶瓷片-a、第二压电陶瓷片-b、第三压电陶瓷片-c和第四压电陶瓷片-d,电极结构由多个所述第一压电陶瓷片-a、第二压电陶瓷片-b、第三压电陶瓷片-c和第四压电陶瓷片-d构成叠层结构,所述第一压电陶瓷片-a、第二压电陶瓷片-b、第三压电陶瓷片-c和第四压电陶瓷片-d上均设置有一组定位r角,所述第二压电陶瓷片-b、第三压电陶瓷片-c和第四压电陶瓷片-d上设置有表面印刷银层内电极;

4、所述第二压电陶瓷片-b、第三压电陶瓷片-c和第四压电陶瓷片-d上均设置有多组纵向定位与裁切位、横向定位与裁切位,沿着所述纵向定位与裁切位、横向定位与裁切位形成切割刀路,通过热切机沿着切割刀路切割形成电极切割品,电极切割品的表面均设置有表面印银层面电极与侧边印银层翻边电极,且所述电极切割品一侧还设置有低温银浆层。

5、一种低温共烧叠层压电元件的制造工艺,包括以下步骤:

6、步骤一:流延成型;步骤二:裁片;步骤三:叠压;步骤四:一次切片;步骤五:印刷内电极;步骤六:叠层;步骤七:温等静压;步骤八:印纵向定位与裁切位和横向定位与裁切位;步骤九:二次切片;步骤十:上隔离粉;步骤十一:排胶;步骤十二:烧成;步骤十三:磨边;步骤十四:印表面印银层面电极;步骤十五:印侧面和端面的侧边印银层翻边电极;步骤十六:烧银;步骤十七:极化;步骤十八:涂低温银浆;步骤十九:测试。

7、作为本发明进一步的方案:所述步骤一流延成型中,成型后膜带的厚度为0.035mm-0.038mm,膜带底部附一层pet膜;所述步骤二裁片中,采用的设备为裁片机,裁片的尺寸为220mm x 220mm;所述步骤三叠压中,采用的是两张膜带叠片,工作参数为温等静压60℃,、60mpa、保压300s。

8、作为本发明进一步的方案:所述步骤四一次切片中,采用的是激光切割机,切片尺寸为200mm x 200mm,膜片切割后一个r角三个直角;所述步骤五印刷内电极中,撕掉一面pet膜后在膜带上印刷表面印刷银层内电极,电极图有第二压电陶瓷片-b、第三压电陶瓷片-c和第四压电陶瓷片-d三种,采用的银浆为耐温900℃的银浆料或者采用钯含量为5%的银钯浆料。

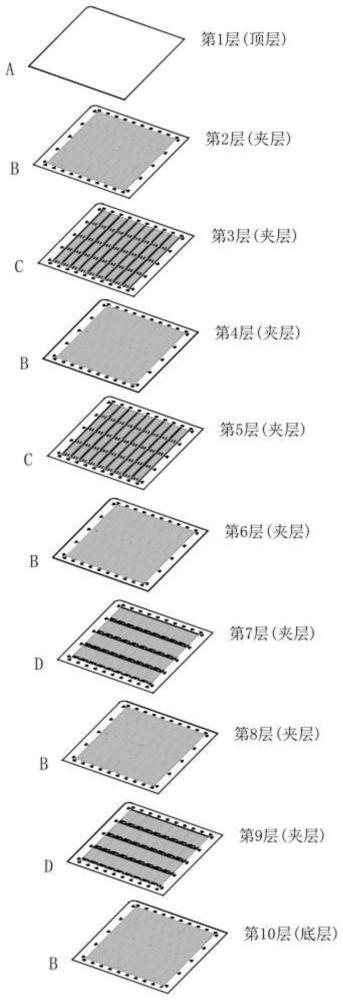

9、作为本发明进一步的方案:所述步骤六叠层中,从下往上膜带的叠放顺序依次是b、d、b、d、b、c、b、c、b、a,第一压电陶瓷片-a正面做标记,所有膜带电极面朝上,按照r角对齐电极图形方向;撕掉膜带底部pet膜,每叠加一层膜带做一次热压,热压参数为62℃、5t、1min;重复以上叠层和热压操作。

10、作为本发明进一步的方案:所述步骤七温等静压中,叠层热压好的膜带装袋密封,进行温等静压,温等静压参数为60℃,60mpa,300s;所述步骤八印纵向定位与裁切位和横向定位与裁切位中,膜块正面印纵向定位与裁切位、横向定位与裁切位,形成切割刀路。

11、作为本发明进一步的方案:所述步骤九二次切片中,在热切机上按照切割刀路切片;所述步骤十上隔离粉中,用毛刷给生坯片上氧化锆粉,并排片与加压块,排片中采用5片膜带为一叠,加压块中压块尺寸大于生坯片的尺寸。

12、作为本发明进一步的方案:所述步骤十一排胶中,为车间排胶窑排胶;所述步骤十二烧成中,按低温料烧成工艺执行;所述步骤十三磨边中,长宽四边磨边,公差为±0.05mm;所述步骤十四印表面印银层面电极中,瓷片正面印表面印银层面电极,烘干;银浆采用银含量为60%的银浆料,丝网印刷网目为230目。

13、作为本发明进一步的方案:所述步骤十五印侧面和端面的侧边印银层翻边电极中,印刷侧边印银层翻边电极后进行烘干,银浆采用银含量为60%的银浆料,丝网印刷网目为230目;步骤十六烧银中,采用车间烧银窑正常烧银。

14、作为本发明再进一步的方案:所述步骤十七极化中,共进行两次极化,端面极化一次,侧面极化一次,端面极化为①负②正,侧面极化为①正③负,极化电压为80v;所述步骤十八涂低温银浆中,形成低温银浆层,其低温银浆涂覆②、③电极角,连接②、③电极,涂覆低温银浆后,在120℃烘箱中烘干30min。

15、与现有技术相比,本发明的有益效果是:

16、该低温共烧叠层压电元件的电极结构和制造工艺,采用了低温共烧压电陶瓷材料,设计了新的内电极结构,使叠层工艺更简单;制造工艺设备简化,降低加工成本;工艺过程易实施,合格率提高。

技术特征:1.一种低温共烧叠层压电元件的电极结构,其特征在于,包括第一压电陶瓷片-a、第二压电陶瓷片-b、第三压电陶瓷片-c和第四压电陶瓷片-d,电极结构由多个所述第一压电陶瓷片-a、第二压电陶瓷片-b、第三压电陶瓷片-c和第四压电陶瓷片-d构成叠层结构,所述第一压电陶瓷片-a、第二压电陶瓷片-b、第三压电陶瓷片-c和第四压电陶瓷片-d上均设置有一组定位r角(4),所述第二压电陶瓷片-b、第三压电陶瓷片-c和第四压电陶瓷片-d上设置有表面印刷银层内电极(7);

2.根据权利要求1所述的一种低温共烧叠层压电元件的制造工艺,其特征在于,包括以下步骤:

3.根据权利要求2所述的一种低温共烧叠层压电元件的制造工艺,其特征在于,所述步骤一流延成型中,成型后膜带的厚度为0.035mm-0.038mm,膜带底部附一层pet膜;所述步骤二裁片中,采用的设备为裁片机,裁片的尺寸为220mm x 220mm;所述步骤三叠压中,采用的是两张膜带叠片,工作参数为温等静压60℃,、60mpa、保压300s。

4.根据权利要求2所述的一种低温共烧叠层压电元件的制造工艺,其特征在于,所述步骤四一次切片中,采用的是激光切割机,切片尺寸为200mm x 200mm,膜片切割后一个r角三个直角;所述步骤五印刷内电极中,撕掉一面pet膜后在膜带上印刷表面印刷银层内电极(7),电极图有第二压电陶瓷片-b、第三压电陶瓷片-c和第四压电陶瓷片-d三种,采用的银浆为耐温900℃的银浆料或者采用钯含量为5%的银钯浆料。

5.根据权利要求2所述的一种低温共烧叠层压电元件的制造工艺,其特征在于,所述步骤六叠层中,从下往上膜带的叠放顺序依次是b、d、b、d、b、c、b、c、b、a,第一压电陶瓷片-a正面做标记,所有膜带电极面朝上,按照r角对齐电极图形方向;撕掉膜带底部pet膜,每叠加一层膜带做一次热压,热压参数为62℃、5t、1min;重复以上叠层和热压操作。

6.根据权利要求2所述的一种低温共烧叠层压电元件的制造工艺,其特征在于,所述步骤七温等静压中,叠层热压好的膜带装袋密封,进行温等静压,温等静压参数为60℃,60mpa,300s;所述步骤八印纵向定位与裁切位(5)和横向定位与裁切位(6)中,膜块正面印纵向定位与裁切位(5)、横向定位与裁切位(6),形成切割刀路(8)。

7.根据权利要求2所述的一种低温共烧叠层压电元件的制造工艺,其特征在于,所述步骤九二次切片中,在热切机上按照切割刀路(8)切片;所述步骤十上隔离粉中,用毛刷给生坯片上氧化锆粉,并排片与加压块,排片中采用5片膜带为一叠,加压块中压块尺寸大于生坯片的尺寸。

8.根据权利要求2所述的一种低温共烧叠层压电元件的制造工艺,其特征在于,所述步骤十一排胶中,为车间排胶窑排胶;所述步骤十二烧成中,按低温料烧成工艺执行;所述步骤十三磨边中,长宽四边磨边,公差为±0.05mm;所述步骤十四印表面印银层面电极中,瓷片正面印表面印银层面电极(1),烘干;银浆采用银含量为60%的银浆料,丝网印刷网目为230目。

9.根据权利要求2所述的一种低温共烧叠层压电元件的制造工艺,其特征在于,所述步骤十五印侧面和端面的侧边印银层翻边电极(2)中,印刷侧边印银层翻边电极(2)后进行烘干,银浆采用银含量为60%的银浆料,丝网印刷网目为230目;步骤十六烧银中,采用车间烧银窑正常烧银。

10.根据权利要求2所述的一种低温共烧叠层压电元件的制造工艺,其特征在于,所述步骤十七极化中,共进行两次极化,端面极化一次,侧面极化一次,端面极化为①负②正,侧面极化为①正③负,极化电压为80v;所述步骤十八涂低温银浆中,形成低温银浆层(3),其低温银浆涂覆②、③电极角,连接②、③电极,涂覆低温银浆后,在120℃烘箱中烘干30min。

技术总结本发明公开了一种低温共烧叠层压电元件的电极结构和制造工艺,包括第一压电陶瓷片‑A、第二压电陶瓷片‑B、第三压电陶瓷片‑C和第四压电陶瓷片‑D,电极结构由多个所述第一压电陶瓷片‑A、第二压电陶瓷片‑B、第三压电陶瓷片‑C和第四压电陶瓷片‑D构成叠层结构,所述第一压电陶瓷片‑A、第二压电陶瓷片‑B、第三压电陶瓷片‑C和第四压电陶瓷片‑D上均设置有一组定位R角,所述第二压电陶瓷片‑B、第三压电陶瓷片‑C和第四压电陶瓷片‑D上设置有表面印刷银层内电极;所述第二压电陶瓷片‑B、第三压电陶瓷片‑C和第四压电陶瓷片‑D上均设置有多组纵向定位与裁切位、横向定位与裁切位;采用了低温共烧压电陶瓷材料,设计了新的内电极结构,使叠层工艺更简单。技术研发人员:朱惠祥,李枫,戴开彬,陈桢受保护的技术使用者:广州凯立达电子股份有限公司技术研发日:技术公布日:2024/7/18本文地址:https://www.jishuxx.com/zhuanli/20240801/245542.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表